IIC

Inter-Intergrated Circuit(内部集成电路)

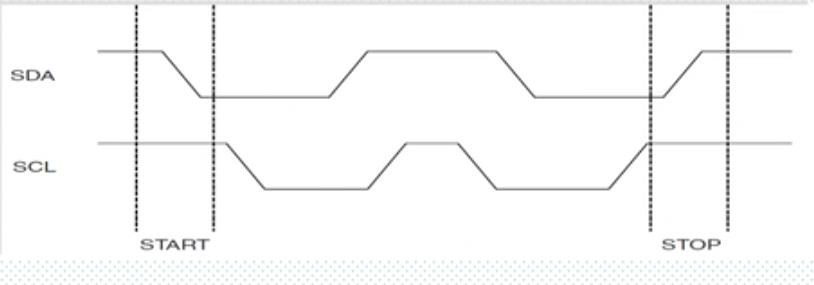

由数据线SDA和时钟线SCL构成串行总线,可发送接收数据。

SCL:通讯时起到控制作用。

SDA:进行位传输数据。

软件IIC:通过单片机的I/O口模拟,使用软件控制I/O口模拟通信波形,软件模拟寄存器的工作方式。

硬件IIC:通过IIC驱动电路,硬件直接调用寄存器配置。

半双工通信方式

IIC通信协议

主要有开始、结束、发送、响应、接收这几个过程。

//产生IIC起始信号

//1.设置SDA输出

//2.先拉高SDA,再拉高SCL,空闲状态

//3.拉低SDA

//4.准备接收数据

void IIC_Start(void)

{

SDA_OUT(); //sda线输出

IIC_SDA=1;

IIC_SCL=1;

delay_us(4);

IIC_SDA=0;//START:when CLK is high,DATA change form high to low

delay_us(4);

IIC_SCL=0;//钳住I2C总线,准备发送或接收数据

}

//产生IIC停止信号

//1.设置SDA输出

//2.先拉低SDA,再拉低SCL

//3.拉高SCL

//4.拉高SDA

//5.停止接收数据

void IIC_Stop(void)

{

SDA_OUT();//sda线输出

IIC_SCL=0;

IIC_SDA=0;//STOP:when CLK is high DATA change form low to high

delay_us(4);

IIC_SCL=1;

IIC_SDA=1;//发送I2C总线结束信号

delay_us(4);

}

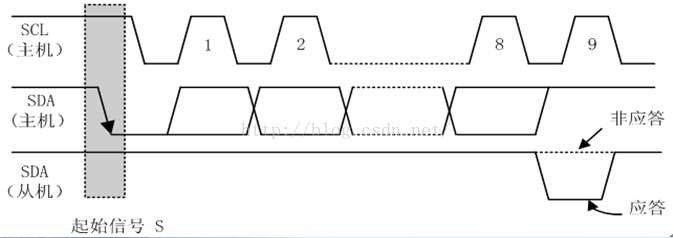

应答信号

每次主机向从机发送完一个字节的数据,主机需要等待从机给一个应答信号,以确定从机是否接收了数据,从机所需的时钟是主机提供的,应答在每完成8个数据位之后的时钟周期,低电平0为应答,1表示非应答。

应答程序:

//产生ACK应答

//这里就很清楚了,产生应答:SCL在SDA一直为低电平期间完成低高电平转换

void IIC_Ack(void)

{

IIC_SCL=0;

SDA_OUT();

IIC_SDA=0;

delay_us(2);

IIC_SCL=1;

delay_us(2);

IIC_SCL=0;

}

//不产生ACK应答

//这里就很清楚了,不产生应答:SCL在SDA一直为高电平期间完成低高电平转换

void IIC_NAck(void)

{

IIC_SCL=0;

SDA_OUT();

IIC_SDA=1;

delay_us(2);

IIC_SCL=1;

delay_us(2);

IIC_SCL=0;

}

发送数据:

void IIC_Send_Byte(u8 txd)

{

u8 t;

SDA_OUT();

IIC_SCL=0;//拉低时钟开始数据传输

for(t=0;t<8;t++)

{

//IIC_SDA=(txd&0x80)>>7;

//获取数据的最高位,然后左移7位

//如果某位为1,则SDA为1,否则相反

if((txd&0x80)>>7)

IIC_SDA=1;

else

IIC_SDA=0;

txd<<=1;

delay_us(2); //对TEA5767这三个延时都是必须的

IIC_SCL=1;

delay_us(2);

IIC_SCL=0;

delay_us(2);

}

}

单片机发送完一个字节后面必须跟一个等外应答函数:

思路:先让SDA=1,再判断在一定时间内SDA是否变为0,从而识别出外设有没有发送应答信号。

u8 IIC_Wait_Ack(void)

{

u8 ucErrTime=0;

SDA_IN(); //SDA设置为输入

IIC_SDA=1;delay_us(1);

IIC_SCL=1;delay_us(1);

while(READ_SDA)

{

ucErrTime++;

if(ucErrTime>250)

{

IIC_Stop();

return 1;

}

}

IIC_SCL=0;//时钟输出0

return 0;

}

接收数据

发送数据通过位发送,接收数据通过位接收,最后返回应答信号:

u8 IIC_Read_Byte(unsigned char ack)

{

unsigned char i,receive=0;

SDA_IN();//SDA设置为输入

for(i=0;i<8;i++ )

{

IIC_SCL=0;

delay_us(2);

IIC_SCL=1;

receive<<=1;

if(READ_SDA)receive++;

delay_us(1);

}

if (!ack)

IIC_NAck();//发送nACK

else

IIC_Ack(); //发送ACK

return receive;

}

SPI

Serial Peripheral interface(串行外设接口)

- SCLK: Serial Clock (output from master);串行时钟(主机输出)

- MOSI; SIMO: Master Output, Slave Input(output from master);主输出,从输入(从主输出)

- MISO; SOMI: Master Input, Slave Output(output from slave);主机输入,从机输出(从机输出)

- SS: Slave Select (active low, outputfrom master).从机选择(低电平有效,主机输出)

SPI是一种高速的,全双工,同步的通信总线,并且在芯片的管脚上只占用四根线

时钟极性CPOL是用来配置SCLK的电平出于哪种状态时是空闲态或者有效态,时钟相位CPHA是用来配置数据采样是在第几个边沿:

- CPOL=0,表示当SCLK=0时处于空闲态,所以有效状态就是SCLK处于高电平时;

- CPOL=1,表示当SCLK=1时处于空闲态,所以有效状态就是SCLK处于低电平时;

- CPHA=0,表示数据采样是在第1个边沿,数据发送在第2个边沿;

- CPHA=1,表示数据采样是在第2个边沿,数据发送在第1个边沿。

在SCLK的控制下,数据按照**从高位到低位的方式依次移出主机寄存器和从机寄存器,并且依次移入从机寄存器和主机寄存器。**当寄存器中的内容全部移出时,相当于完成了两个寄存器内容的交换。

698

698

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?