Vivado仿真时出现无法编译仿真问题

项目场景、问题描述:

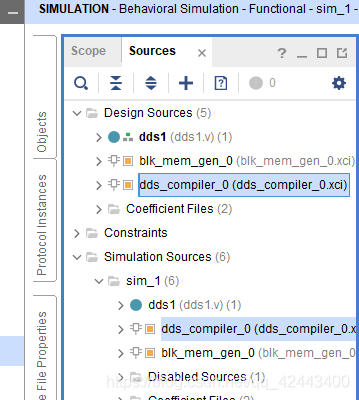

用官方的IP库生成参数化的IP后仿真,出现问题

ERROR: [VRFC 10-2987] ‘********某某某’ is not compiled in library ‘xil_defaultlib’

ERROR: [VRFC 10-3782] unit ‘tb’ ignored due to previous errors

解决方案:

方法1(但对我没用):

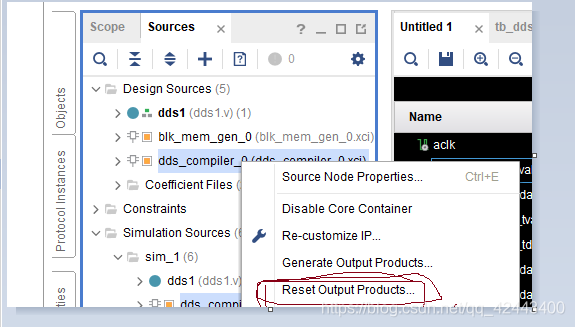

方法2(我的方法):

Reset output products就好了,之前试了N多种方法,包括update,重置仿真,重新打开项目,都没有用。

希望能帮助到更多的人!

在使用Vivado进行仿真时遇到无法编译官方IP的问题,报错提示'********某某某'未在'xil_defaultlib'库中编译。尝试了多种方法如更新、重置仿真等均未成功。最终通过Reset output products解决了问题,这是一个可能被忽视的解决步骤,对于遇到同样问题的用户可能有所帮助。

在使用Vivado进行仿真时遇到无法编译官方IP的问题,报错提示'********某某某'未在'xil_defaultlib'库中编译。尝试了多种方法如更新、重置仿真等均未成功。最终通过Reset output products解决了问题,这是一个可能被忽视的解决步骤,对于遇到同样问题的用户可能有所帮助。

5513

5513

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?