数字系统中亚稳态

亚稳态定义:

当数据的输入不能满足触发器的建立与保持时间时,系统产生亚稳态状态。如何理解触发器的建立与保持时间?

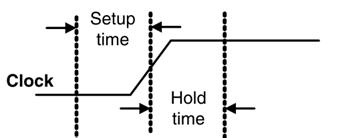

上图所示为触发器的建立与保持时间示意图,其中建立时间指的是,在时钟的上升沿到来之间,数据需要保持稳定的最小时间,保持时间指的是在时钟的上升沿来之后,输入数据需要保持不变的时间。为什么会出现建立时间与保持时间这个概念呢?也就是说为什么它会存在这么一个时间?这个时间与什么相关呢?

触发器的组成是由两个RS锁存器组成,其中第一个锁存器的输出作为第二个锁存器的输入信号,两个的时钟为相反时钟信号,当时钟信号为低电平时,前一个锁存器导通,当时钟信号变为高电平时,前一个锁存器数据保持,后一个锁存器打开。因此,建立时间指得就是在时钟的上升沿到来之前,前一个锁存器的数据要保持不变的时间,如果在这个时间数据发生变化的话,第一级的锁存器输出信号将出现混乱,不是我们想要输入的一个信号,经过后一级传递,输出即为一个亚稳态;保持时间就是时钟上升沿到来之后,第一级锁存器的输入信号保持不变的时间。触发器的建立与保持时间是触发器的一种性质。

在实际应用中,以下条件下可能产生亚稳态:

1.输入信号为异步信号

2.时钟的抖动和偏移超过容许的极限

3.数据信号工作在两个不同的频率下

4.数据信号工作在相同的频率下,但工作在不同的相位

5.组合逻辑电路延时比较长,导致信号变化在时钟的上升沿上

如何解决实际问题中的亚稳态问题,以下几点有助于减少系统中产生亚稳态:

1.尽量在电路中采用同步时序电路

2.使用更快的触发器,即减小触发器的建立时间与保持时间

3.在异步电路中,对输入的信号采用两级D触发器进行信号的同步化

4.降低数据的采样率

5.相同频率下的不同模块,一个模块产生数据,另一个模块需要采集 前一个模块数据时,产生数据模块在时钟的上升沿产生,接收数据模块在时钟的下降沿接收数据,这样能够避开亚稳态的产生(两个模块的时钟抖动和偏移量都在有限的范围下)。

462

462

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?