DesignWare低功耗流水线浮点乘法器仿真

DC中的DesignWare提供了相应的IP,进行仿真需要使用以下的文件:DW_fp_mult.v,DW_lp_pipe_mgr.v,DW_lp_piped_fp_mult.v,DW_lp_piped_fp_mult_inst.v,其中DW_lp_piped_fp_mult_inst.v为顶层文件,对其进行仿真需要编写testbench,产生相应的控制信号和数据,接下来将连续对5个数据进行仿真,输入数据的格式均为标准的浮点数表示形式。

testbench编写如下:

`timescale 1ns/1ns

module tb_fp1;

reg clk;

reg rst_n;

reg [31:0] a;

reg [31:0] b;

reg launch;

reg [7:0] launch_id;

reg accept_n;

wire [31:0] z_out;

wire [7:0] status;

wire pipe_full;

wire pipe_ovr;

wire arrive;

wire [7:0] arrive_id;

wire push_out_n;

wire [2:0] pipe_census;

wire [7:0] exp_a;

wire [7:0] exp_b;

wire [7:0] exp_z;

wire [22:0] sig_a;

wire [22:0] sig_b;

wire [22:0] sig_z;

assign exp_a = a[30:23];

assign exp_b = b[30:23];

assign exp_z = z_out[30:23];

assign sig_a = a[22:0];

assign sig_b = b[22:0];

assign sig_z = z_out[22:0];

DW_lp_piped_fp_mult_inst #(

.sig_width (23),

.exp_width (8),

.ieee_compliance (0),

.op_iso_mode (0),

.id_width (8),

.in_reg (1),

.stages (4),

.out_reg (1),

.no_pm (0),

.rst_mode (0)

) DPF_Inst (

.inst_clk (clk),

.inst_rst_n (rst_n),

.inst_a (a),

.inst_b (b),

.inst_rnd (3'b0),

.z_inst (z_out),

.status_inst (status),

.inst_launch (launch),

.inst_launch_id (launch_id),

.pipe_full_inst (pipe_full),

.pipe_ovf_inst (pipe_ovf),

.inst_accept_n (accept_n),

.arrive_inst (arrive),

.arrive_id_inst (arrive_id),

.push_out_n_inst (push_out_n),

.pipe_census_inst (pipe_census)

);

initial begin

clk = 0;

rst_n = 0;

#40 rst_n = 1;

end

always #20 clk = ~clk;

reg [3:0] count;

initial begin

a = 32'd0;

b = 32'd0;

launch = 0;

launch_id = 0;

accept_n = 1;

count = 0;

repeat(8)@(posedge clk);

a <= 32'h40000000;

b <= 32'h40400000;

$display("Round %d",count);

$display("the sig and exp of a are: %h, %h", sig_a, exp_a);

$display("the sig and exp of b are: %h, %h", sig_b, exp_b);

$display("#===============================#");

launch <= 1;

count = count + 1;

repeat(1) @(posedge clk);

launch_id <= launch_id + 1;

a <= 32'h40200000;

b <= 32'h40500000;

$display("Round %d",count);

$display("the sig and exp of a are: %h, %h", sig_a, exp_a);

$display("the sig and exp of b are: %h, %h", sig_b, exp_b);

$display("#===============================#");

count = count + 1;

repeat(1) @(posedge clk);

launch_id <= launch_id + 1;

a <= 32'h40700000;

b <= 32'h40800000;

$display("Round %d",count);

$display("the sig and exp of a are: %h, %h", sig_a, exp_a);

$display("the sig and exp of b are: %h, %h", sig_b, exp_b);

$display("#===============================#");

count = count + 1;

repeat(1) @(posedge clk);

launch_id <= launch_id + 1;

a <= 32'h3fddbe4e;

b <= 32'h3f917915;

$display("Round %d",count);

$display("the sig and exp of a are: %h, %h", sig_a, exp_a);

$display("the sig and exp of b are: %h, %h", sig_b, exp_b);

$display("#===============================#");

count = count + 1;

repeat(1) @(posedge clk);

launch_id <= launch_id + 1;

a <= 32'h3f777c44;

b <= 32'hc051cfbf;

$display("Round %d",count);

$display("the sig and exp of a are: %h, %h", sig_a, exp_a);

$display("the sig and exp of b are: %h, %h", sig_b, exp_b);

$display("#===============================#");

count = count + 1;

repeat(1) @(posedge clk);

launch <= 0;

launch_id <= 0;

a <= 0;

b <= 0;

repeat(20) @(posedge clk);

$finish;

end

always @(*) begin

accept_n <= !arrive;

end

always @(posedge clk) begin

if(arrive) begin

$display("the result of z: %h", z_out);

end

end

initial begin

$dumpfile("tb_fp1.vcd");

$dumpvars;

end

endmodule

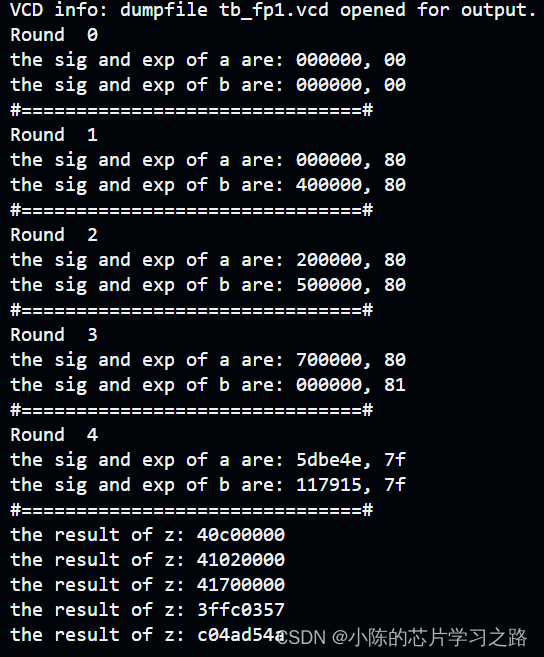

仿真过程如下:

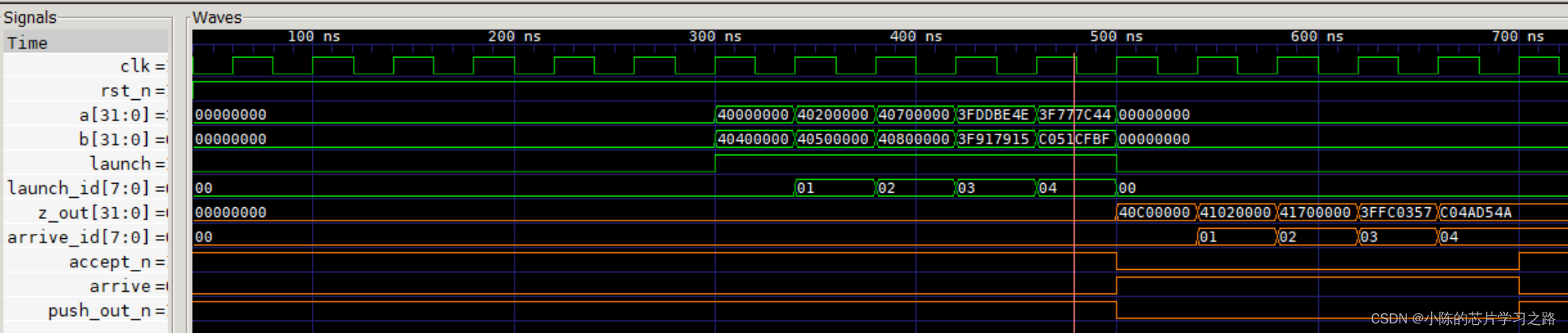

波形图仿真如下:

4033

4033

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?