NICE

1、 介绍

E203核心支持可配置的NICE(nucleus指令协同单元扩展),它可以用来创建用户定义的指令。NICE支持集成定制硬件协同单元,从而提高特定领域的性能,同时降低功耗通过NICE接口协议连接的Co-unit(以下简称NICE-Core)是主E203核之外的一个独立模块。

| Custom | Inst[6:5] | Inst[4:2] | Inst[1:0] |

|---|---|---|---|

| Custom-0 | 00 | 010 | 11 |

| Custom-1 | 01 | 010 | 11 |

| Custom-2 | 10 | 110 | 11 |

| Custom-3 | 11 | 110 | 11 |

2、 NICE的指令格式

为方便用户扩展自定义说明。RISC-V ISA在32位指令中预定义了4组自定义指令类型(custom -0, custom -1, custom -2, custom -3),每一组都有自己的操作码,如下表所示。

在E203内核中,用户可以使用这4个自定义指令组(custom -0, custom -1, custom -2, custom -3)用于NICE扩展,下图显示了NICE指令格式的详细信息,下表显示了NICE指令中各个字段的详细描述。

| Field | Description |

|---|---|

| opcode | Choose one of 4 custom instruction groups (Custom-0, Custom-1, Custom-2, Custom-3) |

| rd | Destination register index |

| xs2 | If this bit is set, source register 2 will be read |

| xs1 | If this bit is set, source register 1 will be read |

| xd | If this bit is set, destination register will be written |

| rs1 | Source register 1 index |

| rs2 | Source register 2 index |

| funct7 | Encode different custom instructions |

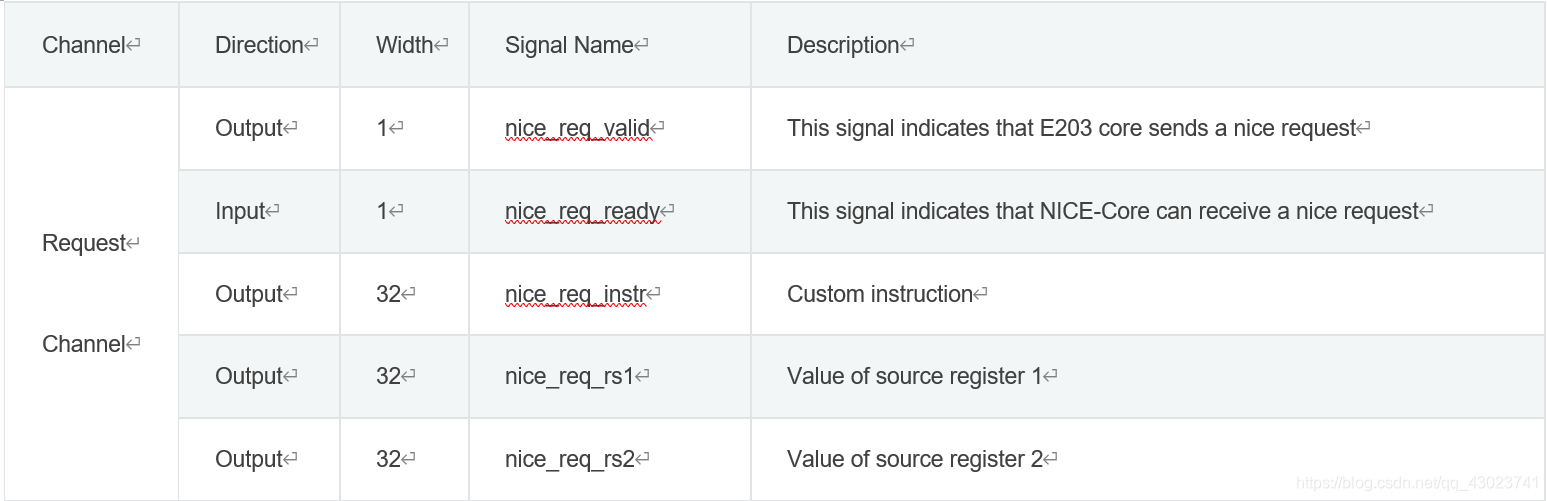

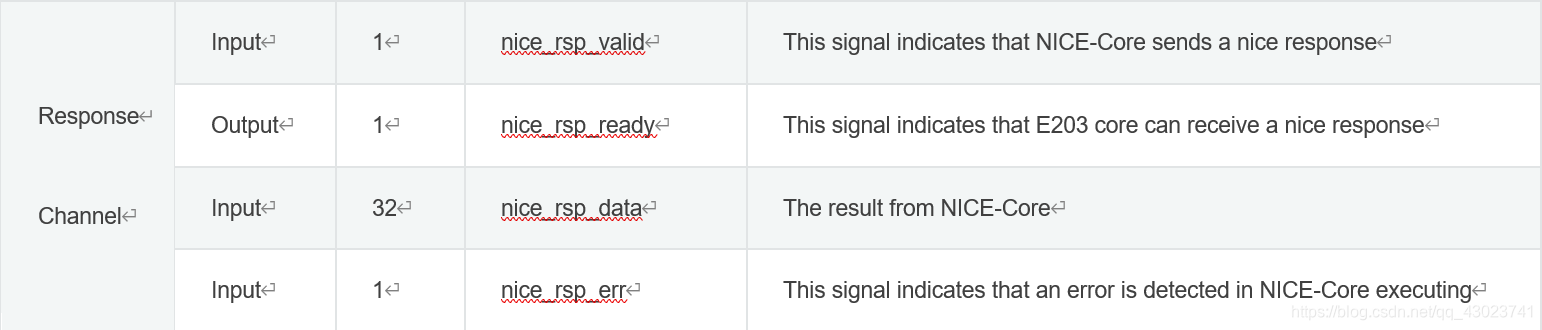

3、 NICE的接口

NICE接口有4个通道,请求通道,响应通道,内存请求通道和内存响应通道。各通道的详细说明如下表所示

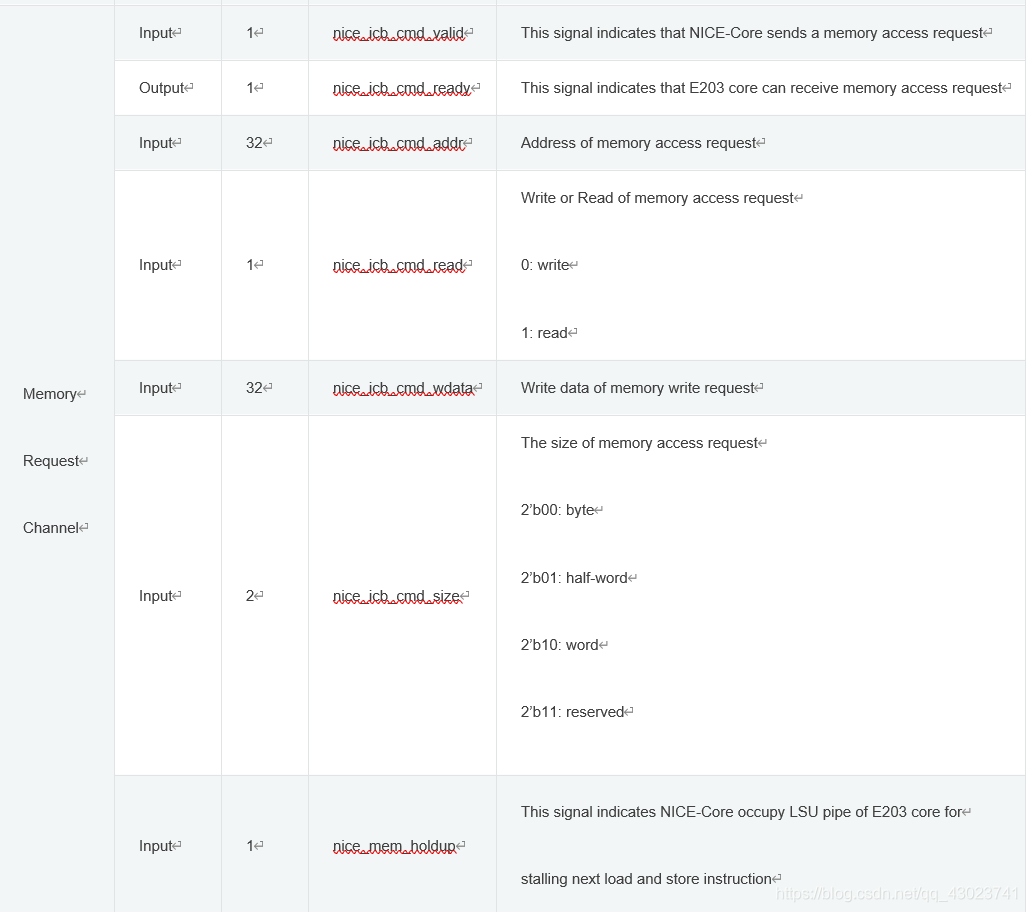

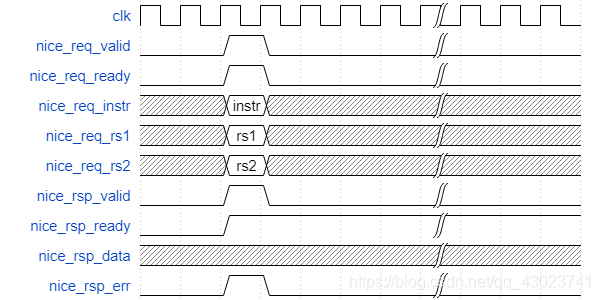

4、 NICE的指令处理

指令通过NICE接口发送给NICE- core前,由E203处理器内核解码,标记为NICE指令,同时根据需要读取NICE接口的rs1和rs2寄存器。如果NICE指令和之前的未完成指令之间存在依赖关系,那么管道将会停止,直到这种依赖关系被消除。由于这种机制,NICE指令的行为就像来自E203处理器核心的一般指令一样。NICE请求通道通过NICE reg-valid和NICE reg-ready握手确认传输。nice_reg_valid和其他请求信息应该保持稳定,直到nice_req_ready信号高。在NICE- core完成处理后,通过NICE响应通道将响应发送到E203处理器核心。

注意:当一个NICE指令在NICE- core中处理时,nice_req_ready信号被清除为低信号。因此,新的NICE请求将会暂停,直到当前的NICE指令完成。

5、 NICE的内存访问

NICE- core通过包含内存请求通道和内存响应通道的NICE接口访问内存。在内存请求通道中,nice - core发送ICB请求,包括nice icb_cmd_valid nice_icb_cmd_addr, nice icb_cmd_size, nice_icb_cmd_read和nice ICB cmd wdata(如果是写操作),然后这些信号等待来自E203处理器核心的nice_icb_cmd_ready。一旦有效就绪握手成功,E203处理器核心使用其LSU管道处理内存访问操作。在记忆响应通道。E203处理器内核发送niceicb rsp valid和nice_icb_rsp_rdata(如果是读操作)到nice - core,并等待niceicb_rsp_ready当nice - core要访问内存时,应该将nice_mem_holdup信号设置为HIGH,直到nice - core完成所有nice内存访问。这种机制阻塞了下面的load和store指令,这可以避免一些死锁场景。在nice_memholdup的帮助下,在NICE指令完成之前,NICE- core可以在任何时间启动一次或多次内存访问

6、 典型NICE操作示例

Fig. 2.4 NICE-Core multi-cycle processing

Fig. 2.5 NICE-Core access memory

Fig. 2.6 Illegal NICE instruction

本文介绍了RISC-V架构的E203处理器如何通过NICE单元实现可配置的自定义指令扩展,详细阐述了指令格式、接口设计、内存访问流程及典型操作示例。NICE通过4个通道进行指令处理,支持自定义指令组和内存操作,以提升性能并优化功耗。

本文介绍了RISC-V架构的E203处理器如何通过NICE单元实现可配置的自定义指令扩展,详细阐述了指令格式、接口设计、内存访问流程及典型操作示例。NICE通过4个通道进行指令处理,支持自定义指令组和内存操作,以提升性能并优化功耗。

1141

1141

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?