FPGA与VHDL语言学习3

目录

1. LPM_RAM的设置和调用方法,设计一个LPM_RAM

2. 简易正弦信号发生器(这里要使用的 data7X8 .mif 文件),要求用LPM设计一个七位计数器及对应的LPM_ROM

3. 《桶型移位寄存器设计》

4. 有符号数与无符号数比较器设计

1.参考PPT第七章第三节的LPM_RAM的设置和调用方法,参照图7-13至7-18,设计一个LPM_RAM,参照图7-19(这里要使用的 data7X8 .mif 文件, 参照图7-10,使用File→New→Memory Initalization File),进行仿真测试,并说明仿真测试结果正确的理由。

存储器初始化文件就是可配置于LPM_RAM或LPM_ROM中数据或程序代码。在设计中,通过EDA工具设计或设定的存储器中的代码文件必须由EDA软件在统一编译的时候自动调入,所以此类代码文件,即初始化文件的格式必须满足一定的要求。

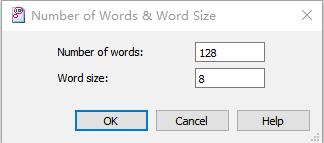

1,mif文件的生成

(1)直接编译法

(2)专用mif生成器:Mif_maker

等多种方式,在本实验中,采用mif生成器生成mif正弦波文件。文件内数据如下图

-

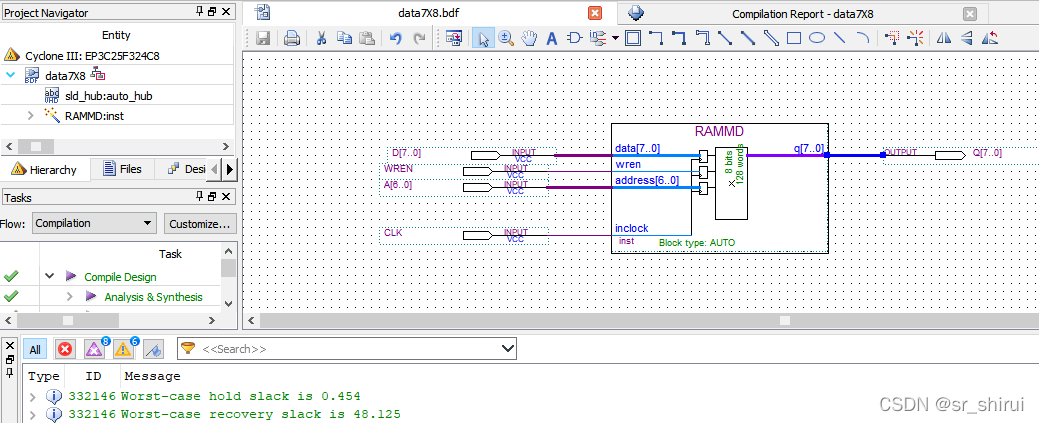

LPM_RAM的设计和调用

用LPM设计完成RAMMD。设定RAM参数block type:auto;dual clock;设定RAM仅输入时钟控制;设定当写入时,同步读出原数据:old data;设定初始化mif文件和允许在系统编辑。

最后设计出顶层电路原理图,如下图所示

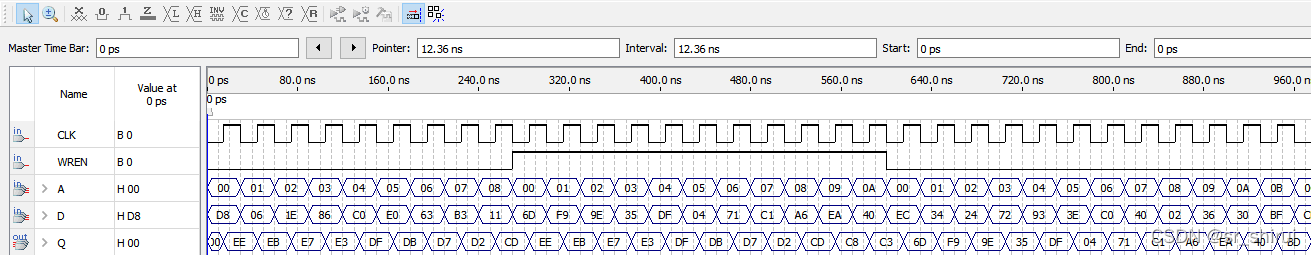

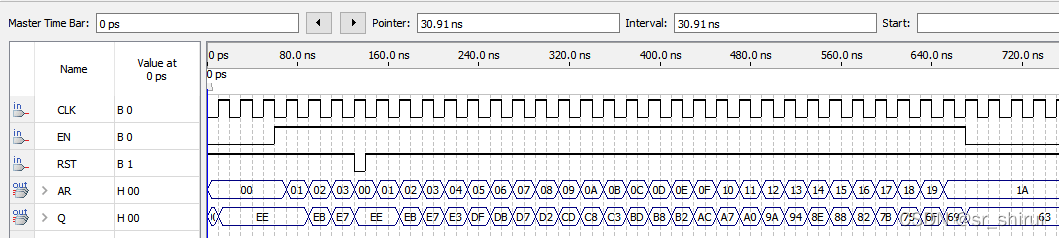

RAM波形图仿真结果如下,地址A是从0开始的,当写允许WREN=0时,读出RAM的数据,随着地址的递增,对应每一个时钟的上升沿,RAM中的数据被读出,他们分别是EE,EB,E7,E3等,正好与上图中mif文件的数据相符。说明初始化数据能被正常调入。

当写允许WREN=1时,地址A仍是从0开始的,数据D随着时钟上升沿,就会被写入。同时还可以观察到读出的数据EE,EB,E7,E3等,与输入的数据相符,即读出的是Old data , 与上图设置的相符合。当再次WREN=0时,由于地址再次从零开始,读出数据6D,F9,9E,35等,与写入数据相同。显然此RAM的各项功能符合要求。

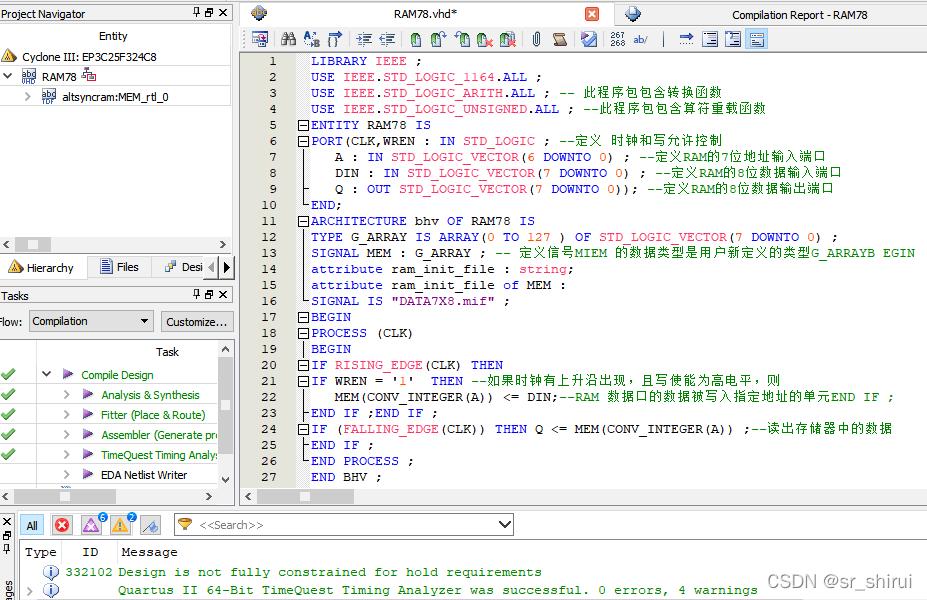

- 利用时钟的双边沿控制数据读写的VHDL存储器描述程序。

VHDL设计的存储器描述仿真的结果与电路图顶层设计的仿真结果相同,如下图,同理也是正确的。

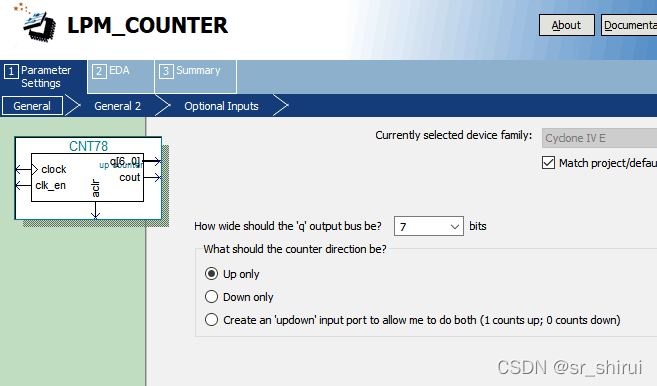

2.参考PPT第七章第四节的简易正弦信号发生器设计方法,设计一个简易正弦信号发生器(这里要使用的 data7X8 .mif 文件),要求用LPM设计一个七位计数器及对应的LPM_ROM,参照图7-25,用图形方式连接电路(因为没有硬件支持,不能加入D/A转换)。参照图7-26,对简易正弦信号发生器进行仿真测试,把简易正弦信号发生器设计图及仿真测试图(因为没有硬件支持,不能进行图7-27、7-28的仿真),并说明仿真测试结果正确的理由

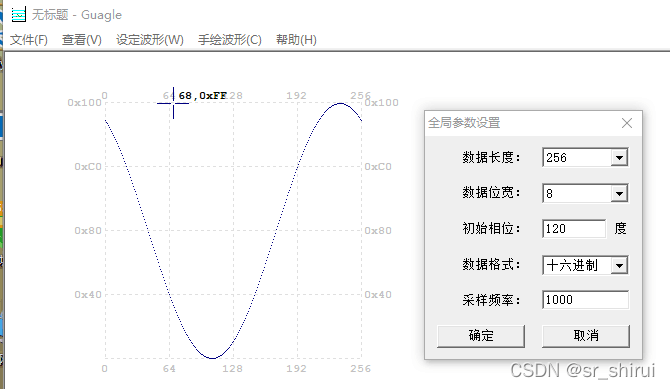

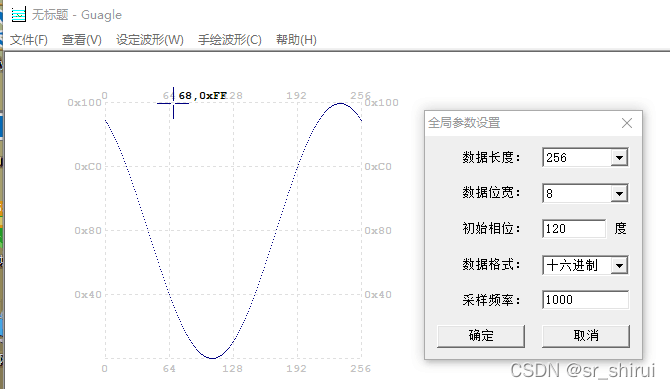

制作简易的正弦信号发生器首先是调用ROM,这完全可以仿照调用RAM的流程对LPM_ROM进行定值和调用。首先,设计正弦波mif文件,如下图所示,通过MIF_maker.exe设计初始文件。

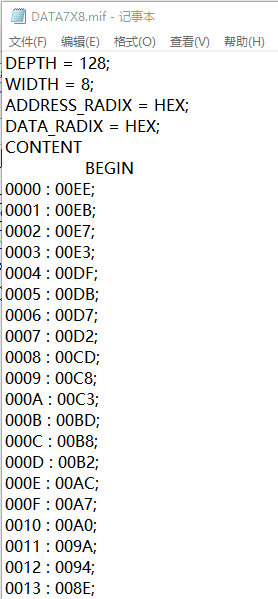

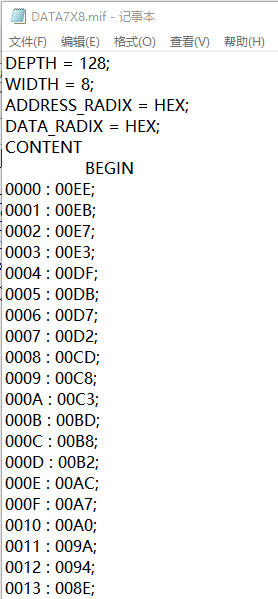

DATA7X8.mif文件的数据如下图所示。

定制调用的ROM模块的参数设置和初始化文件的配置如图,正弦波数据初始化文件用DATA7X8.mif

然后根据原理图中以定制完成的LPM_ROM设计一个建议的正弦信号发生器。

由如下三部分组成:

(1)计数器或地址信号发生器,这里根据以上ROM的参数,选择7位输出

(2)正弦信号数据存储器ROM(7位地址线,8位数据线),含有128个8位波形数据(一个正弦波形周期),即LPM_ROM:ROM78

(3)8位D/A(但在本实验中没有硬件)

上图所示的信号发生器结构图中,顶层文件是原理图工程ROMM,它包含两个部分:ROM地址信号发生器,由七位计数器担任;正弦数据ROM,由名为SIN_GNT的LPM_ROM模块构成。

地址发生器的时钟CLK的输入频率f0与每周期的波形点数(在此选择128点),以及D/A输出的频率关系是,f=f0/128。

注:下图是正弦信号发生器的顶层设计原理图,图中包含作为ROM地址信号发生器的七位计数器,和名为SIN_GNT的LPM_ROM模块构成。

上图是仿真结果,由波形可见,随着每一个时钟上升沿的到来,输出端口将正弦波数据一次输出,输出的数据与初始化mif中输入的数据相符。

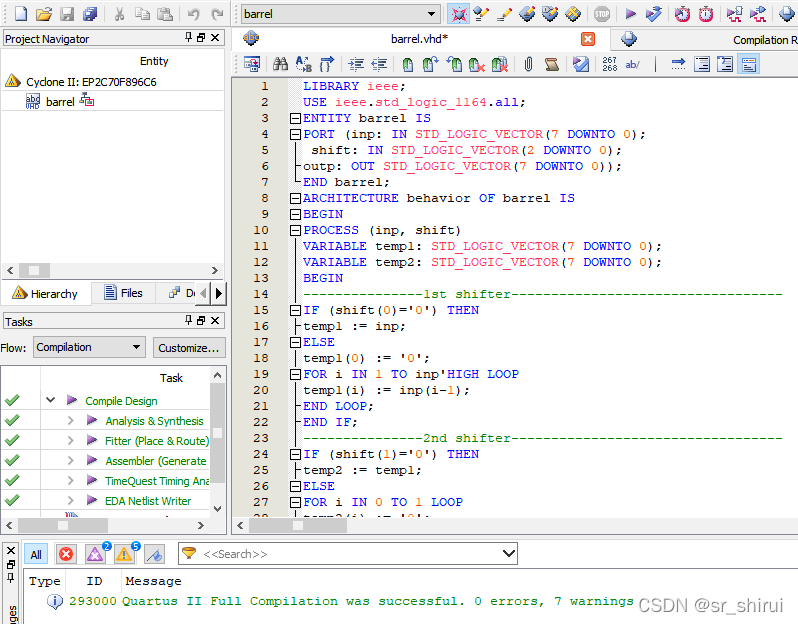

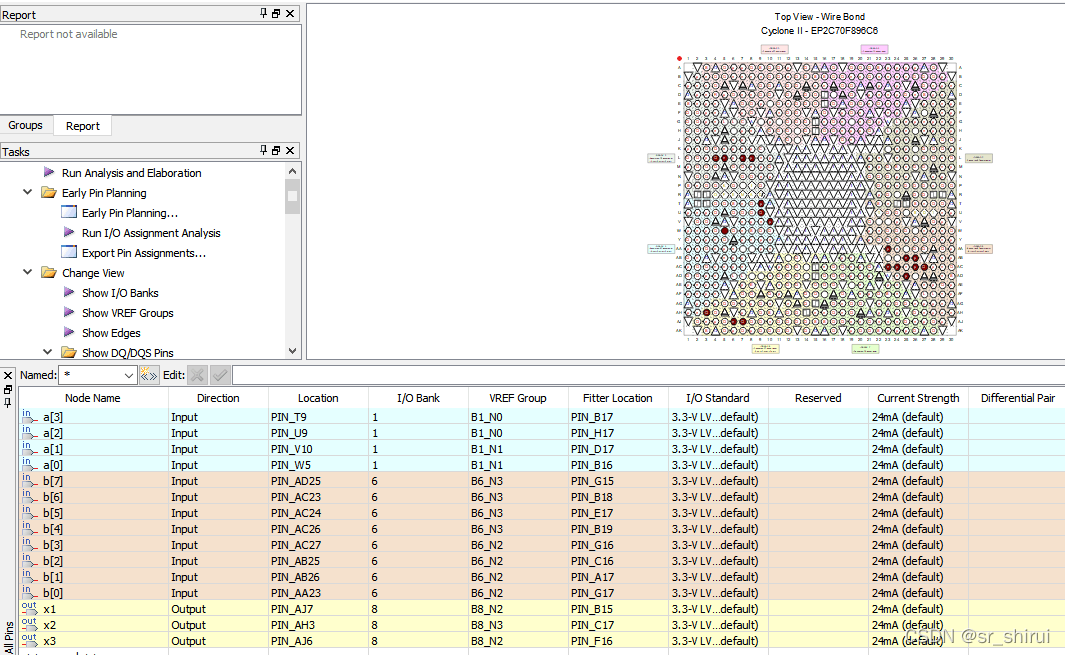

3.参考FPGA与VHDL语言实验指导书(在海大学习通的资料文件夹中)中 的实验一《桶型移位寄存器设计》,输入程序代码,对代码进行编译,试用Assignments→Assignment Editor进行I/O引脚锁定,重新编译。这里因为没有硬件电路板支持,只是学习如何进行引脚锁定及软件与硬件的关系。对项目进行波形图仿真,把程序与引脚锁定图及仿真结果图,说明仿真结果正确的理由。

实验一、桶形移位寄存器设计

1.在 QuartusⅡ中创建项目,并完成相关设备配置。

2.新建 VHDL 文档,输入代码并编译通过。

- 原理:桶形移位寄存器即循环移位寄存器,在浮点加减运算、压缩/解压缩和图像处理算法中有应用,常用的是组合逻辑实现的桶形移位寄存器。8位桶形移位器是有8个数据输入位,8个数据输出位和3个控制输入位的组合逻辑电路,其输出字等于输入字的循环移位,循环移位的次数由控制输入位指定。比如,如果输入字等于ABCDEFGH(每个字母表示一位),且输入控制位为101(5),则输出字为FGHABCDE。

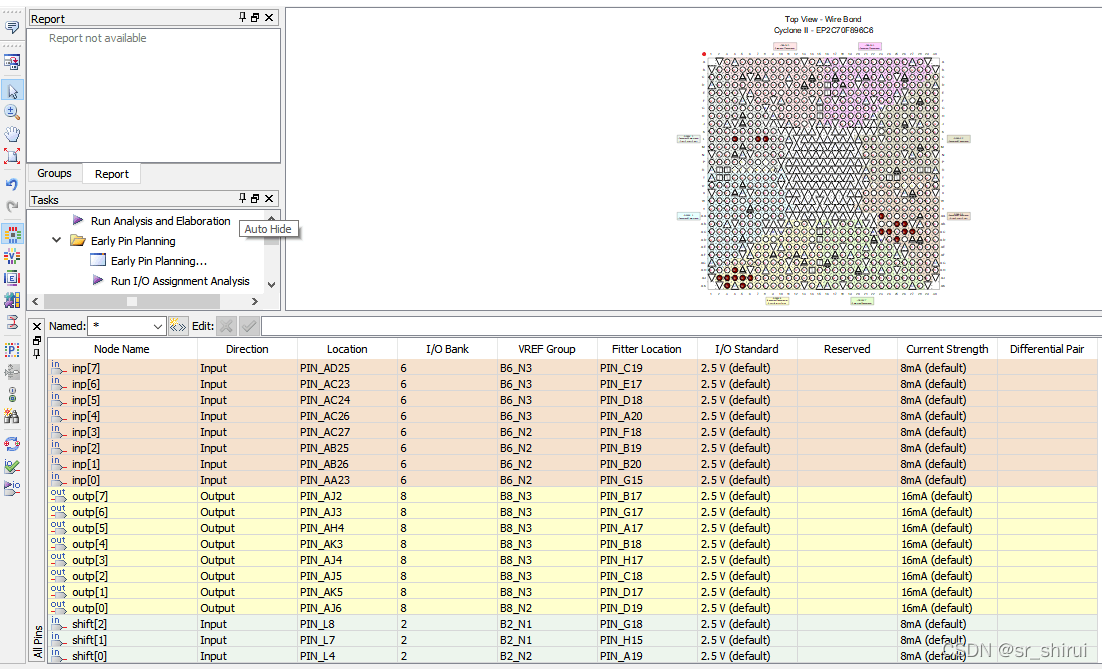

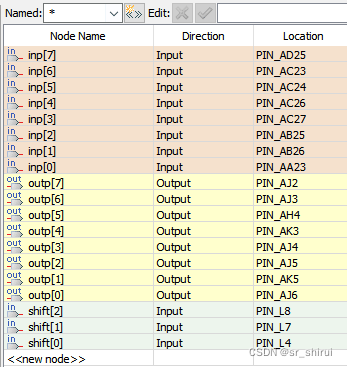

3.手动完成引脚分配,重新编译项目。

【注意:使用 SW[7]需要修改配置】 引脚分配:inp -> SW[7:0]; outp -> LEDR[7:0]; shift -> SW[17:15]

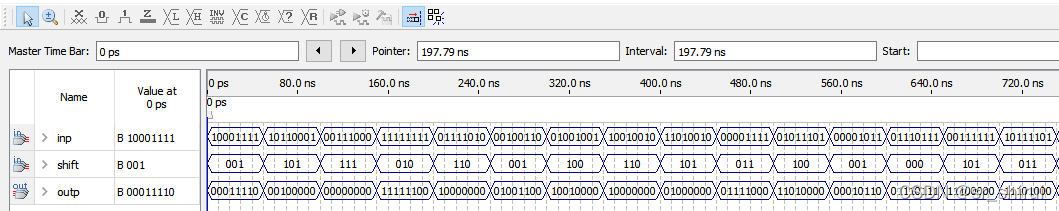

4.新建波形文件,分别进行功能仿真与时序仿真。

A.功能仿真:如第一格子中,shift=001,即将input中的数据1000 1111向左移位1位,并将右侧的空位用零补上,即Output=0001 1110。

第二个格子中,shift=101,即将input中的数据1011 0001向左移位5位,并将右侧的空位用零补上,即Output=0010 0000。仿真正确

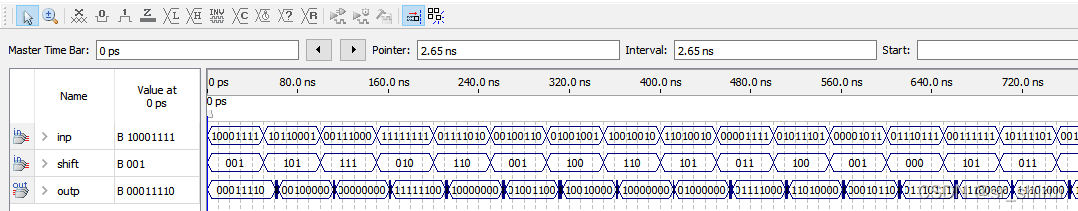

B. 时序仿真:

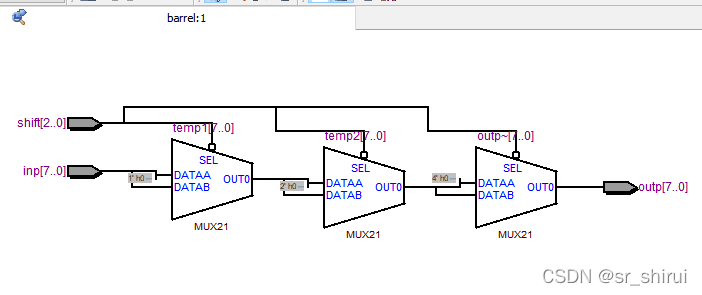

- Netlist Viewers下的RTL结构

4. 参考FPGA与VHDL语言实验指导书中 的实验二《有符号数与无符号数比较器设计》,输入程序代码,对代码进行编译,试用Assignments→Assignment Editor进行I/O引脚锁定,重新编译。这里因为没有硬件电路板支持,只是学习如何进行引脚锁定及软件与硬件的关系。对项目进行波形图仿真,把程序与引脚锁定图及仿真结果图上交,说明仿真结果正确的理由。

实验二、有符号数与无符号数比较器设计

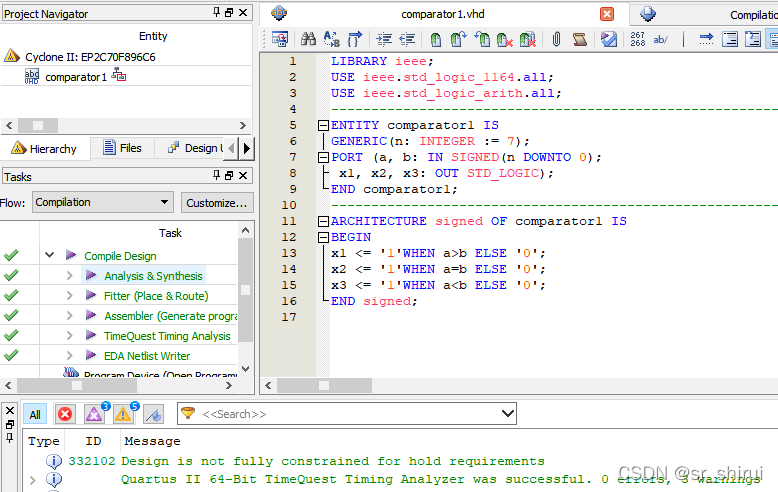

- 有符号数比较器:

1.在 QuartusⅡ中创建项目,并完成相关设备配置。

2.新建 VHDL 文档,输入代码并编译通过。

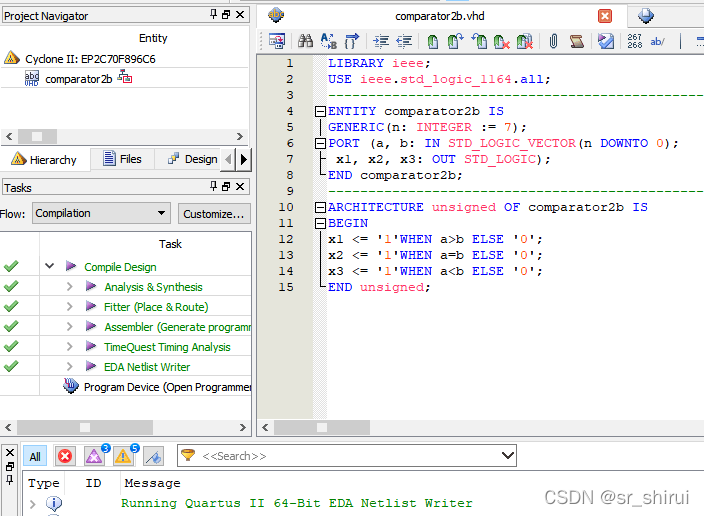

- 原理:其中 a 与 b 分别代表两个有符号数;x1 表示 a > b ,x2 表示 a = b ,x3 表示 a < b

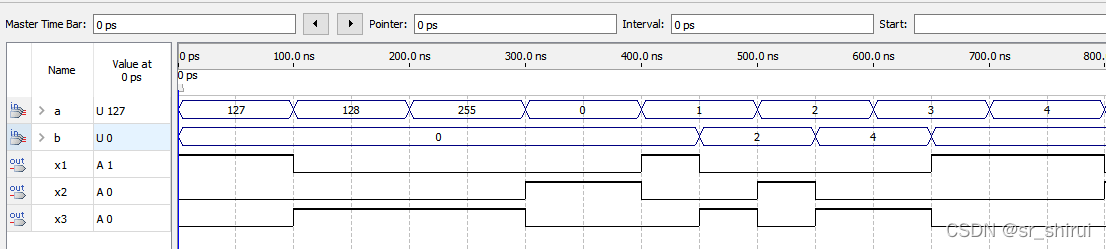

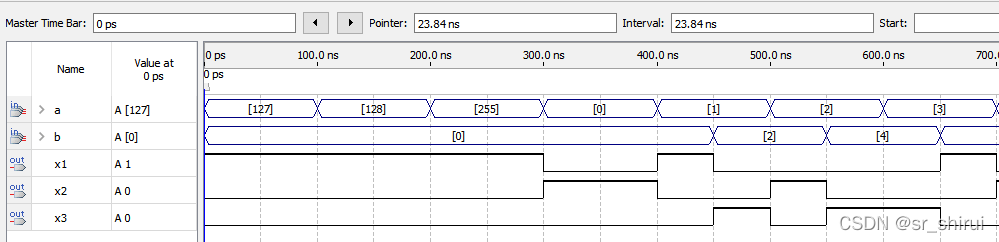

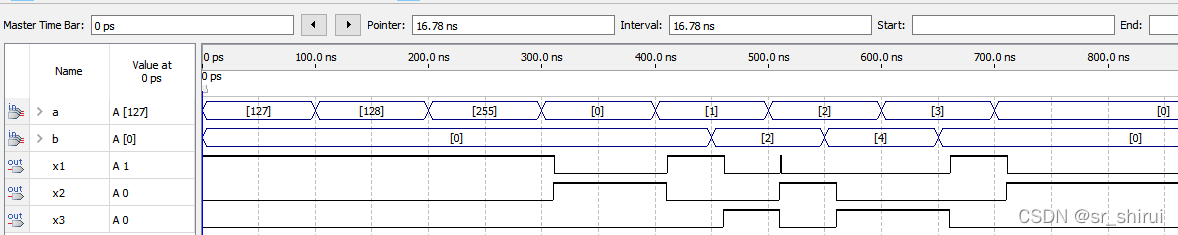

4.新建波形文件,分别进行功能仿真与时序仿真。有符号数比较器

A.功能仿真:如第一个格子,当 a 为127=0111 1111(B),b = 0; a > b,则x1 = 1,x2 = x3 = 0。

如第二个格子,当 a 为128=1000 0000(B) -0的表示方法,b = 0; a < b,则x3 = 1,x2 = x1 = 0。

如第三个格子,当 a 为255=1111 1111(B) -127的表示方法,b = 0; a < b,则x3 = 1,x2 = x1 = 0。

如第四个格子,当 a =b = 0; 则 x2 = 1,x1 = x2 = 0。验证成功。

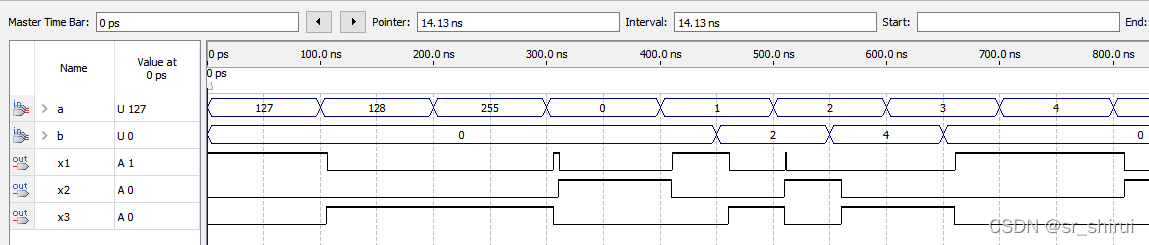

B.时序仿真:

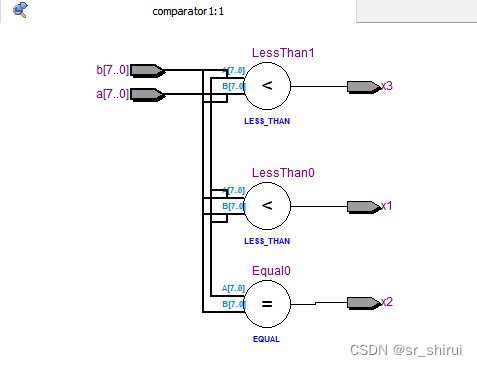

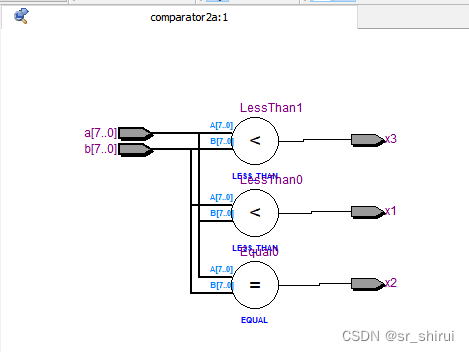

- Netlist Viewers下有符号数比较器的RTL结构

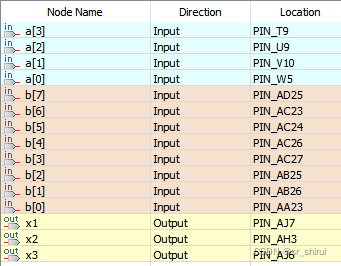

6.手动完成引脚分配,重新编译项目。

引脚分配:a -> SW[17:10]; b -> SW[7:0]; x1 -> LEDR[17]; x2 -> LEDR[8]; x3 -> LEDR[0]

- 无符号数比较器 a:

1.在 QuartusⅡ中创建项目,并完成相关设备配置。新建VHDL 文档,输入代码并编译通过。

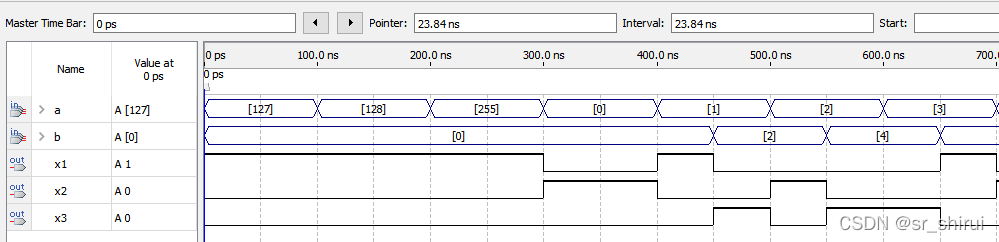

2.新建波形文件,分别进行功能仿真与时序仿真。无符号数比较器

A.功能仿真:如第一个格子,当 a 为127=0111 1111(B),b = 0; a > b,则x1 = 1,x2 = x3 = 0。

如第二个格子,当 a 为128=1000 0000(B),b = 0; a > b,则x1 = 1,x2 = x3 = 0。

如第三个格子,当 a 为255=1111 1111(B),b = 0; a > b,则x1 = 1,x2 = x3 = 0。

如第四个格子,当 a =b = 0; 则 x2 = 1,x1 = x2 = 0。

在第450ns-500ns之间时,a = 1,b = 2; a < b,则x3 = 1,x1 = x2 = 0。验证成功。

B.时序仿真:

3. Netlist Viewers下无符号数比较器a的RTL结构

- 无符号数比较器 b:

1.无符号数比较器b的仿真波形图同a。

- Netlist Viewers下无符号数比较器b的RTL结构

4万+

4万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?