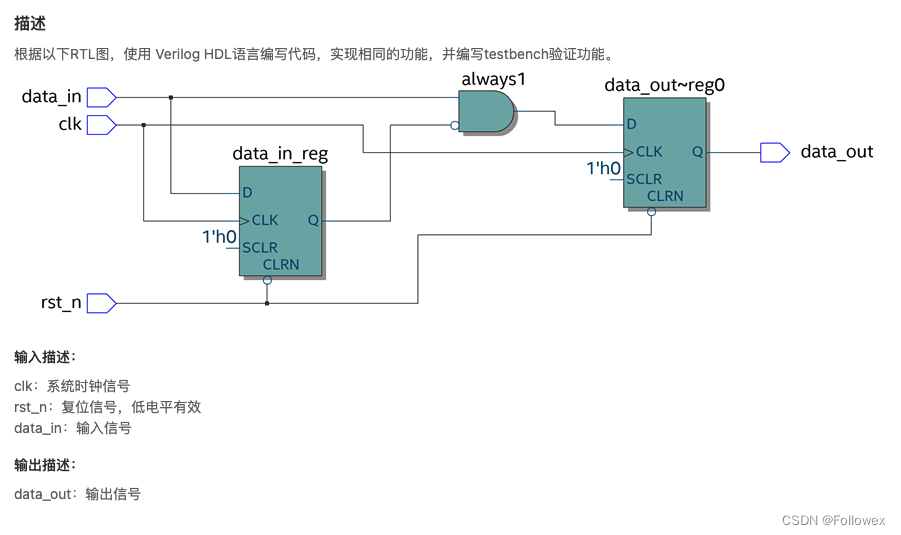

`timescale 1ns/1ns

module RTL(

input clk,

input rst_n,

input data_in,

output reg data_out

);

reg data_in_reg;

wire data_out_pre;

always @(posedge clk or negedge rst_n)

begin

if(!rst_n) begin

data_in_reg <= 1'b0;

end else begin

data_in_reg <= data_in;

end

end

// 上一拍为低,当前拍为高

assign data_out_pre = data_in && (!data_in_reg);

always @(posedge clk or negedge rst_n)

begin

if(!rst_n) begin

data_out <= 1'b0;

end else begin

data_out <= data_out_pre;

end

end

endmodule

1066

1066

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?