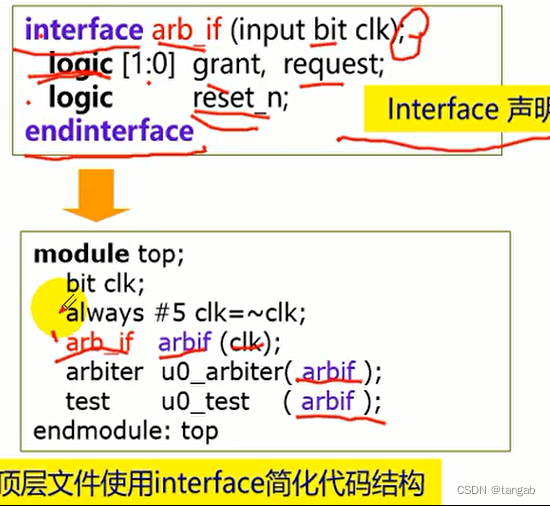

verilog的testbench是直接来进行连线,dut的输入有tb创造输入, 输出有tb接受,在tb中例化module来相互连接。

FSM seq_ul(.clk(clk),

.reset(reset),

.in(in),

.out(out),

.state(state)

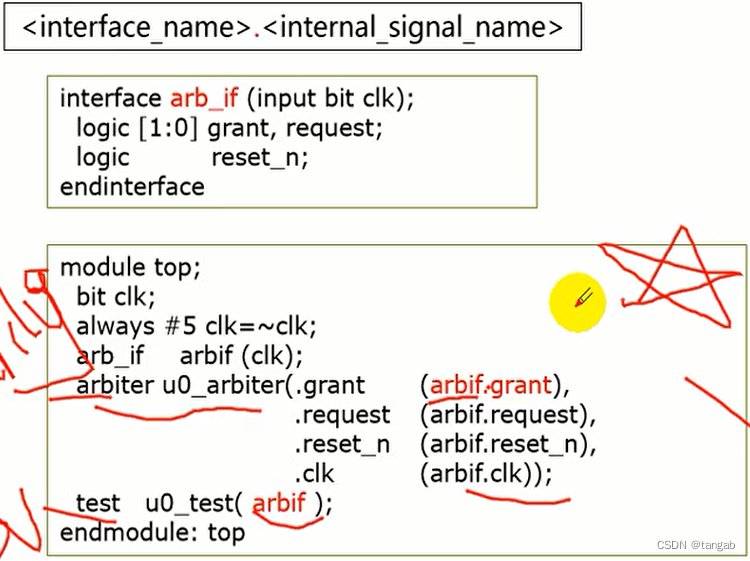

);接口则是设置一堆wire或者reg放进interface中,两边按这个连接。

tb和dut直接传入例化的接口,就有了相应的wire和reg

dut用的verilog,tb用sv的情况

dut用的verilog,tb用sv的情况

modport卸载interface对应设置端口输入输出

clocking

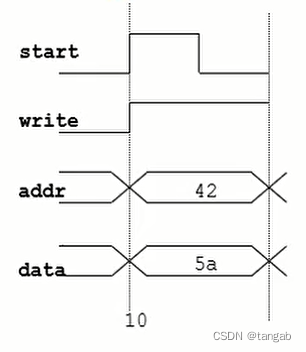

tb中为了防止信号的冲突,比如data,clk,address,write_en在同一个时间段达到上升沿,

类似情况可能出现冲突,即data是否出现,可能在写之前出现,导致产生未知结果。在interface中用clock将信号绑定至上升沿,即在上升沿信号发出的时候产生激励和输出,按可以在interface中给input提前一个timescale,output延迟一个timescale来防止冲突。

类似情况可能出现冲突,即data是否出现,可能在写之前出现,导致产生未知结果。在interface中用clock将信号绑定至上升沿,即在上升沿信号发出的时候产生激励和输出,按可以在interface中给input提前一个timescale,output延迟一个timescale来防止冲突。

上图就是在interface上写clock cb@(posedge clock);default.....。

clock只能用于tb中

2984

2984

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?