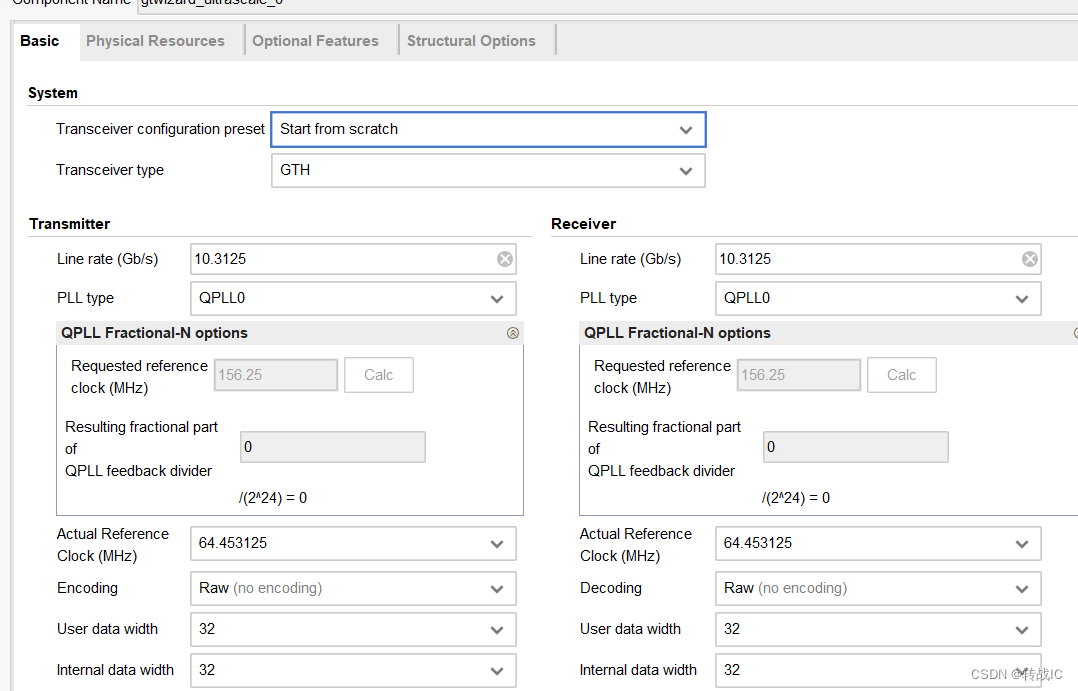

1.如果按照默认配置

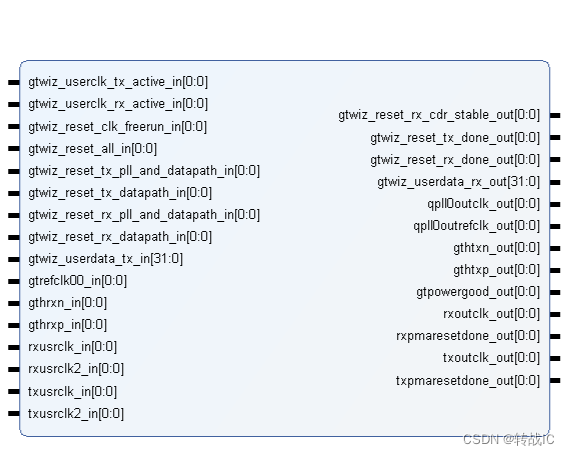

1.1框图

1.2.信号说明

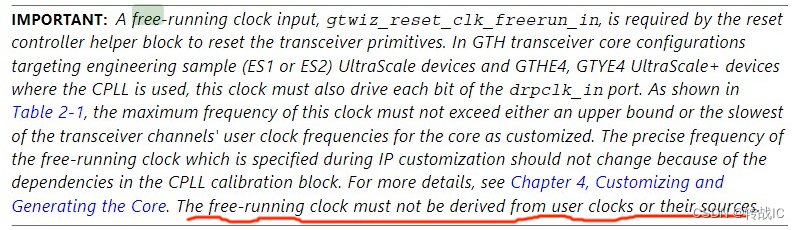

1.2.1复位信号

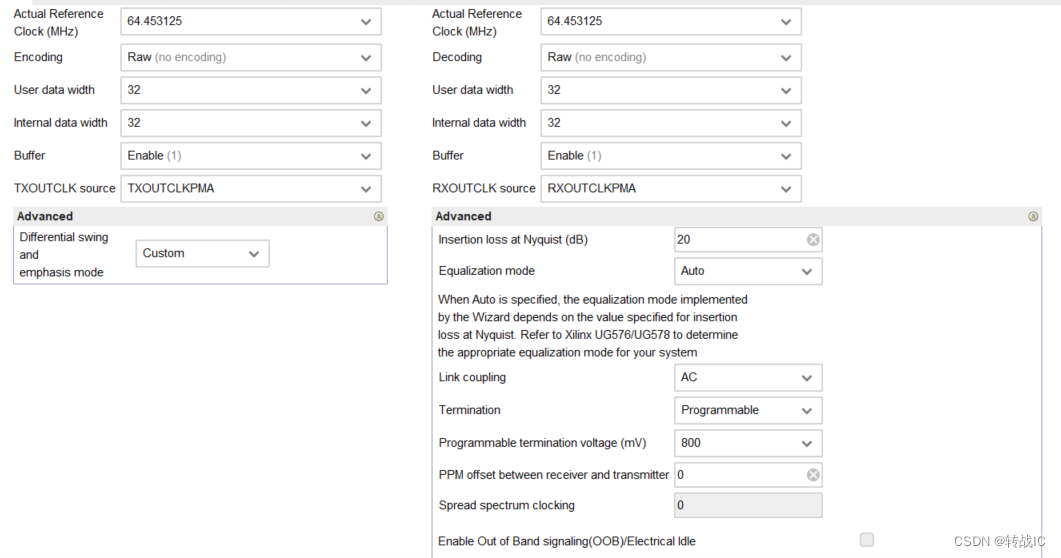

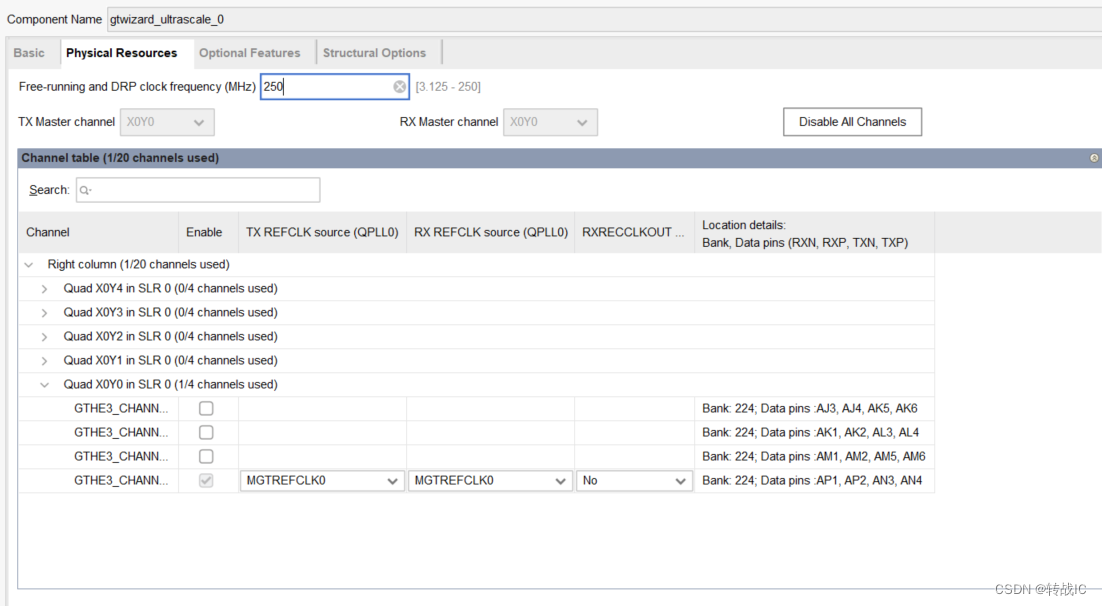

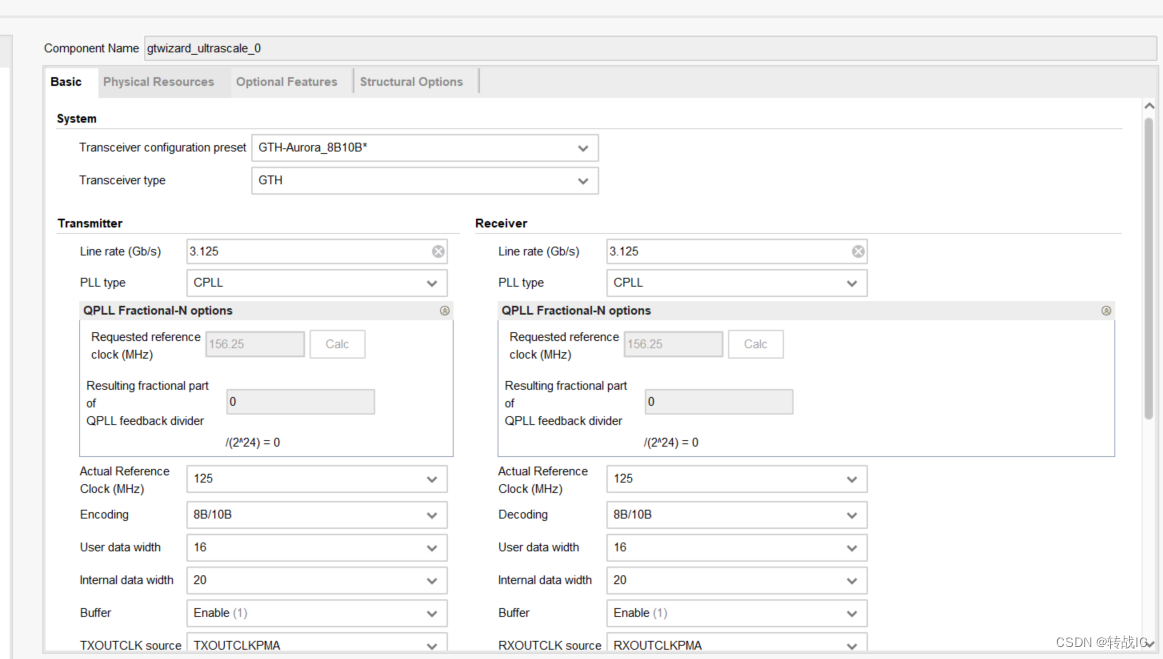

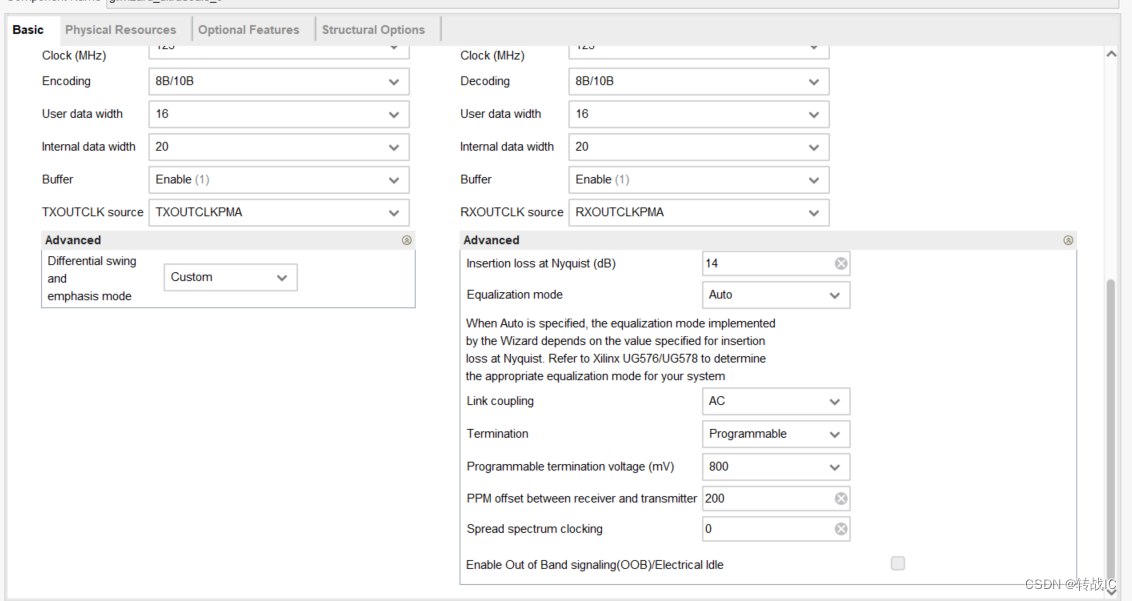

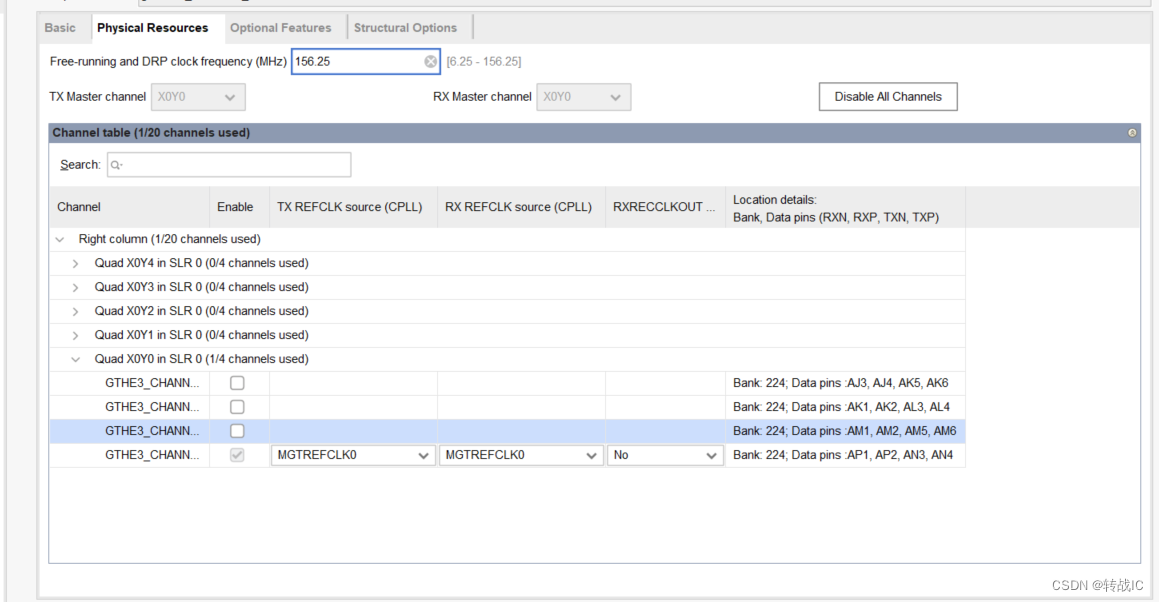

gtwiz_reset_clk_freerun_in: 复位控制器辅助块的运行时钟,要启用此模块,必须提供此时钟(注意改时钟频率要和我们在ip核的Physical Resources 配置的一致)且不能以用户时钟为源。

gtwiz_reset_all_in:复位TX和RX的PLL和Datapath(Datapath=PMA+PCS)。

gtwiz_reset_tx_pll_and_datapath_in:复位TX的PLL和Datapath.

gtwiz_reset_tx_datapath_in:复位TX的Datapath.

gtwiz_reset_rx_pll_and_datapath_in:复位RX的PLL和Datapath.

gtwiz_reset_rx_datapath_in:复位RX的Datapath.

gtwiz_reset_tx_done_out:在完成TX的复位后拉高,与主通道TXUSERCLK2同步。

gtwiz_reset_rx_done_out:在完成RX的复位后拉高,与主通道RXUSERCLK2同步。

gtwiz_reset_rx_cdr_stable_out:标明RX原语的时钟和数据恢复(CDR)电路是稳定的。保留;不使用

txpmaresetdone_out[0:0]:如果是高电平,tx通道的pma部分复位完成

rxpmaresetdone_out[0:0]:如果是高电平,rx通道的pma部分复位完成

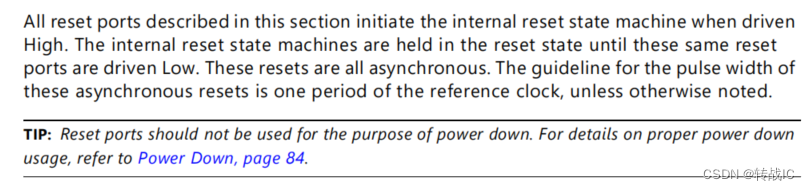

注意:

1.所以的复位信号都是高电平有效,且高电平时系统一直处在复位状态,只有拉低之后,系统才会完成复位。

2.gtwiz_reset_clk_freerun_in:这个信号手册上一直没有具体的介绍,也不知应该输入频率范围在什么之间,一般给一个板子上的时钟就行,不要高于给CPLL和QPLL的参考时钟频率大小

1.2.2时钟源信号

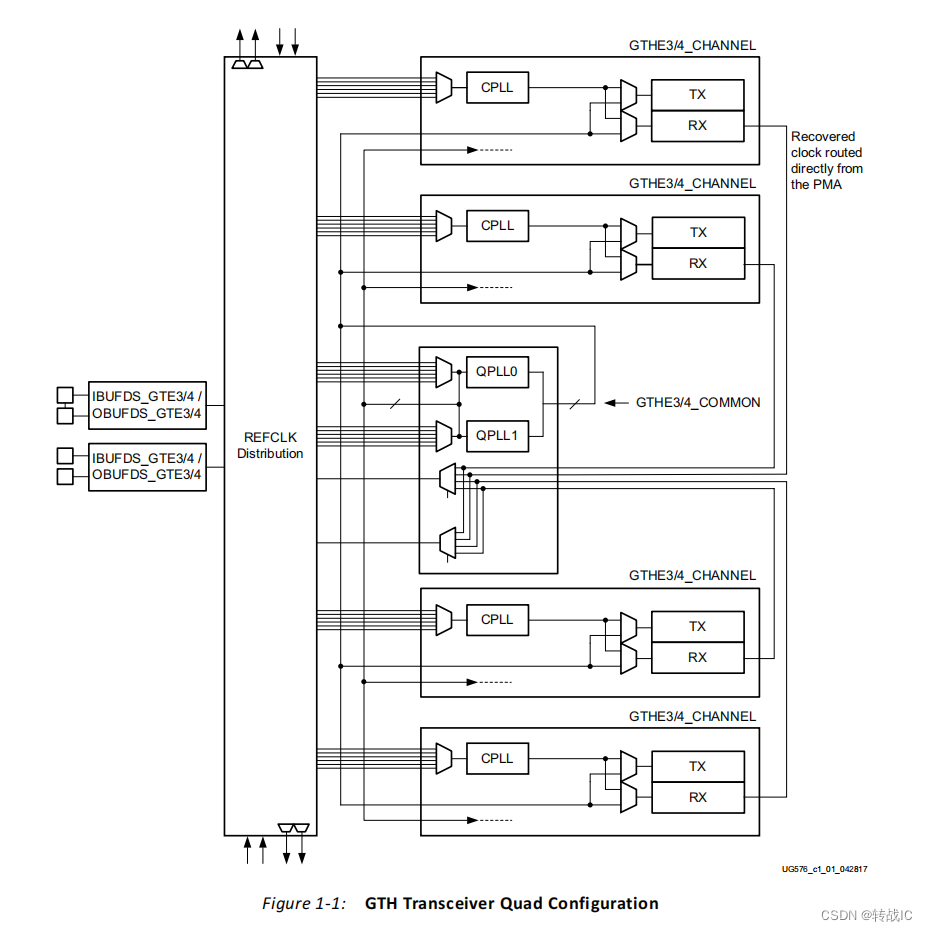

gtrefclk00_int[0:0]:外部输入的参考差分时钟经过ibufds后得到的单端时钟信号,作为cpll和qpll的可以选择的时钟源。在7系列器件中,一个quad可以选择相邻一个南北quad的参考时钟作为输入,ultra器件中则为相邻两个。

注意:该信号的时候时钟频率要和我们在IP核配置界面的actual reference clock一致

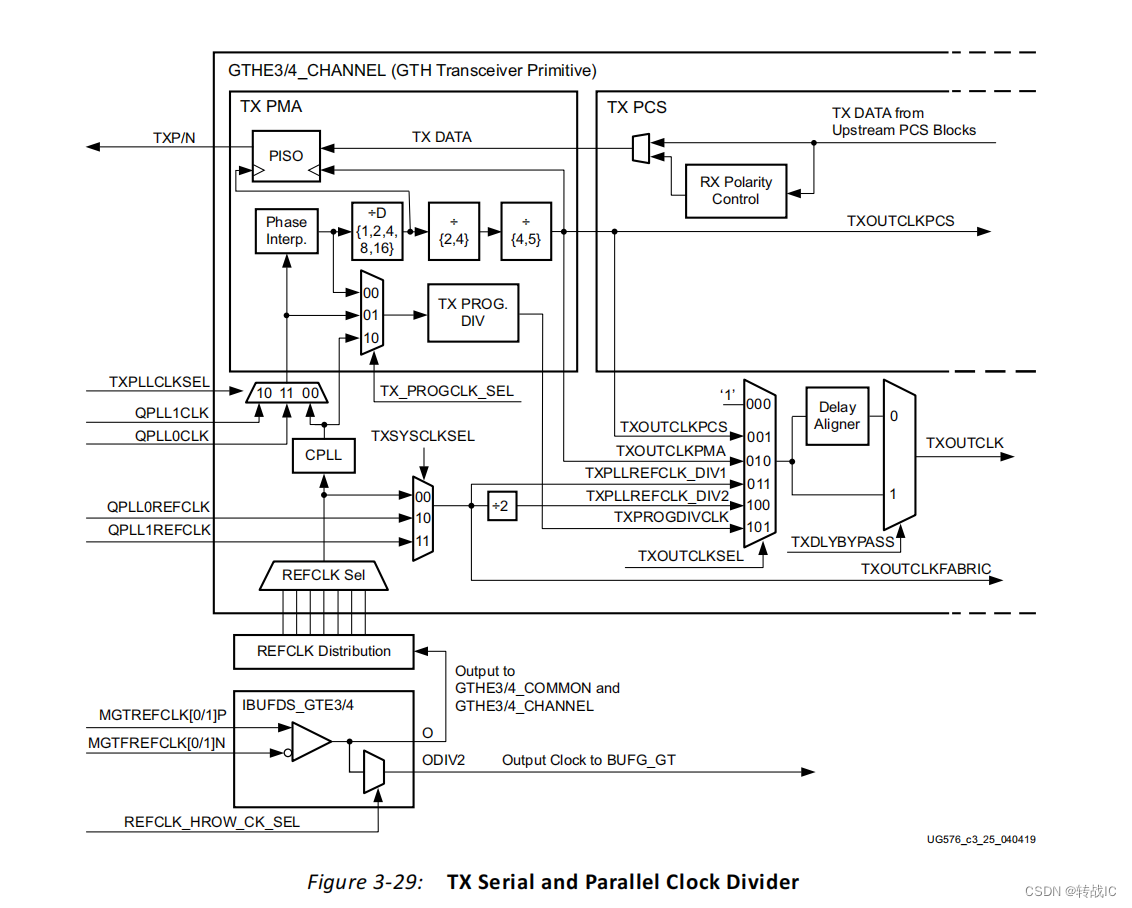

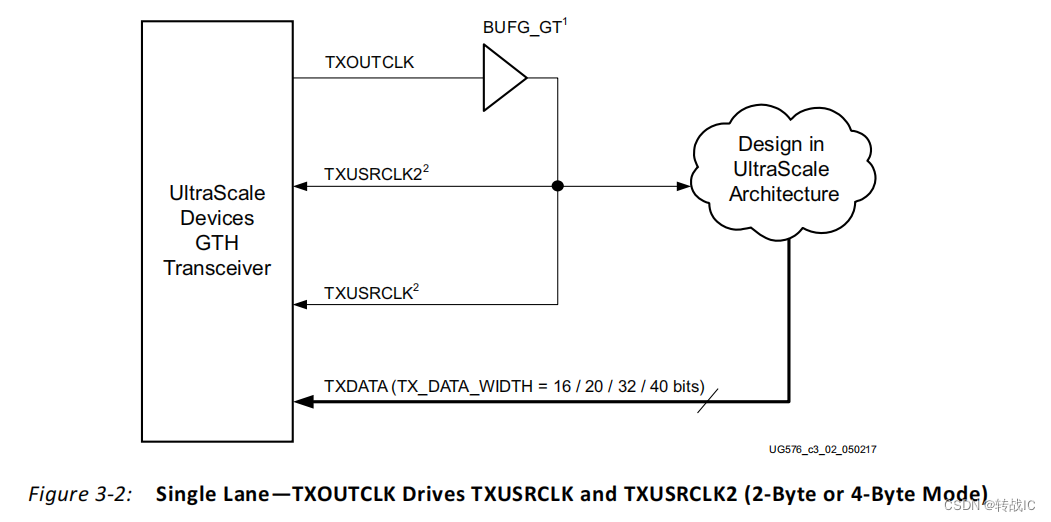

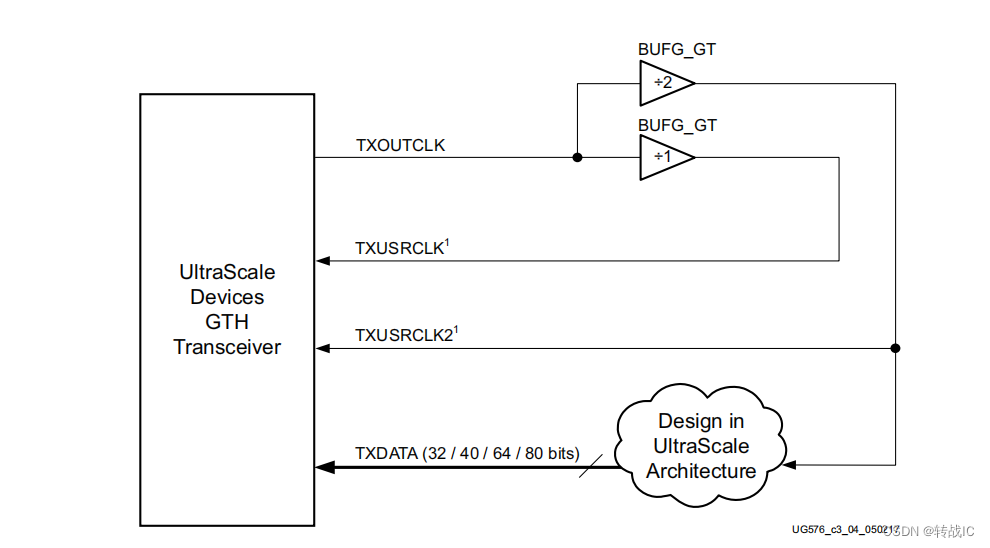

txoutclk_out:GT核为tx通道输出的时钟,可以来自PMA、PCS、配置分频,在多通道时由中间通道作为源产生

rxoutclk_out:这个是rx通道输出的时钟频率

txusrclk_in:提供给TX PCS的时钟,由txoutclk_out信号产生

txusrclk2_in:我们通过这个时钟来往gt核中发送数据

gtwiz_userclk_tx_active_in :标志txuserclk_in和txuserclk2_in信号是有效,高电平有效

(在由ip核产生的示例工程中,它是这么使用这个信号的,把这个输入信号当作为一个bufg的复位信号 )

BUFG_GT bufg_gt_usrclk_inst

.CE (1'b1),

.CEMASK (1'b0),

.CLR (gtwiz_userclk_tx_reset_in),

.CLRMASK (1'b0),

.DIV (P_USRCLK_DIV),

.I (gtwiz_userclk_tx_srcclk_in),

.O (gtwiz_userclk_tx_usrclk_out)

);)

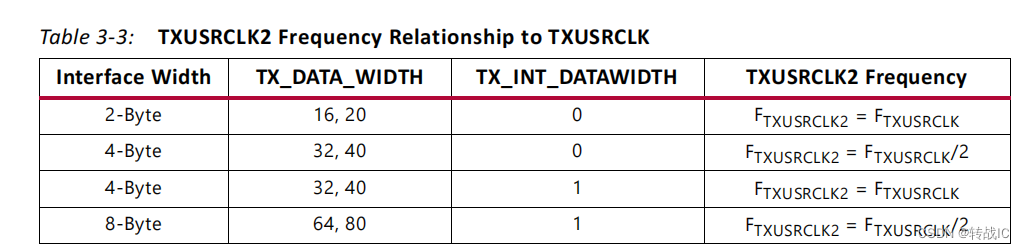

注意:其实txusrclk_in和txusrclk2_in是有关系的

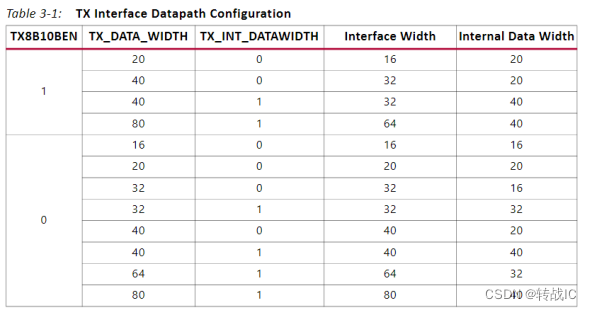

其中,TX_DATA_WIDTH和TX_INT_DATA_WIDTH是GT核内部信号,在配置GT数据位宽与8b10b使能时已经确定,对应关系如下

TX_DATA_WIDTH:是我们可以配置的值,决定TX_DATA的位宽。但是其实在配置ip核的时候,我们是去配置TX_DATA的位宽,然后ip核去自动帮我们配置TX_DATA_WIDTH的值

TX_INT_DATAWIDTH:是我们可以配置的值,用来控制TX内部数据的宽度即Inter Data WIDTH。但是其实在配置ip核的时候,我们是去配置Inter Data WIDTH的位宽,然后ip核去自动帮我们配置TX_INT_DATAWIDTH的值

rx部分其实核tx部分是对应的,这里不过多阐述

gtwiz_userclk_rx_active_in:标志rxuserclk_in和rxuserclk2_in信号是有效,高电平有效

rxusrclk_in:提供给RX PCS的时钟

rxusrclk2_in:我们通过这个时钟来往gt核中接收数据

1.2.3数据发送接收信号

gthrxn_in[0:0]:这个就是RX通道接收外部信号的差分引脚

gthrxp_in[0:0]:这个就是RX通道接收外部信号的差分引脚

gthtxn_out[0:0]:这个就是TX通道发送信号的差分引脚

gthtxp_out[0:0]:这个就是TX通道发送信号的差分引脚

注意:这四个引脚理应在约束文件中进行管脚约束,但是这个约束已经在gt核中帮我们做了,只要在ip配置中选择好用哪个cahnel,ip就会自动帮我们把引脚连上

1.2.4输入数据信号

gtwiz_userdata_tx_in[31:0]:就是是我们把需要发送的数据输入到这个端口,在每一个 txusrclk2的上升沿更新

即我们把数据从gtwiz_userdata_tx_in[31:0]端口输入,经过TX通道,从gthtxn_out[0:0],gthtxp_out[0:0]差分引脚对把数据输出

1.2.5接收数据信号

gtwiz_userdata_rx_out[31:0]:就是接收到的数据,,在每一个 rxusrclk2的上升沿更新

即我们把数据从gthrxn_in[0:0],gthrxp_in[0:0]差分引脚接收数据,然后经过RX通道,从gtwiz_userdata_rx_out[31:0]把数据发送出去

1.2.6与qpll相关信号

qpll0outclk_out[0:0]:用于驱动TX/RX通路,就是下图的信号

qplloutrefclk_out[0:0]:可作为TXOUTCLK的源输出,就是下图的信号

因为ultraScale中有两个qpll,这里我们在ip核配置里用的qpll0

1.2.7与电源相关信号

gtpowergood_out[0:0]:拉高表示电源已经接上了,系统开始工作

2.如果把ip核配置为aurora 8b/10b模式

2.1框图

这里只讲新增的几个信号,其余信号的功能在上面都讲过

2.2信号说明

2.2.1时钟信号

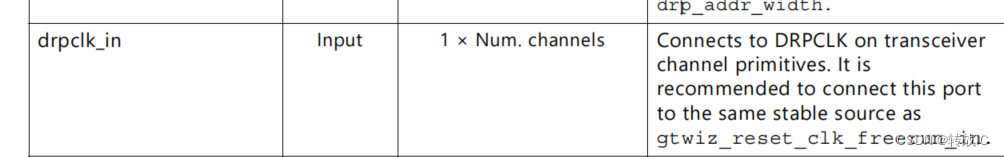

1.drp的时钟:这个时钟是给GT收发器动态调制功能的时钟(不用管干嘛的)官方推荐这个时钟直接给和gtwiz_reset_clk_freerun_in一样的时钟

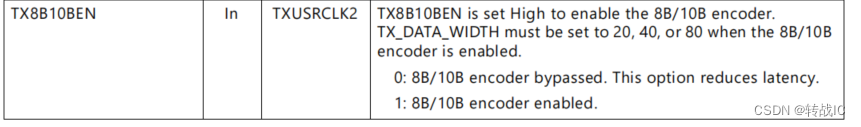

2.2.2与8b/10b功能相关信号

1.rx8b/10en_in[0:0]:拉高就启动8b/10译码功能,拉低不启动

2.tx8b/10en_in[0:0]:拉高就启动8b/10译码功能,拉低不启动

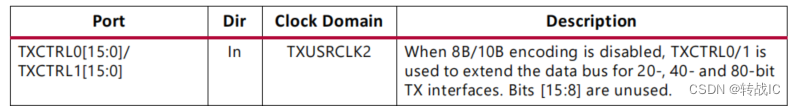

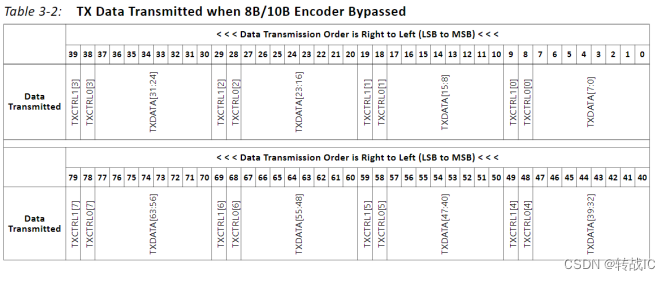

3.txctrl0_in[15:0]:在8b/10b模式下无用,不用管

4.txctrl1_in[15:0]:在8b/10b模式下无用,不用管

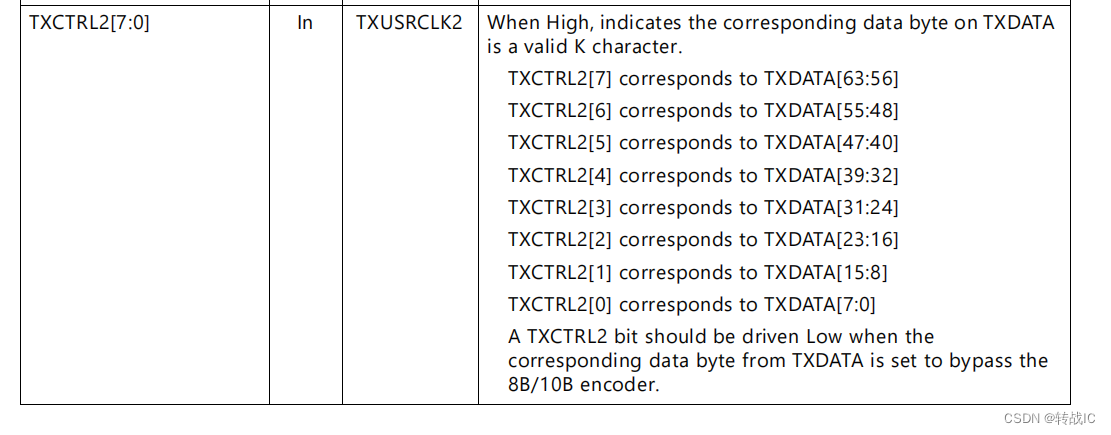

5.txctrl2_in[7:0]:8B/10B表包含经常用于控制功能的特殊字符(K字符)。TXCTRL2端口用于指示TXDATA上的数据是K字符还是常规数据。如果相应的TXCTRL2位被驱动为高位,则8B/10B编码器会检查接收到的TXDATA字节以匹配任何K个字符。

6.rxctrrl0_out[15:0]:在8b/10b模式下无用,不用管。

7.rxctrlr1_out[15:0]:在8b/10b模式下无用,不用管。

(注意:rxctrrl0_out[15:0]、rxctrlr1_out[15:0]用于在8b/10b被旁路时填充用户数据的高位。)

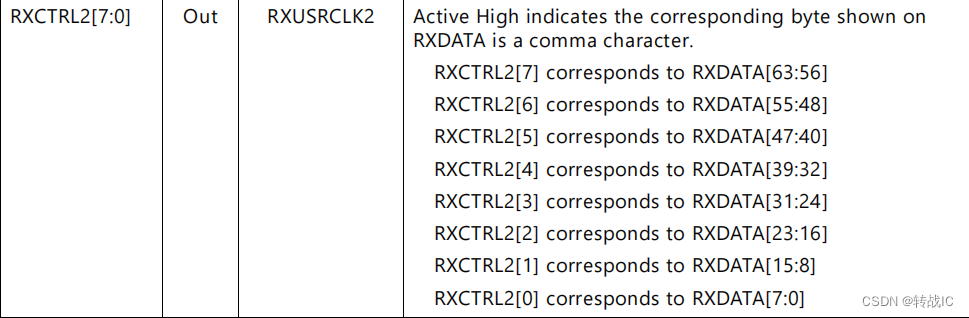

8.rxctrl2_out[7:0]:RXCTRL2端口用于指示RXDATA上的数据是K字符还是常规数据。如果相应的RXCTRL2位被驱动为高位,发送的RXDATA字节相应的自节是K字符。

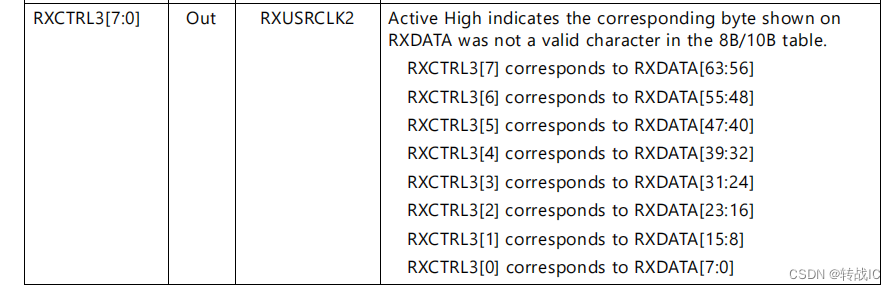

9.rxctrl3_out[7:0]:拉高表示在RXDATA上显示的相应字节不是8B/10B表中的有效字符。因为用户数据经过8b10b编码之后,只有限种10位的数据,如果rx接到的10位数据不是经过8b10b编码后的任一一种,那就把RXDATA对应位的rxctrl3_out[7:0]拉高

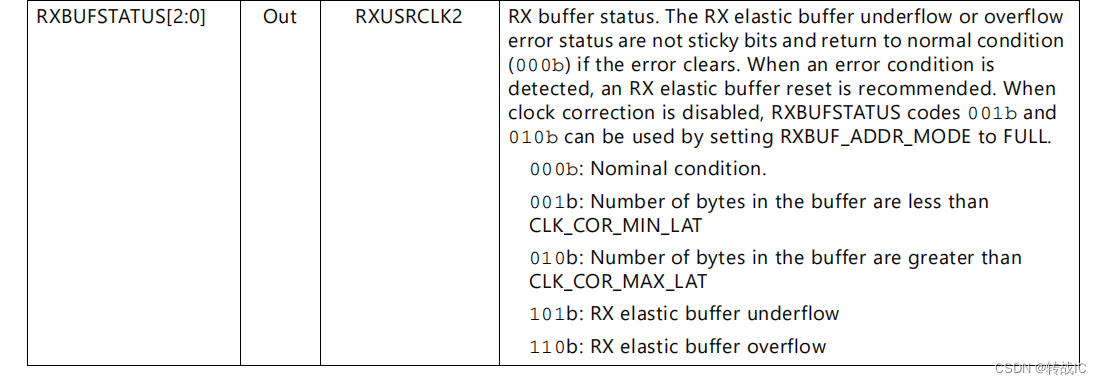

2.2.3与RX buffer相关信号

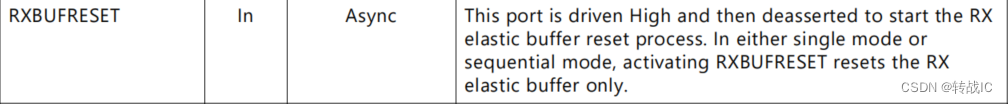

1.rxbufreset_in[0:0]:rxbuffer的复位信号。此端口被驱动为高,然后拉低以启动RX弹性缓冲区重置过程。在单个模式或顺序模式下,激活RXBUFRESET只会重置RX弹性缓冲区。

2.rxbufstatus_out[2:0]:表示rxbuf此时的状态

2.2.4逗号检测功能

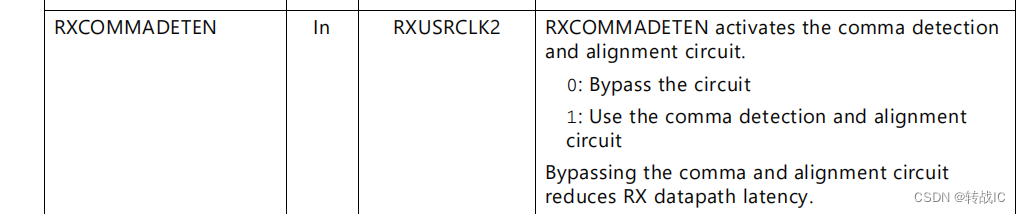

1.rxcommadeten_in[0:0] :开启逗号检测的功能

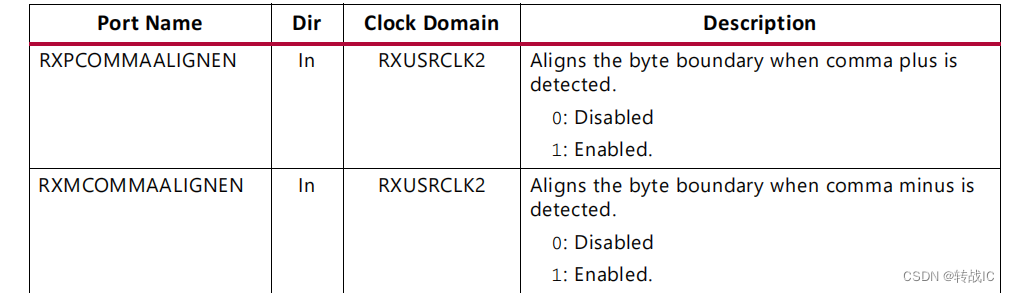

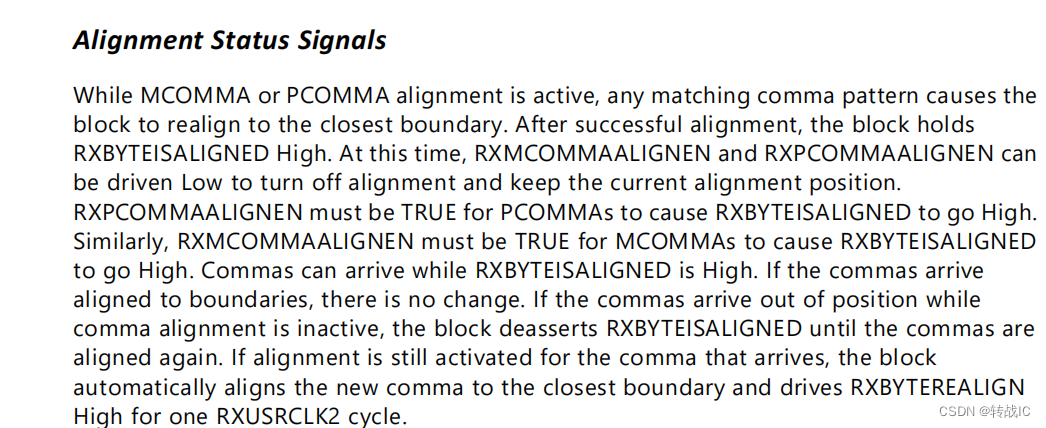

2.rxpcommaalignen[0:0]:高电平使能+1k码检测

3.rxmcommaalignen[0:0]:高电平使能-1k码检测

8B/10B编码方案中会有+1与-1两种状态,这就是所谓的极性偏差( running disparity,RD)。所以在检测K码时,K28.5就会有两种K码,所以K码对齐功能有MCOMMA和PCOMMA模式,也就是plus comma 和Minus Comma。把这两个信号拉高就表示,启动+1和-1的k码检测

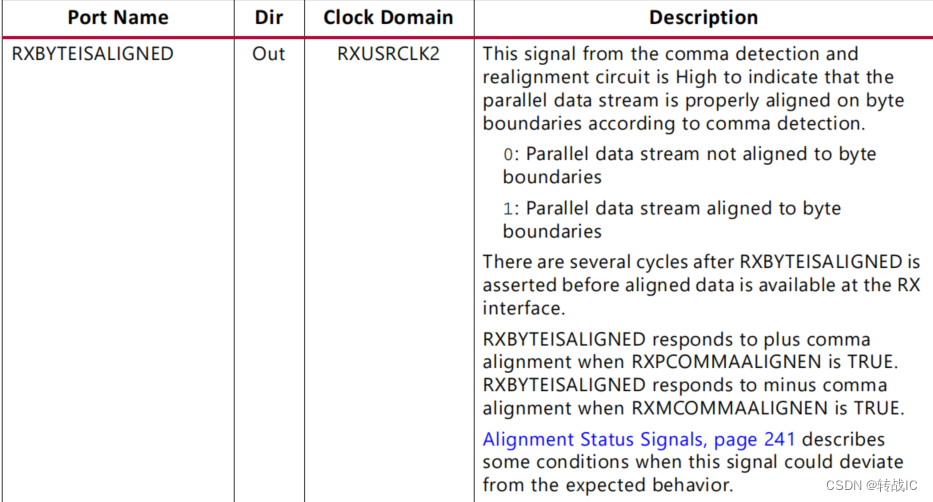

4.rxbyteisaligned_out[0:0]:拉高表示信号已经对齐了.这时可以将ENPCOMMALIGN和ENMCOMMALIGN两个信号拉低,关闭K码对齐功能。

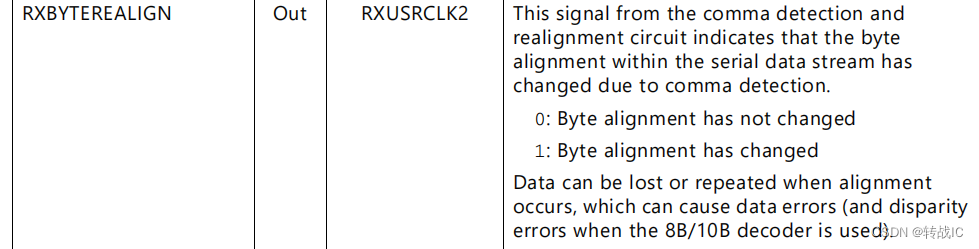

6.rxbyterealign_out[0:0]:RXBYTEREALIGN是状态信号,用来表示对齐的K码是否发生变化或者说现在是否在对齐状态,=1表示字节对齐边界没有改变,=0表示字节对齐边界改变了。所以当RXBYTEREALIGN为0时我们可以重新使能字节对齐

(这里给出文档中k码对齐的流程:

)

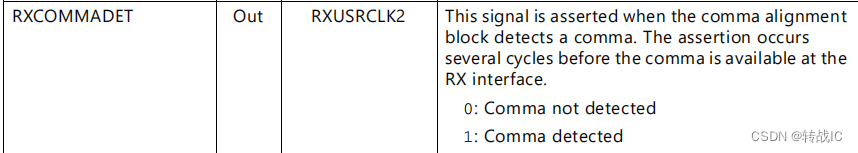

7.rxcommadet_out[0:0]:RXCOMMADET是个状态信号,当K码对齐模块检测到K码时该信号置一,该信号有效几个周期

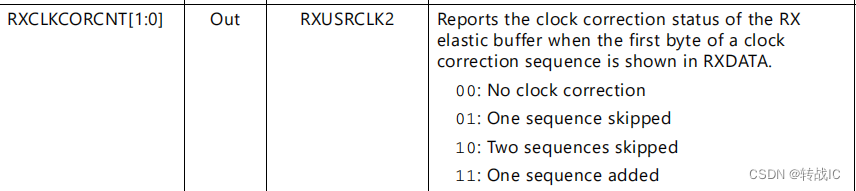

8.rxclkcorcnt_out[1:0]:也是一个状态信号,时钟矫正端口

6231

6231

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?