目录

2.3User data width、Internal data width和Encoding

前言

对GTH的IP 及架构讲解,会按照IP核设置的选项来进行依次讲解,并不是按照GTH的官方目录来长篇说明,觉得还是带着问题和不解来学习更加深刻~~,下面中有关GTH Transceiver的结构介绍是为了和其相对IP设置,因为在IP核设置的时候其相关的引脚和属性就已经被Vivado软件生成完成~~

注意:主要讲解通用的设置选项,advnaced的选项请自行查阅资料学习~

一、GTH transceiver 大概描述

对于不太熟悉GTH transceiver的同学,先简单介绍一些基础概念~~

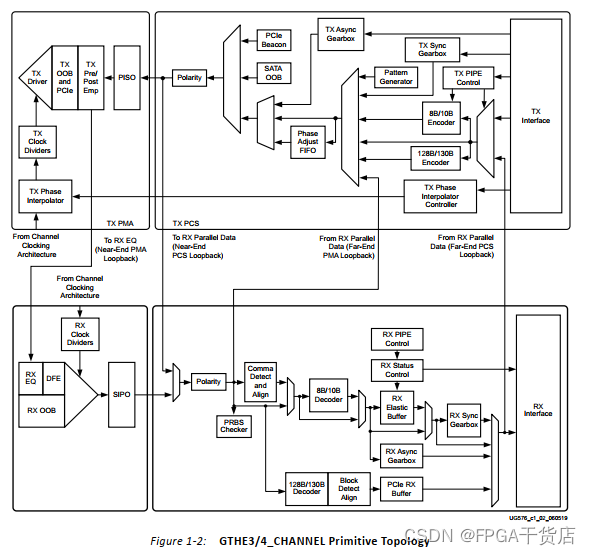

下图就是一个channel通道的TX和RX端的内部各结构框图,主要是由PCS和PMA两部分组成。

1.什么是Quad?

一个Quad包含四个GTH transeiversl通道,两个专用的参考时钟管脚和专用的南/北时钟路径。

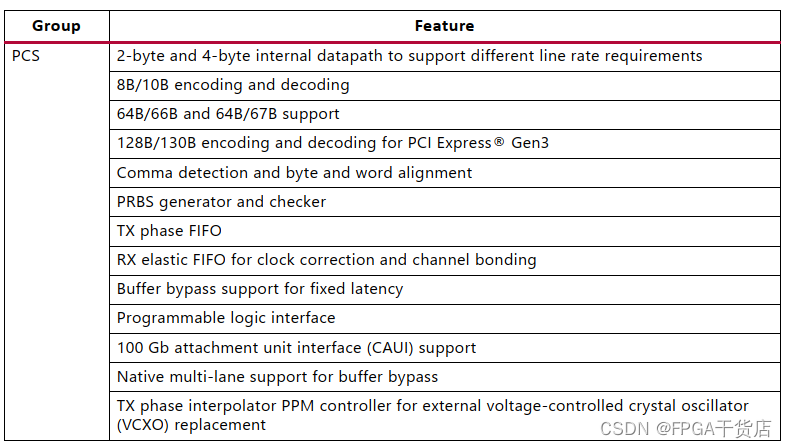

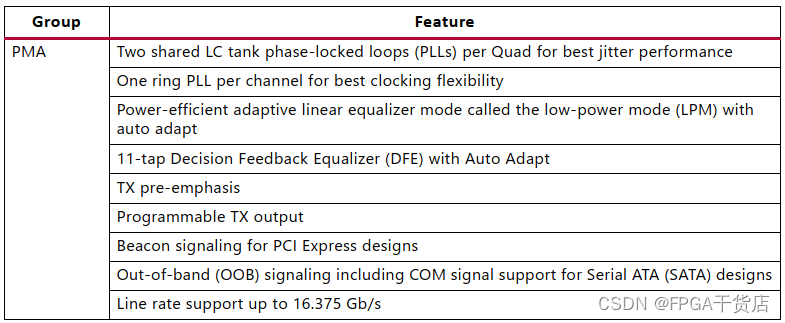

2.GTH 主要特性

废话不多说,干货在下面~~下面就对IP界面设置的选项及GTH内部对应结构进行说明,因为IP核的设置就会对应到GTH Transceiver的内部设置。

二、Basic 界面对应GTH结构说明

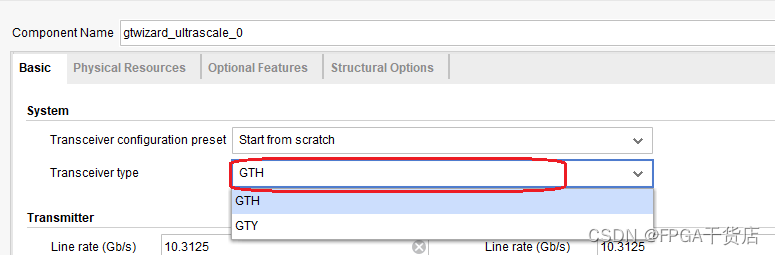

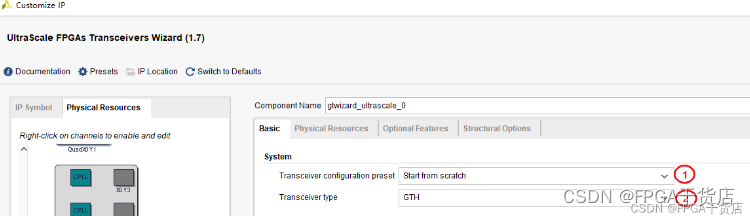

1.System设置选项

如下图所示,包含Transceiver configuration preset和Transceiver type这两个选项设置。

( 1)Transceiver configuration preset:

该选项用于设置GTH跑的协议类型,可以从下拉菜单中看到不同类型的协议。如果想自定义GTH的各选项,则就选择Start from scratch(默认)。

(2)Transceiver type

该选项用于设置tranceiver的类型,根据FPGA device型号的不同则可以选择GTH或是GTY;

2. Transmitter和Receiver

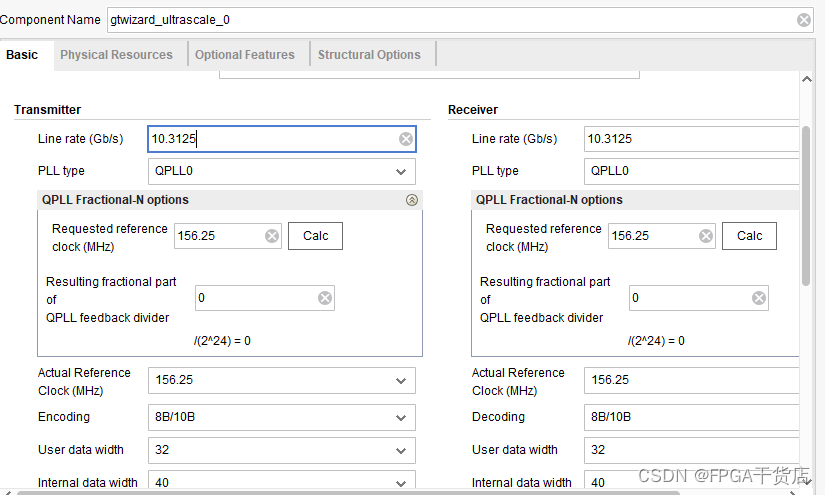

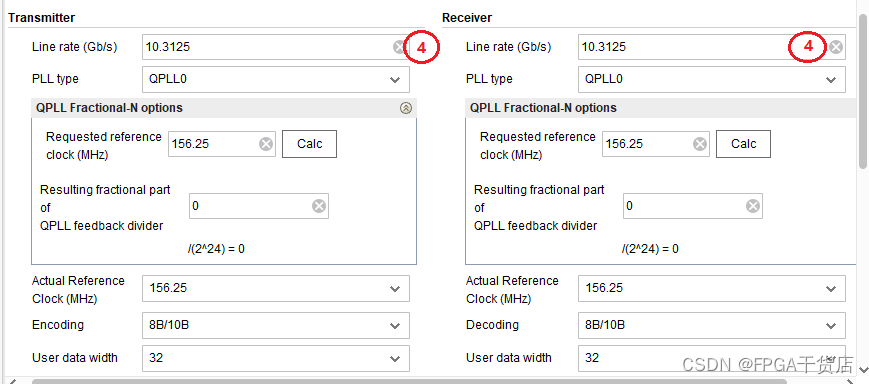

从下图可以看到Transmiiter和Receiver设置项相同但是可以分别设置,因此TX端和RX端可以根据应用的需求去设置不同,但一般情况TX和RX设置相同。

2.1Reference Clock

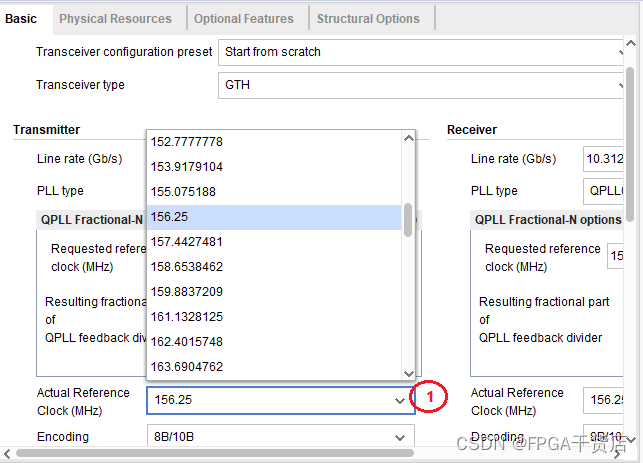

1.IP设置说明

如图中(1)所示,设置GTH的外部参考时钟频率,根据板卡的实际需求来进行设置;

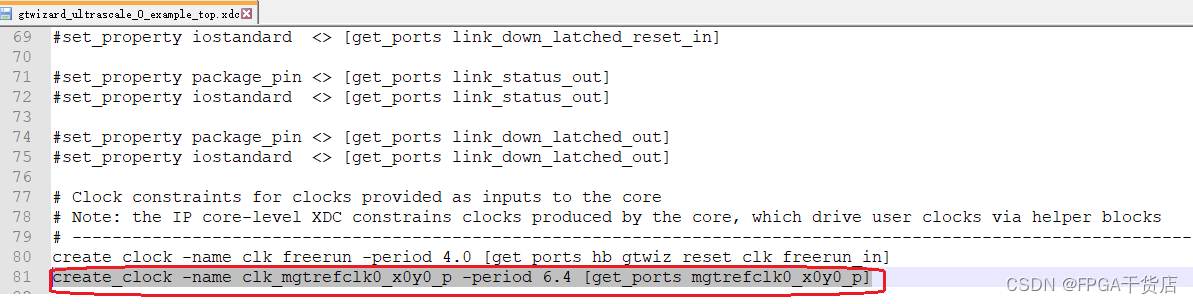

当将此IP核生成example 工程后,可以看到example的约束文件会对此参考时钟频率进行约束,如下图所示。

2.Reference Clock的结构说明

在GTH的uers guide手册中关于Reference Clock有两种运行模式:Input和Output(在IP中无体现)。

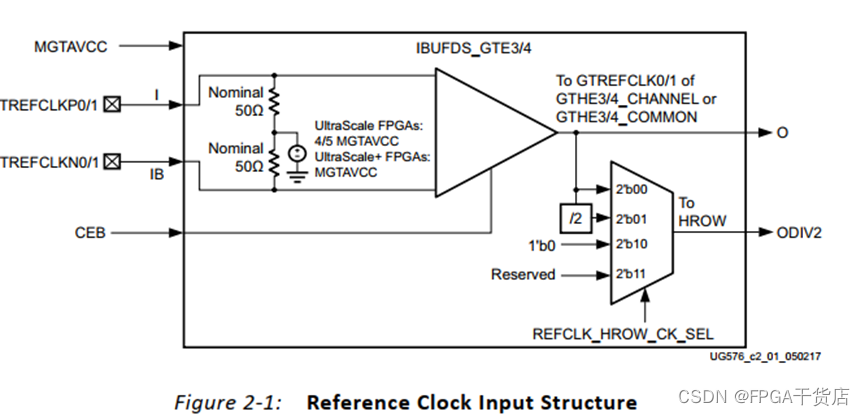

(1)Input输入模式:该时钟为外部输入的参考时钟,为了驱动QPLL/CPLL;输入的参考时钟进入IBUFDS_GTE3/4源语,如下图所示。

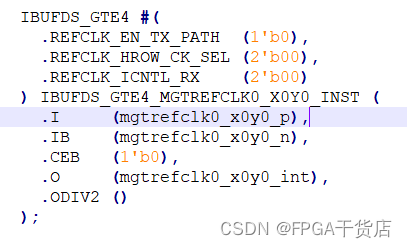

例化GTH的example后的顶层代码中都有该源语的使用,如下图所示。

其端口描述:

| 端口名 | 方向 | 时钟域 | 描述 |

| CEB | In | N/A | Clock buffer的时钟使能信号,拉高后该clock buffer 掉电 |

| I | In (pad) | N/A | 参考时钟输入管脚,映射到 GTREFCLK0P和GTREFCLK1P |

| IB | In (pad) | N/A | 参考时钟输入管脚,映射到 GTREFCLK0N和GTREFCLK1N |

| O | Out | N/A | 输出时钟信号 |

| ODIV2 | Out | N/A | 该信号可配置为O输出或是O的2分频输出时钟 |

其属性描述:

| 属性 | 类型 | 描述 |

| REFCLK_EN_TX_PATH | 2-bit Binary | 保留位,设置1’b0 |

| REFCLK_HROW_CK_SEL | 2-bit Binary | 配置ODIV输出: 2’b00:ODIV=O 2’b01:ODIV=O的2分频 2’b10:ODIV=1’b0 2’b11:保留 |

| REFCLK_ICNTL_RX | 2-bit Binary | 保留位,推荐使用Wizard设置的值 |

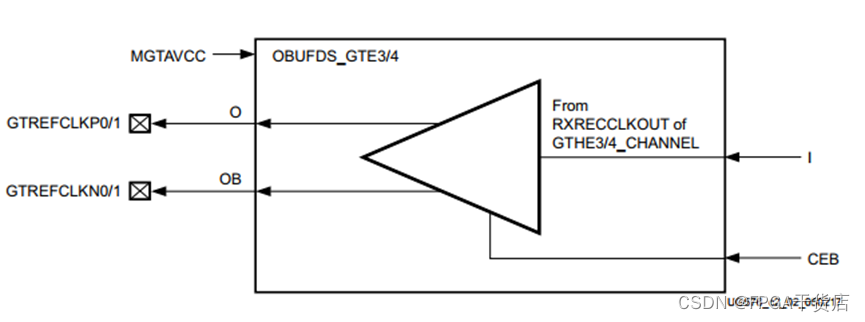

(2)Output输入模式:该时钟时由同一组Quad的中四个任意channel输出的恢复时钟RXRECCLKOUT输出给专用参考时钟I/O管脚,结构如下图所示。(没有找到相关的IP设置或是代码,文档中也没有找到相关的管脚信息)

该模式可以使用两个OBUFDS_GTE3/4 和 OBUFDS_GTE3/4_ADV源语中的一个输出参考时钟,具体使用哪个要根据你的应用来选择;

a.使用OBUFDS_GTE3/4 源语应用情况:

使用该源语是由于RXRECCLKOUT信号总是来自同一个channel,其结构如下图所示。

其端口描述:

| 端口名 | 方向 | 时钟域 | 描述 |

| CEB | In | N/A | Clock buffer的时钟使能信号,拉高后该clock buffer 掉电 |

| I | In | N/A | 恢复时钟输入管脚,与同一个Quad其中一个GTHE3/4_CHANNEL输出的RXRECCLKOUT连接 |

| O | Out | N/A | 输出参考时钟端口,映射到GTREFCLK0P和GTREFCLK1P |

| OB | Out | N/A | 输出参考时钟端口,映射到GTREFCLK0N和GTREFCLK1N |

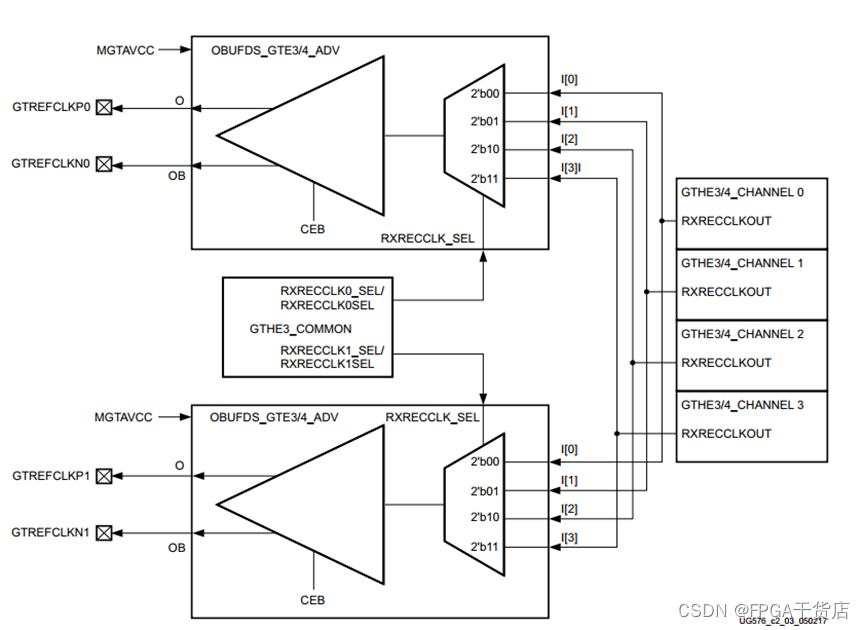

b.使用OBUFDS_GTE3/4 源语应用情况:

使用该源语是由于在runtime时改变所使用RXRECCLKOUT的通道;当使用这个源语时GTHE3/4_COMMON源语也必须例化,其结构如下图所示。

其端口描述:

| 端口名 | 方向 | 时钟域 | 描述 |

| CEB | In | N/A | Clock buffer的时钟使能信号,拉高后该clock buffer 掉电 |

| I[3:0] | In | N/A | 恢复时钟输入管脚,

|

| O | Out | N/A | 输出参考时钟端口,映射到GTREFCLK0P和GTREFCLK1P |

| OB | Out | N/A | 输出参考时钟端口,映射到GTREFCLK0N和GTREFCLK1N |

| RXRECCLK_SEL[1:0] | In | Async | RXRECCLKOUT的时钟选择 |

2.2PLL Type

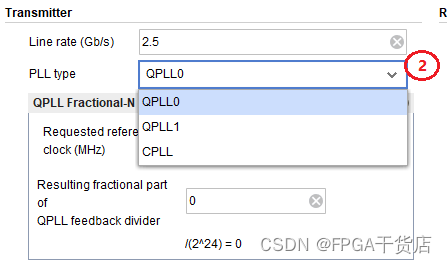

如上图所示,在IP选项中PLL类型的选择一共有三种:CPLL、QPLL0和QPLL1。但是会发现当Line rate设置不同的时候,该选项的下拉菜单会有不同,这是由于不同PLL支持的范围不同。

- CPLL支持工作范围在2.0GHz~6.5GHz;

- QPLL0支持工作范围在9.8GHz~16.375Hz;

- QPLL1支持工作范围在8.0GHz~13.0GHz

接下来分别介绍CPLL和QPLL0/1的结构:

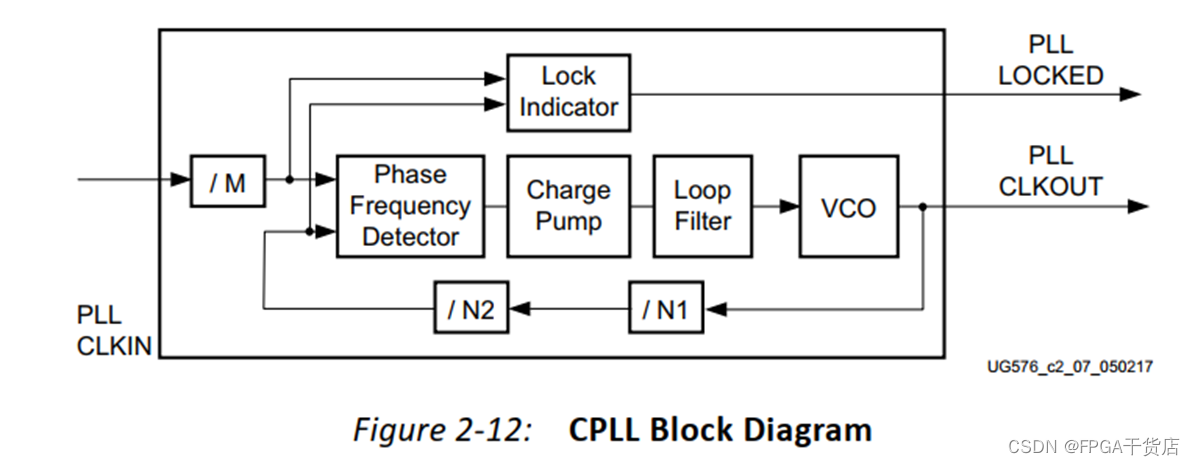

1.CPLL

CPLL结构如下图所示。在进入到phase frequency detector之前对输入进来的时钟M分频处理,反馈分频器N1和N2决定了VCO的倍增比和CPLL的输出频率。lock indicator block用于比较输入参考时钟和VCO反馈时钟判定频率锁存是否完成。

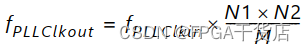

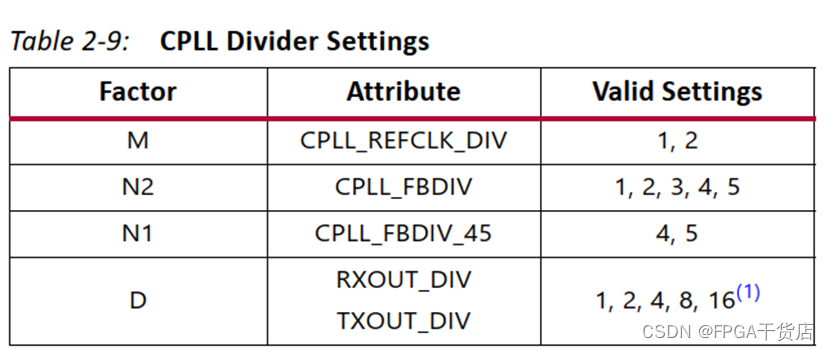

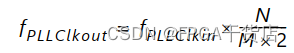

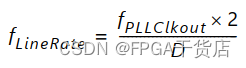

CPLL输出的频率(GHz)是由以下公式决定:

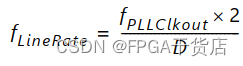

以下公式决定线速率line Rate(Gb/s):

上述公式中的参数如下: 当遇到这些公式时,心里就会想如果想要达到怎样速率,频率是否还要计算,放心这些Xilinx IP都已帮助完成,只要在IP 界面中选择所需使用的PLL和速率就可以。

当遇到这些公式时,心里就会想如果想要达到怎样速率,频率是否还要计算,放心这些Xilinx IP都已帮助完成,只要在IP 界面中选择所需使用的PLL和速率就可以。

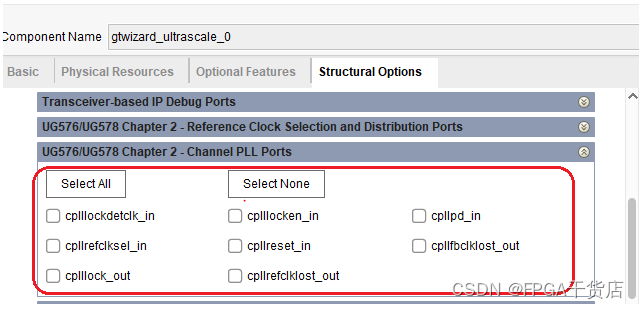

其端口描述:

| 端口 | 方向 | 时钟域 | 描述 |

| CPLLLOCKDETCLK | In | Clock | 该时钟是一个稳定时钟用于检测反馈和参考时钟信号,输入到CPLL参考时钟和从CPLL输出的时钟一定不要驱动该时钟; |

| CPLLLOCKEN | In | Aysnc | 用于使能CPLL lock 检测。当使用CPLL时该端口总是拉高,否则拉低避免CPLLLOCK输出 |

| CPLLPD | In | Aysnc | 拉高则power down和reset CPLL |

| CPLLREFCLKSEL | In | Aysnc | CPLL输入参考时钟选择。当改变CPLL输入参考时钟要进行复位操作; 000: Reserved |

| CPLLRESET | In | Aysnc | 保留,CPLL使用CPLLPD复位 |

| CPLLFBCLKLOST | Out | CPLLLOCKDETECLK | 拉高表示来自CPLL feedback divider的反馈时钟到phase frequency detector 是丢失 |

| CPLLLOCK | Out | Aysnc | CPLL锁存信号 |

| CPLLREFCLKLOST | Out | CPLLLOCKDETECLK | 拉高表输入到CPLL phase frequency detector 参考时钟是丢失 |

上面中的端口信号都可以在IP的端口中显示出来,需要的化在下面的界面中打勾选择即可。

其属性描述:

| 端口 | 类型 | 描述 |

| CPLL_FBDIV | Integer | CPLL的N2值设置,可设置1,2,3,4,5 |

| CPLL_FBDIV_45 | Integer | CPLL的N1设置,可设置4和5 |

| CPLL_REFCLK_DIV | Integer | CPLL 的M设置,可设置1和2 |

| RXOUT_DIV | Integer | RX路径CPLL输出时钟分频D的值,可设置1,2,4,8 |

| TXOUT_DIV | Integer | TX路径CPLL输出时钟分频D的值,可设置1,2,4,8 |

2.QPLL

每个Quad包含两个QPLL,任何一个QPLL可与同Quad的channel共享,但不能与其他的Quad共享。 以下是QPLL0/1内部结构图。输出到QPLL0/1的时钟经过M分频输入到phase frequency detector,反馈分频N决定了VCO的倍增系数。QPLL0/1输出时钟频率时VCO频率的一半。lock indicator模块比较输入参考时钟与VCO时钟决定时钟锁存是否完成。

以下公式用于计算QPLL0/1输出频率:

以下公式用于计算线速率line rate(Gb/s)

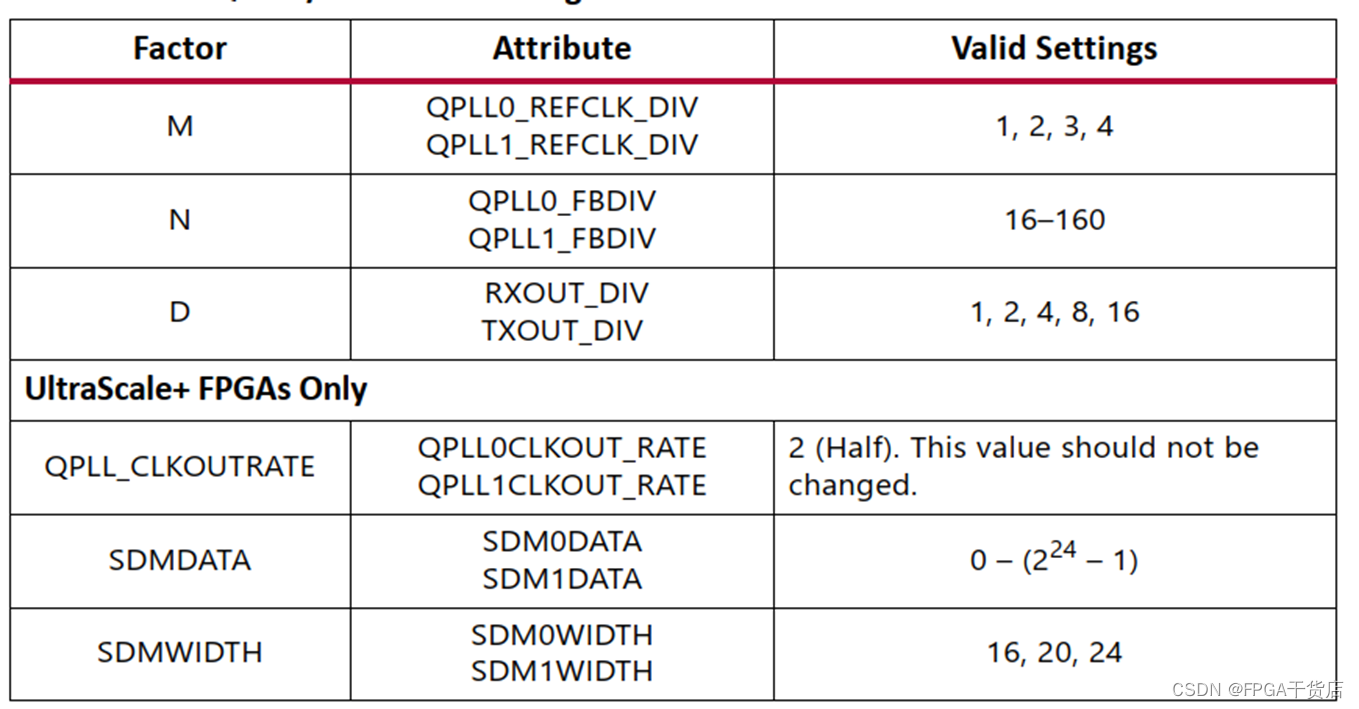

上述公式中的参数如下:

同样这些频率是不需要计算,这些Xilinx IP都已帮助完成,只要在IP 界面中选择所需使用的PLL和速率就可以。

其端口描述:

| 端口 | 方向 | 时钟域 | 描述 |

| QPLLDMONITOR0[7:0]/ | Out | Aysnc | 保留 |

| QPLL0CLKRSVD0/ | In | 保留,设置1’b0 | |

| QPLL0CLKRSVD1/QPLL1CLKRSVD1 | In | 保留,设置1’b0 | |

| QPLL0FBCLKLOST/QPLL1FBCLKLOST | Out | QPLL0LOCKDETCLK/ QPLL1LOCKDETCLK | 拉高表示从QPLL0/1反馈回来的反馈时钟在输入到 Phase frequency detector 丢失 |

| QPLL0LOCK/QPLL1LOCK | Out | Aysnc | 拉高表示QPLL0/1时钟频率已锁存 |

| QPLL0LOCKDETCLK/ | In | Clock | 该时钟是一个稳定时钟用于检测反馈和参考时钟信号,输入到QPLL0/1参考时钟和从QPLL0/1输出的时钟一定不要驱动该时钟; |

| QPLL0LOCKEN/ | In | Aysnc | 该端口用于使能QPLL0/1lock检查。 |

| QPLL0OUTCLK/ | Out | N/A | QPLL0/1输出时钟,分别将连接QPLL0/1OUTCLK到GTHE3/4_CHANNEL primitive的QPLL0/1CLK |

| QPLL0OUTREFCLK/ QPLL1OUTREFCLK | Out | N/A | QPLL0/1输出参考时钟,分别将连接QPLL0/1OUTREFCLK到GTHE3/4_CHANNEL primitive的QPLL0/1REFCLK |

| QPLL0PD/QPLL1PD | In | Aysnc | 拉高则将QPLL0/1 power down |

| QPLL0REFCLKLOST/ | Out | QPLL0LOCKDETCLK/ QPLL1LOCKDETCLK | 拉高则表示输入到QPLL0/1的phase frequency detector参考时钟丢失 |

| QPLL0REFCLKSEL[2:0]/ | In | Aysnc | QPLL0/1输入参考时钟的动态选择,在改变完参考时钟输入后要复位QPLL0/1 |

| QPLL0RESET/QPLL1RESET | In | Aysnc | 拉高则表示复位QPLL0/1 |

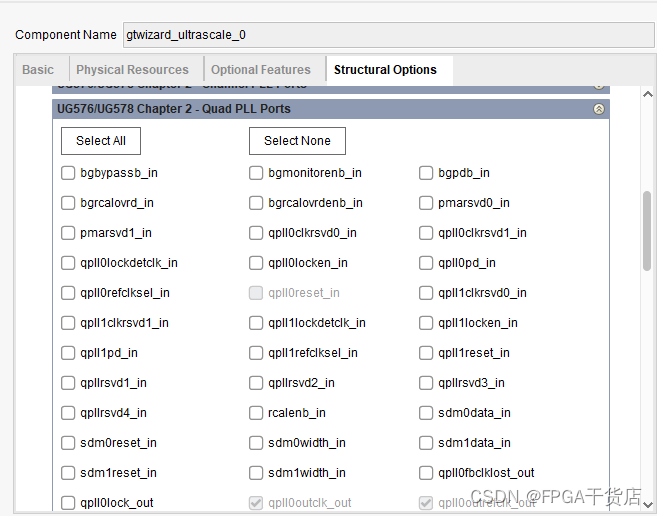

同样,上面中的端口信号都可以在IP的端口中显示出来,需要的话在下面的界面中打勾选择即可。

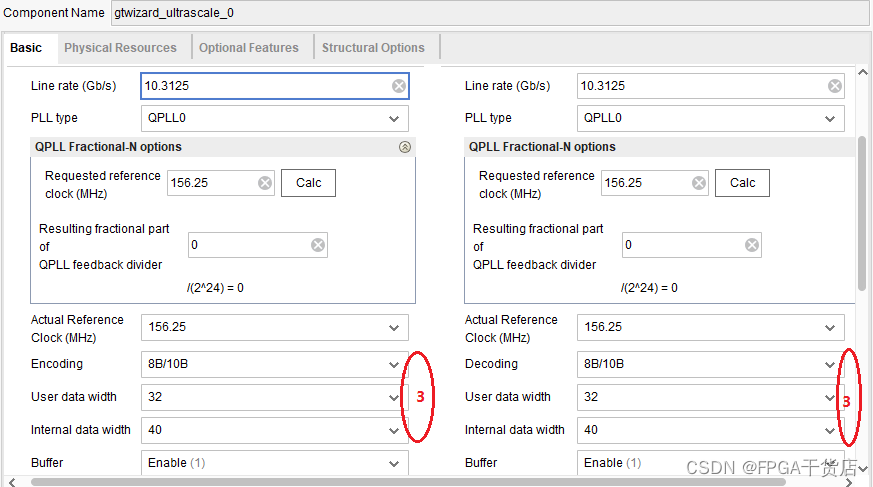

2.3User data width、Internal data width和Encoding

将这三个选项放在一起是他们彼此互相有关联,那么先说明下这三个选项:

User data width:指的是用户接口TX/RX的位宽;

Internal data width:指的是GTH transceiver的内部接口TX/RX数据宽度;

Encoding:指的是GTH传输的数据是否选择编码,如果需要编码选择对应的编码规则。

其对应到GTH 的结构为TX interface/RX interface。以上的这三个选项设置都会对应到GTH 内部的端口和属性上。

1.TX端:

(1)TXDATA端口是用户端口,可以设置2bytes、4bytes或是8bytes;

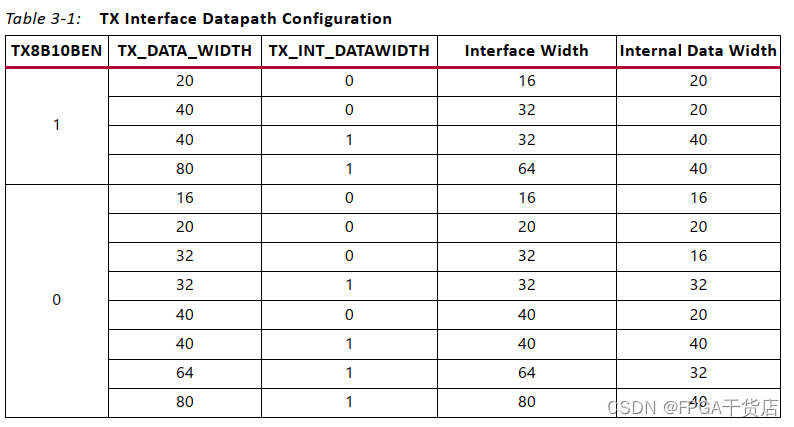

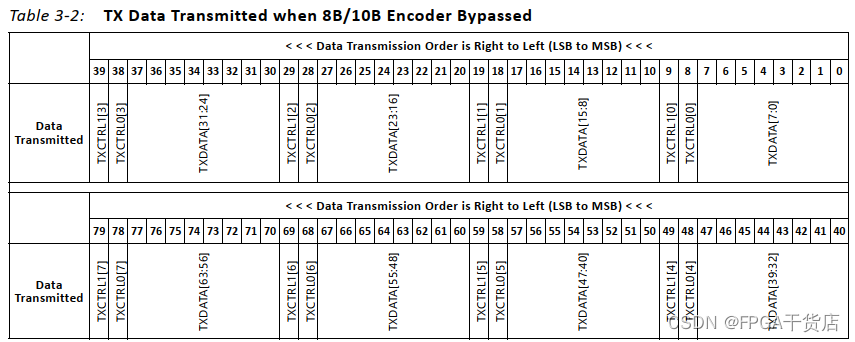

然而这个端口的实际数据宽度是由TX_DATA_WIDTH属性、TX_INT_DATAWIDTH属性和TX8B10BEN端口一起决定的,因此实际数据位宽可以设置为 16, 20, 32,40, 64, 和 80 bits,那么扩充出来的位宽是由TXCTRL1 和TXCTRL0这两个端口进行填补。

举例子:

如果8B10B使能bypass时,TX_DATA_WIDTH设置为40,则interface width位宽为40bit,但实际只使用TXDATA[31:0],其他位宽由TXCTRL1 和TXCTRL0扩充到40bit。

(2)下表为TX_DATA_WIDTH属性、TX_INT_DATAWIDTH属性和TX8B10BEN端口决定各接口位宽。从表中可以看出当TX8B10BEN使能时,interface width不需要扩充,但是当TX8B10BEN不使能时,则interface width宽度有20bit,40bit和80bit,则此时需要将数据位宽进行扩充。

(3) 下图为TX data的数据形式:

(4)端口描述:

| 端口 | 方向 | 时钟域 | 描述 |

| TXCTRL0[15:0]/ | In | TXUSRCLK2 | 当8B/10B不使能,TXCTRL0用于扩展数据总线20,40,80bits,其中[15:8]不用 |

| TXDATA[127:0] | In | TXUSRCLK2 | 发送数据总线,其位宽由TX_DATA_WIDTH决定 TX_DATA_WIDTH=16,20 TXDATA[15:0]=16bits宽度 TX_DATA_WIDTH=32,40 TXDATA[31:0]=32bits宽度 TX_DATA_WIDTH=64,80 TXDATA[63:0]=16bits宽度 |

| TXDATAEXTENDRSVD | In | Async | 保留 |

| TXUSRCLK | In | Clock | 用于TX PCS的路径时钟 |

| TXUSRCLK2 | In | Clock | 用用户逻辑时钟 |

属性描述:

| 端口 | 类型 | 描述 |

| TX_DATA_WIDTH | Integer | 设置TXDATA位宽 |

| TX_INT_DATAWIDTH | Integer | internal datapath控制宽度 0:2byte internal datapath 1:4byte internal datapath 如果线速率超过8.1875Gb/s,则应设置为1. |

| TX_FABINT_USRCLK_FLOP | 1-Bit | 决定是否端口信号需要在TXUSRCLK时钟域再次寄存。该属性只是应用TX internal datapathwidth和TX interface width宽度一样,否则被忽略。 |

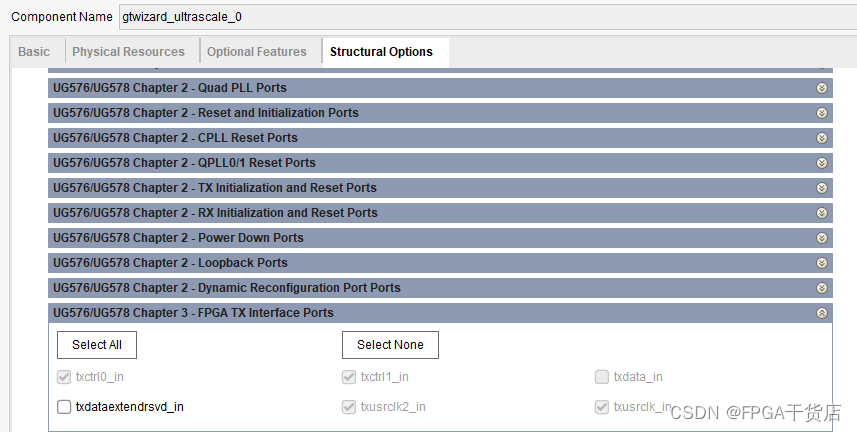

在IP核中可以选择其端口是否打开,如下图所示。

2.RX端:

2.RX端:

与TX端的描述一致,可自行查阅资料阅读。

2.4Line rate(Gb/s)

1.IP设置说明

根据实际应用的速率填写线速率Line rate值。

2.TXUSRCLK/2和RXUSRCLK/2

该线速率Line rate设置会影响TXUSRCLK和RXUSRCLK的速率,公式如下:

![]()

![]()

这里面的Line Rate就是IP核中设置的速率;Internal Datapath width就是2.3章节中IP中的设置,由此就可以计算出 TXUSRCLK和RXUSRCLK的速率;

那么分别对TXUSRCLK/2和RXUSRCLK/2说明:

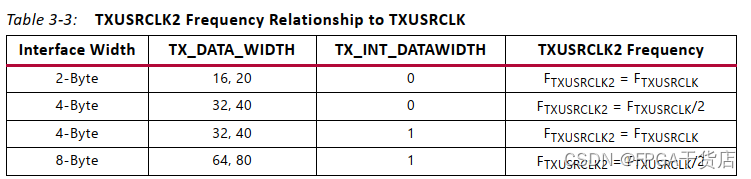

3.TXUSRCLK/2

(1) TX接口包含两个并行时钟:TXUSERCLK和TXUSRCLK2。其中TXUSRCLK用于GTH Transceiver的PCS的逻辑,他的速率时由GTHE3/4_CHANNEL primitive 的internal datapath width宽度和TX line rate线速率一起决定的。计算的公式如下:

![]()

TXUSRCLK2时钟用于信号需要同步到GTH Transeiver TX端(也就是所谓的用户时钟,是我们关心的时钟),也就是输入到IP TX端的信号被在TXUSRCLK2时钟上升沿采样。

TXUSERCLK和TXUSRCLK2有固定的速率关系。他是由TX_DATA_WIDTH和TX_INT_DATAWIDTH共同决定。以下表格就显示了具体的关系。

TXUSERCLK和TXUSRCLK2应遵守以下几条规定:

- TXUSERCLK和TXUSRCLK2必须在上升沿对齐,只允许由轻微的抖动。因此BUFG_GT必须用于驱动TXUSERCLK和TXUSRCLK2;

- TXUSERCLK和TXUSRCLK2和外部参考时钟都是来自同样时钟源;

(2) 那么TUSRCLK/2来自哪里?

TXOUTCLK 用于驱动TXUSRCLK 和TXUSRCLK2时钟,根据以下情况分为以下几种情况:

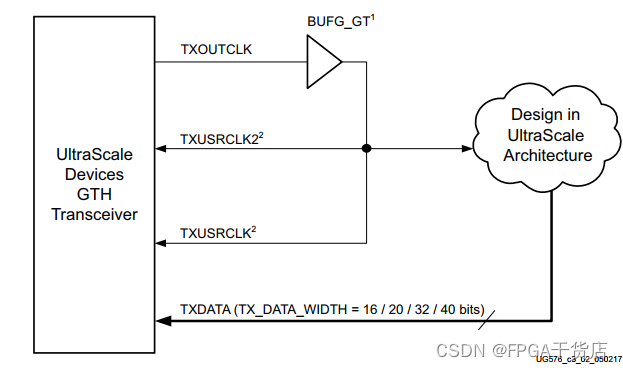

a)当user data位宽小于或是等于intenal data位宽, TXOUTCLK经过BUFG_GT直接输出给TXUSRCLK 和TXUSRCLK2时钟,则TXUSRCLK =TXUSRCLK2;

当GTH IP生成example综合编译完成后,可以在综合界面tcl窗口输入report_clocks可以看到约束TXOUTCLK的时钟频率;

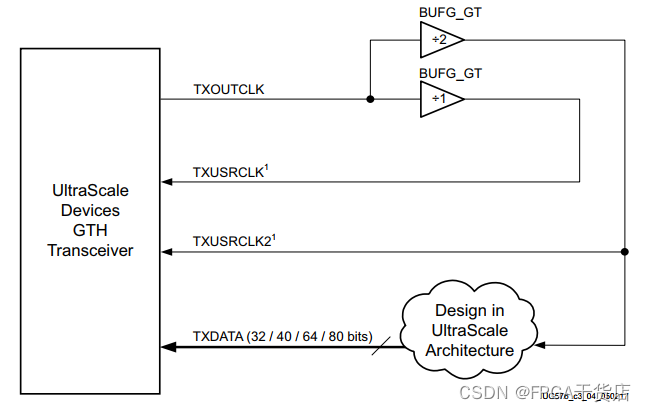

b) 当user data位宽大于intenal data位宽, TXOUTCLK分别经过两个BUFG_GT直接输出TXUSRCLK 和TXUSRCLK2时钟,此时TXUSRCLK =2TXUSRCLK2;

4.RXUSRCLK/2

RXUSERCLK/2和上述的TXUSRCLK的结构内容基本一致,但是有几点规则不太一样:

1.如果发送和接收的通道使用的参考时钟来自同一个晶振,则也可以使用TXOUTCLK用于驱动RXUSRCLK和RXUSRCLK2的时钟;

2.当送和接收的通道使用独立的参考时钟而且时钟校正没有使用,那么RXUSRCLK和RXUSRCLK2的时钟必须要由RXOUTCLK驱动;

2.5TXOUTCLK/RXOUTCLK

1.IP选项设置说明

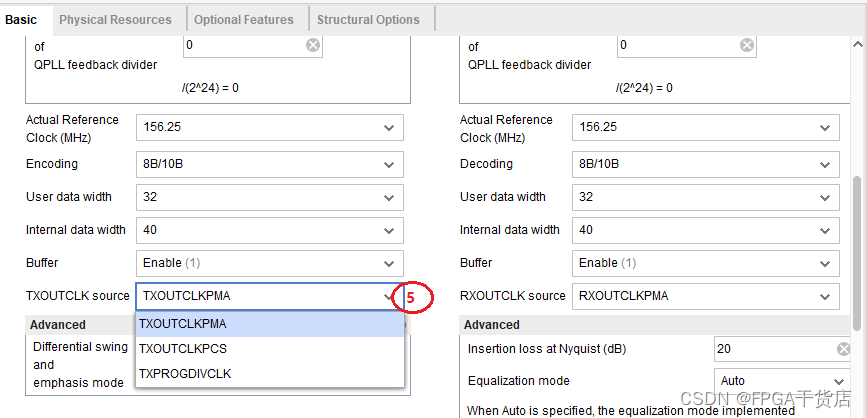

该选项用于选择TXOUTCLK的时钟源,选择TXOUTCLKPMA,那么我们就看下为什么要选择此时钟作为TXOUTCLK的时钟源?

2.TXOUTCLK的时钟源

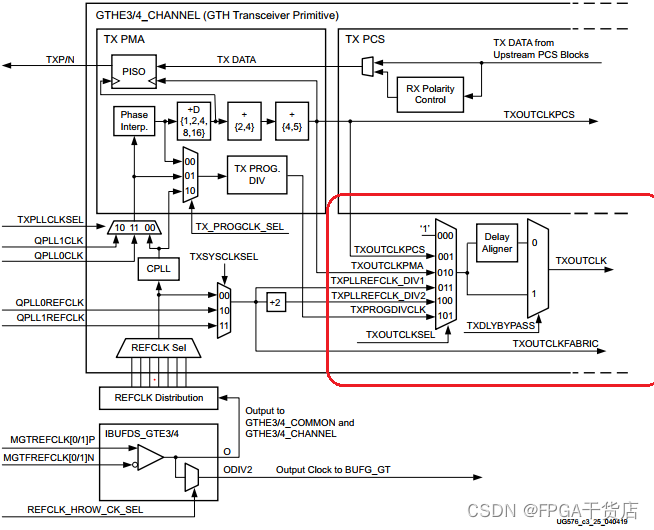

以下框图 TX端的时钟产生结构框图。

可以看到TXOUTCLK是根据TXOUTCLKSEL的选择输出的,输入到多路选择时钟主要有以下:

1)TXOUTCLKPCS:(TXOUTCLKSEL = 3'b001)一般不推荐使用该时钟使用,因为来自PCS block会额外增加延时;

2)TXOUTCLKPMA:(TXOUTCLKSEL = 3'b010)该时钟被TX PCS模块使用,当PLL的任何一个复位信号复位则该时钟就会被中断;

3)TXPLLREFCLK_DIV1或 TXPLLREFCLK_DIV2:(TXOUTCLKSEL = 3'b011 或是3'b100)这两个是输入CPLL或QPLL的参考时钟;

4)TXPROGDIVCLK:(TXOUTCLKSEL = 3'b0101)该时钟有在TX Programmable Divider后输出的分频时钟。

因此在GTH user guide中推荐也是使用TXOUTCLKPMA时钟作为TXOUTCLK的时钟源。

则对应的GHT IP接口如下图所示,可以根据需要选择对应的接口显示。

3.RXOUTCLK的时钟源

3.RXOUTCLK的时钟源

和TXOUTCLK时钟章节的结构类似,可以参考文档学习。

本文详细解读了GTH transceiver的基础设置,包括Quad的概念、GTH特性、PLL类型选择、用户数据宽度设置及其对应结构。重点介绍了System设置、Transmitter/Receiver选项,如参考时钟、PLL类型、编码选择等,并配以实例说明和结构图解析。

本文详细解读了GTH transceiver的基础设置,包括Quad的概念、GTH特性、PLL类型选择、用户数据宽度设置及其对应结构。重点介绍了System设置、Transmitter/Receiver选项,如参考时钟、PLL类型、编码选择等,并配以实例说明和结构图解析。

3605

3605

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?