Kmap1

要求:实现下面卡诺图所描述的电路。

module top_module(

input a,

input b,

input c,

output out );

assign out = a | b | c;

endmoduleKmap2

要求:实现下面卡诺图所描述的电路。

提示:尝试化简卡诺图。

module top_module(

input a,

input b,

input c,

input d,

output out );

assign out = (~b & ~c) | (~a & ~d)

| (b & c & d) | (a & c & d);

endmoduleKmap3

要求: 实现下面卡诺图所描述的电路。

提示:尝试化简卡诺图。

module top_module(

input a,

input b,

input c,

input d,

output out );

assign out = a | (~b & c);

endmoduleKmap4

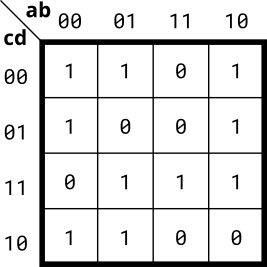

要求: 实现下面卡诺图所描述的电路。

提示:尝试化简卡诺图。(这里的卡诺图没有相邻的最小项,已经是最简形式了)

module top_module(

input a,

input b,

input c,

input d,

output out );

assign out = (~a & ~b & ~c & d) | (~a & ~b & c & ~d)

| (~a & b & ~c & ~d) | (~a & b & c & d)

| (a & b & ~c & d) | (a & b & c & ~d)

| (a & ~b & ~c & ~d) | (a & ~b & c & d);

endmoduleMinimum SOP and POS(Exams/ece241 2013 q2)

要求:具有四个输入(a、b、c、d)的单输出数字系统在输入上出现 2、7 或 15 时生成逻辑 1,当输入上出现 0、1、4、5、6 时生成逻辑 0 、9、10、13 或 14 出现。数字 3、8、11 和 12 的输入条件在此系统中永远不会出现。 例如,7 对应于 a、b、c、d 分别设置为 0、1、1、1。确定最小项之和形式的输出out_sop,以及最大项之积形式的输出out_pos。

根据要求画出对应的卡诺图并化简,输入为 3、8、11 和 12 为无关项,在化简卡诺图时,无关项可以是1也可以是0。

module top_module (

input a,

input b,

input c,

input d,

output out_sop,

output out_pos

);

assign out_sop = (c & d) | (~a & ~b & c);

assign out_pos = c & (~a | b | ~c) & (~b | ~c | d);

endmodule

Karnaugh map(Exams/m2014 q3)

要求: 实现下面卡诺图所描述的电路。

提示:尝试化简卡诺图。(d为无关项)

module top_module (

input [4:1] x,

output f );

assign f = (x[2] & x[4]) | (x[3] & x[4]) | (~x[1] & x[3] & ~x[4]);

endmoduleKarnaugh map(Exams/2012 q1g)

module top_module (

input [4:1] x,

output f

);

assign f = (~x[1] & x[3]) | (~x[1] & ~x[2] & ~x[4])

| (x[2] & x[3] & x[4]) | (x[1] & ~x[2] & ~x[4]);

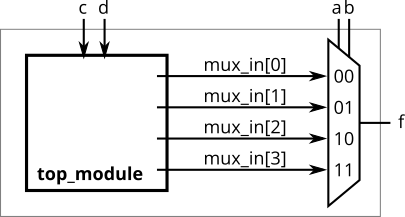

endmoduleK-map implemented with a multiplexer(Exams/ece241 2014 q3)

要求:如下图所示,c、d为top_module的输入,a、b为选择器的选择信号,实现下图的卡诺图所描述的功能,不允许使用逻辑门。

module top_module (

input c,

input d,

output [3:0] mux_in

);

assign mux_in[0] = d ? 1'b1 : c;

assign mux_in[1] = 1'b0;

assign mux_in[2] = d ? 1'b0 : 1'b1;

assign mux_in[3] = c ? d : 1'b0;

endmodule总结:本节是根据卡诺图来描述电路,要学会卡诺图的化简方法。

79

79

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?