电源输出电容一般是100 nF至100 μF的陶瓷电容,它们耗费资金,占用空间,而且,在遇到交付瓶颈的时候还会难以获得。所以,如何最大限度减小输出电容的数量和尺寸,这个问题反复被提及。

输出电容造成的影响

论及此问题,输出电容的两种影响至关重要:对输出电压纹波的影响,以及在负载瞬变后对输出电压的影响。

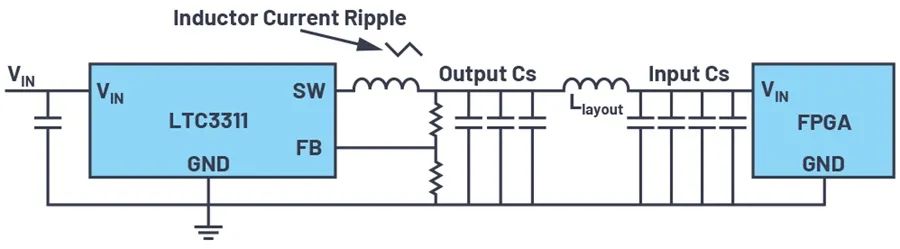

首先,我们来看一看输出电容这个词。这些电容一般安装在电源的输出端。但是,许多电力负载(电力消耗对象),例如FPGA,都需要使用一定数量的输入电容。图1显示的是一种典型的包含负载和FPGA的电源设计。如果在电路板上,电压生成电路和耗电电路之间的距离非常短,那么电源输出电容和负载输入电容之间的界限就会变得非常模糊。

图1. LTC3311 开关稳压器,包含所连接的FPGA对应的输出电容和输入电容。

通常需要利用某种物理分隔方法来加以区分,而这会导致产生大量寄生电感(Llayout)。

电源输出端的电容形成决定了降压型&#

评论

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?

查看更多评论

添加红包

本文探讨了如何在电源设计中减少输出电容的数量和尺寸,关注电容对输出电压纹波和负载瞬变响应的影响。通过分析电容的物理布局、使用模拟工具如LTspice进行仿真,以及利用自适应电压定位(AVP)和优化控制环路速度,可以有效减少电容需求,降低成本和占用空间。

本文探讨了如何在电源设计中减少输出电容的数量和尺寸,关注电容对输出电压纹波和负载瞬变响应的影响。通过分析电容的物理布局、使用模拟工具如LTspice进行仿真,以及利用自适应电压定位(AVP)和优化控制环路速度,可以有效减少电容需求,降低成本和占用空间。

订阅专栏 解锁全文

订阅专栏 解锁全文