本文主要内容:

1、 线间串扰产生的原因

2、 传输线串扰产生的一般要求

3、 各类传输线仿真

4、 总结:如何减少PCB设计中的串扰。

一、线间串扰产生的原因

1、原因

当线与线之间平行布线时,两线之间会会产生一个寄生电容C,寄生电容的大小可用下列公式表示

C=εS/d

注释:ε为极板间介质的介电常数,S为极板面积,d为极板间的距离

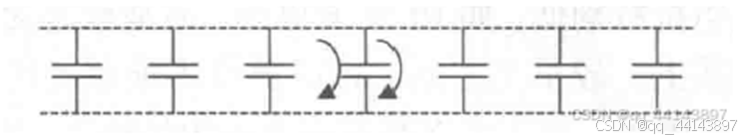

此时两线之间的模型等效如下图所示

上图可以理解为两线之间的感应电容。

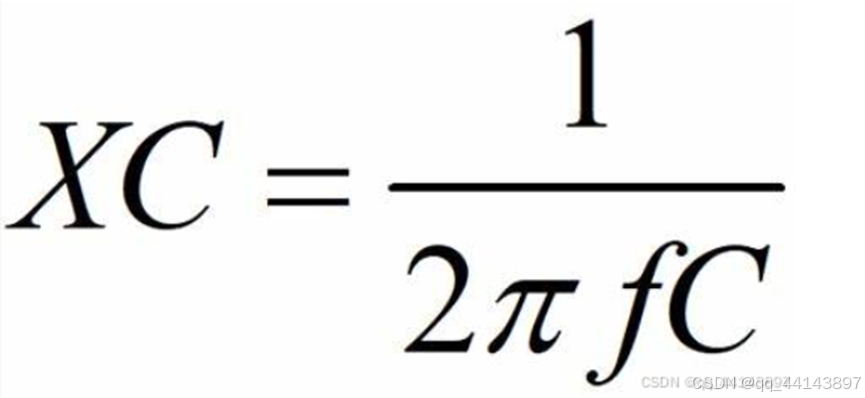

由此得到电容 C的容抗公式为

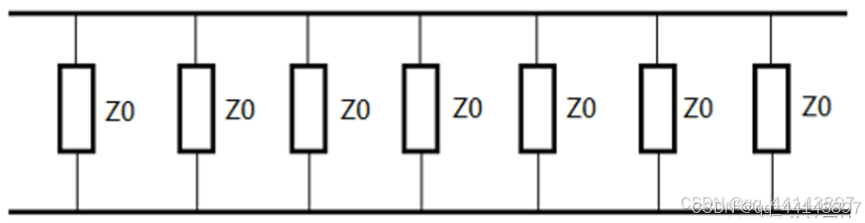

此时两线之间的等效模型如下图所示

此时在在两线上存在对方的感应耦合信号大小和这个电阻有关系,当电阻越大时,感应信号越小,对该传输线上的信号干扰也就越小,反之干扰则越大。

由电容的容抗公式可知

当信号频率固定的条件下,C越小,Xc越大,干扰越小,反之干扰越大。

再由电容的公式C=εS/d可知,干扰越小,则要求间距d越大。

从另一方面来说,由容抗公式可知,当频率越高时,要保证容抗Xc足够大,C就要足够小,对两线之间间距d的要求就越大。

二、传输线串扰产生的一般要求

噪声容限通常站信号电压摆幅的15%,但器件类型不同,具体情况也不同。在这15%中大约1/3即信号的5%是与串扰有关的(此为经验总结出来的)。例如,如果信号的摆幅是3.3V,所分配的最大串扰为160mV。

假如有两个攻击线将噪音耦合到同一条受害线上,考虑最坏的情况(假如两个噪音时序一样),这条受害线的总噪声将为两个总噪声之和。假如这两个噪声的大小时序都相同,则每一对之间的最大容许噪声为1/2*5%=2.5%。

(注:噪声容限表示不影响信号高低电平正常判断的允许最大的噪声值。)

三、 仿真

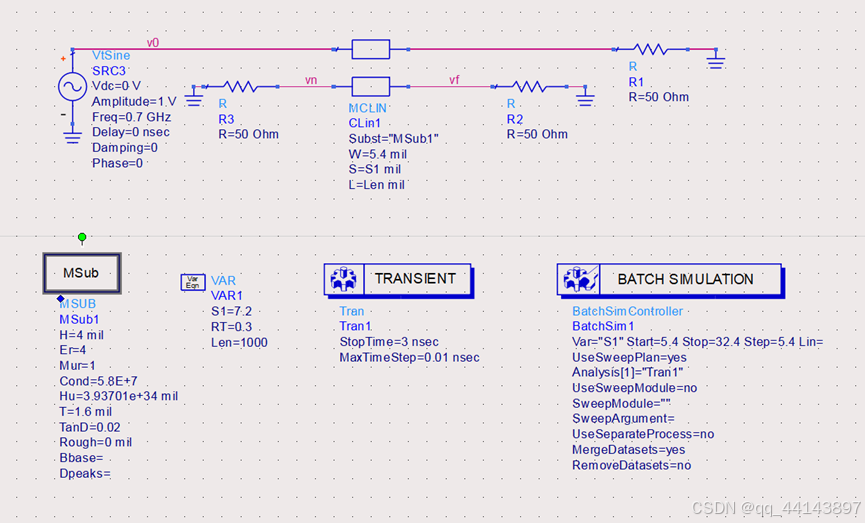

仿真一:传输线(微带线)间距对串扰的影响

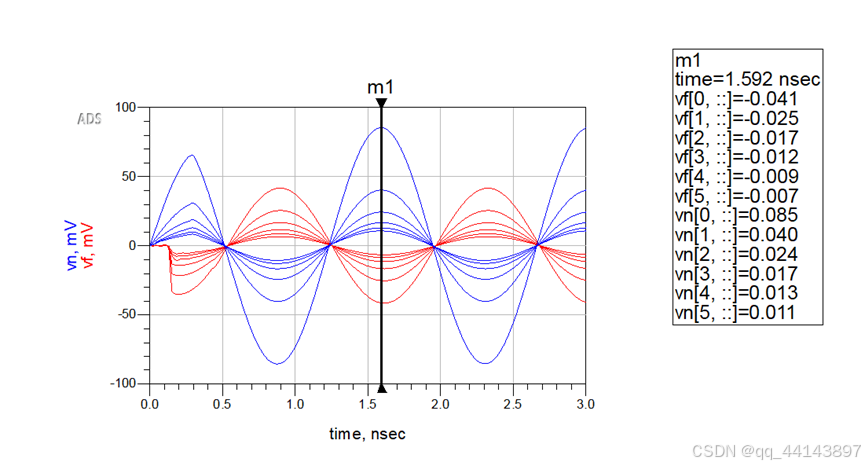

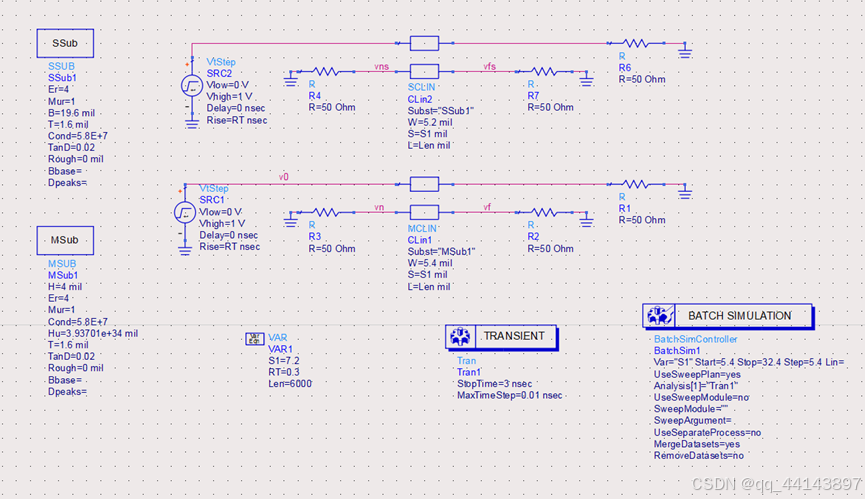

1、 信号幅值为1V,频率700MHz的周期信号,耦合长度为1000mil,线宽5.4,两线间距与串扰之间的关系,从1倍线宽到6倍线宽情况

由上面可知,条件频率为1Ghz,幅值为1V,两线耦合长度1000mil,两线之间的噪声与信号的占比如下图所示

线间距1倍线宽:0.041/1*100%=4.1%

线间距2倍线宽:0.025/1*100%=2.5%

线间距3倍线宽:0.017/1*100%=1.7%

线间距4倍线宽:0.012/1*100%=1.2%

线间距5倍线宽:0.009/1*100%=0.9%

线间距6倍线宽:0.007/1*100%=0.7%

由此可见,在该条件下,3W原则一般可以满足设计要求。

**结论:**当线间距越宽时,两线之间的串扰越小,符合上面的推断。干扰最坏情况下,当频率超过700MHz,或者耦合长度超过1000mil时,3W原则将不满足要求,此时应尽量加大线间距。

一般情况下,对于高速信号来说,为了尽量减少两线之间的干扰,有条件的情况下尽量拉开线间距,一些关键信号,如时钟信号,差分信号则要求5倍间距甚至更宽。

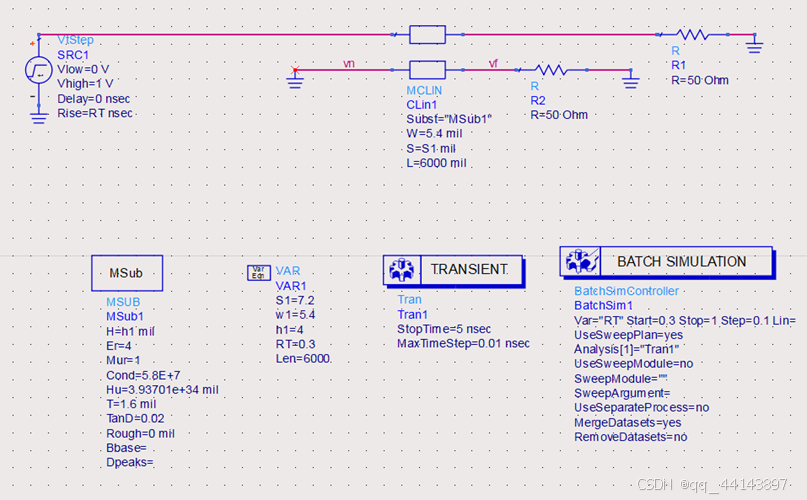

仿真二:激励源上升时间对串扰的影响

本章内容与PCB设计布局关系不大,仅作了解,不在详细叙述。

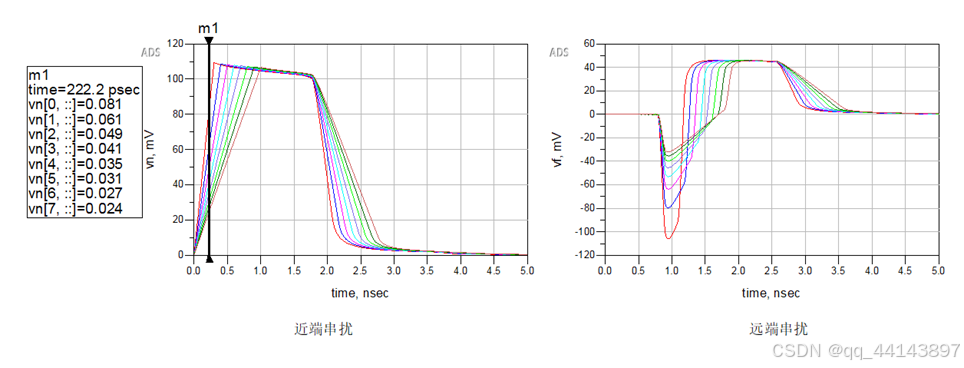

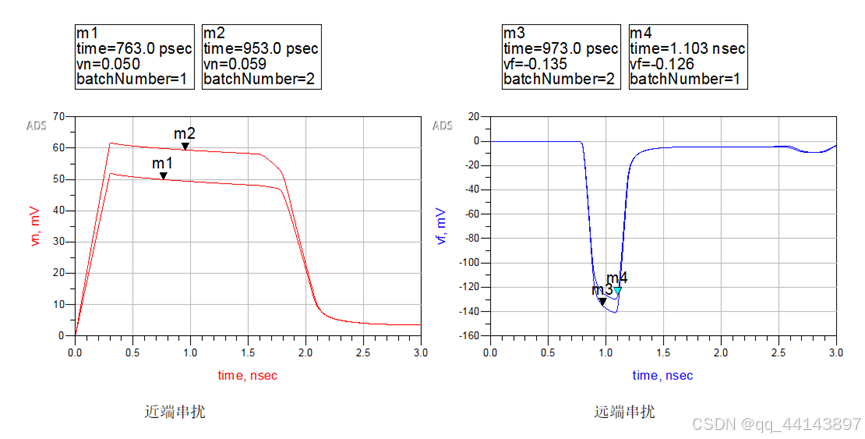

由上图可知,上升时间越大,近端串扰的波形边沿变化越缓慢,远端串扰也会越小。

**结论:**电路设计中,并不是上升时间越快越好,当信号完整性满足要求时,信号上升的时间尽量大一点,这样可以减少相邻信号的干扰,从其他方面来说,从电磁兼容的角度,也希望信号上升时间尽量慢一些。某些情况下,信号过快的上升和下降,也会导致温升偏高,影响系统的可靠性。

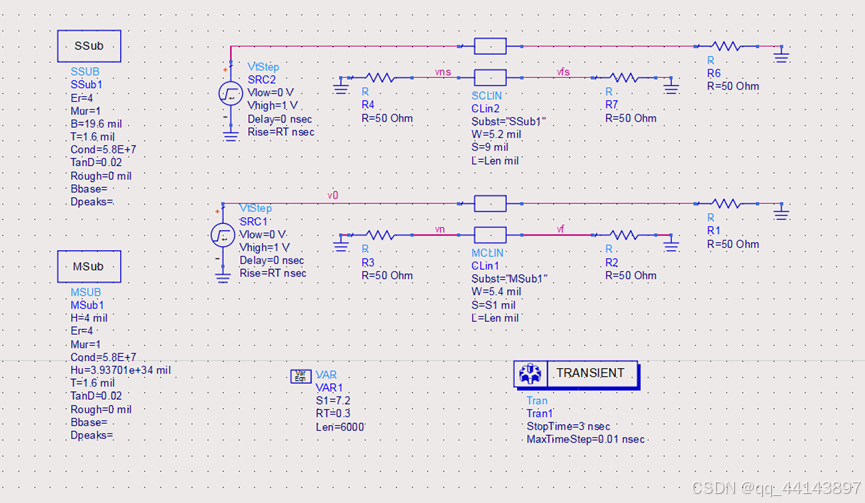

仿真三、串扰与带状线的关系

前面的仿真都是基于微带线进行的,(微带线:表层,带状线:内层),当走线为带状线即在内层走线时,微带线与带状线结果是否一致?

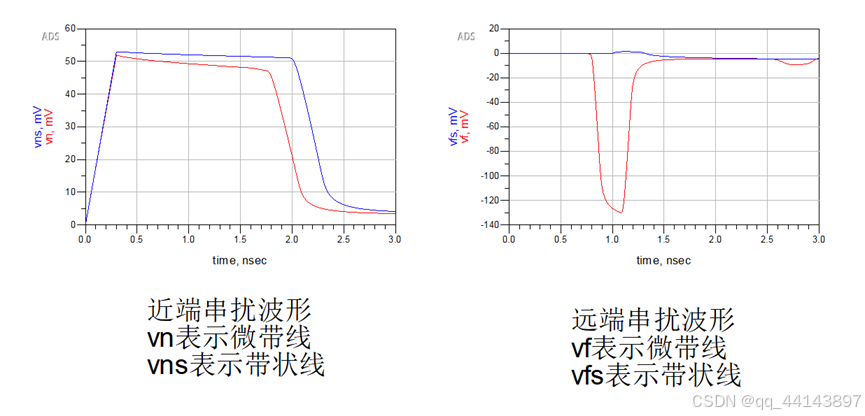

注:上图vns与vfs为带状线的测量参数,vn与vf为微带线的测量参数

如上图所示,由于层叠结构不同,所以线宽和线间距不相同,其他条件设置不一样。

由上面的仿真可知,带状线传输线远端串扰几乎为0,而近端串扰微带线和带状线相差不大。这对于长距离传输时,相当重要,可以大大减少串扰。

尽管如此,并不意味着内层走线没有间距要求。接着我做了如下仿真,查看微带线和带状线在不同间距下的串扰。

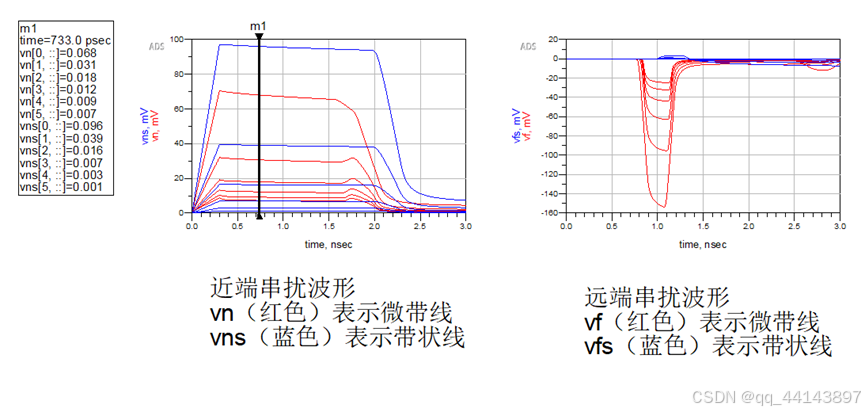

仿真四:微带线和带状线在不同间距下的要求

由上图可知,

在不同间距下,带状线的远端串扰几乎为0,近端串扰随两线距离增大而减小。相比之下,近端的串扰,却没有因为带状线而减小,反而略大于微带线,当然也随两线间距增大而减小。因此,从这个层面上来说,不管是带状线还是微带线,均有间距要求。

**产生上述现象的原因:**近端串扰主要由信号的上升沿引起的,因此无论是带状线还是微带线,均会产生。

远端串扰不一致的原因,带状线周围的材料是同质的,微带线由于处于表面,因此不满足要求。解决微带线远端串扰一个重要的方法是表面阻焊层,这个远端串扰的大小也与阻焊层的厚度为正相关。

不难得出下列结论:

如果所有导线周围的介质材料是同质,而且是均匀分布的,例如两条耦合的、完全嵌入式的微带线或两条耦合带状线,这种结构不会出现远端串扰(此为理想情况,实际上,即使是带状线也不可能完全同质,介电常数不可能完全一样)。

仿真三四结论: 内层外层均有间距要求;当传输线的距离较短时,建议走微带线,因为这样可以减少换层而增加过孔,增加过孔很容易造成阻抗不连续。(关于过孔的影响,后面会详细介绍)。

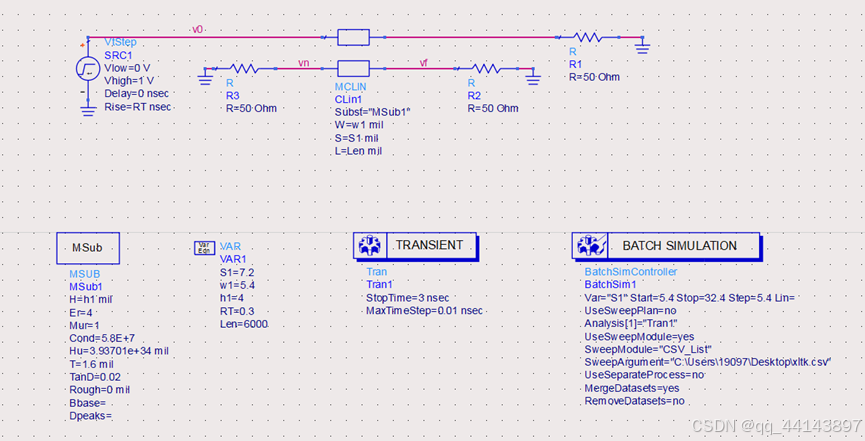

仿真五:传输线之间的耦合距离与串扰的关系

下图为仿真的原理图和仿真结果图,为了保持阻抗的一致性,当参考距离增大之后,也增大了该传输线的宽度(之前已经验证,阻抗不连续也会导致串扰增加)。如下图为参考距离为4mil和5mil时的串扰情况。

从仿真结果分析,当参考距离变大之后,串扰也会随之增大。

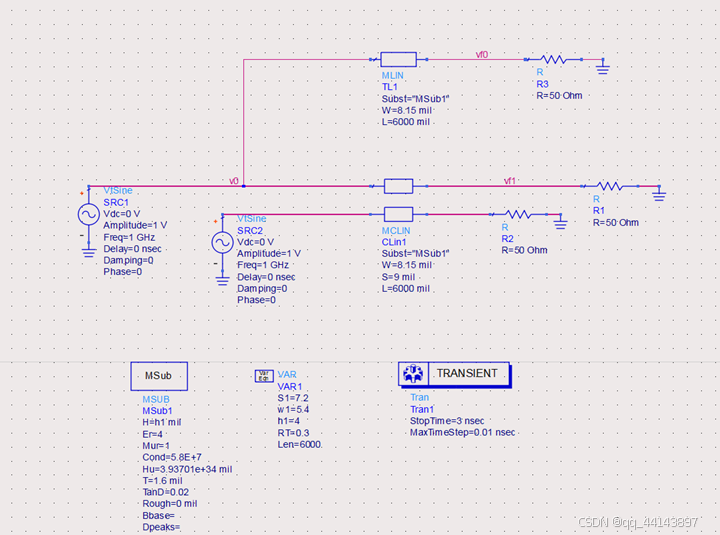

仿真六:串扰定量分析

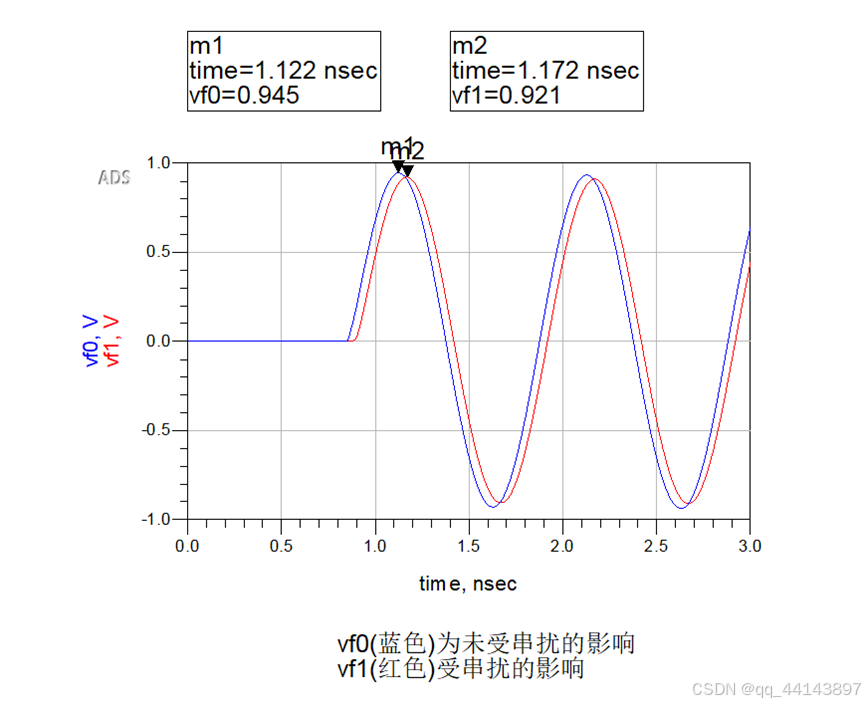

之前为了便于分析串扰因素的影响,通常都会假设另一条信号处于静态状态。对于实际来说,通常相邻的线可能会同时工作,为此,做了如下的对比图

由上图所示,串扰不仅影响了信号质量,带来噪声;还会使信号的时序受到影响!图中vf1比vf0快了50ps左右,这对于一些频率较高的信号,以及一些并行总线来说,也是一个不小的数值!

四、 如何减少PCB设计中的串扰

从之前的仿真我们可以看到,串扰不仅会引入噪声,还会影响到信号的时序。因此,串扰带来的影响不可忽视。

结合我查阅的资料,以及仿真情况来看,可以从以下方面减少串扰:

1、 尽量减少传输线之间的耦合长度,尽量保证在耦合饱和长度以内。

2、 尽量增加传输线之间的耦合距离,能保证3倍线宽更好。

3、 在满足信号完整性的前提下,尽量减缓信号上升的时间。

4、 对于耦合长度较长的高速传输线,尽量走内层,可以大大减少远端串扰,如果要在表层布线,则尽量在表面增加阻焊层的厚度,减少远端串扰。耦合距离较短时,可以在表面布线,这样可以减少过孔带来的影响。

5、 信号布线尽量靠近参考层布线

6、 当相邻层都是信号层时,布线尽量避免相邻信号层平行布线。最好垂直布线。

7、 尽量维持阻抗的连续性,减少阻抗不匹配带来的影响。

8、 空间足够大的时候,可以给高速信号线加屏蔽地,并加上合适的过孔。

9、 高速信号线尽量不要布到PCB板框边缘,最好保证到达信号到参考层的距离的20倍。

5452

5452

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?