我是 雪天鱼,一名FPGA爱好者,研究方向是FPGA架构探索。

关注公众号【集成电路设计教程】,获取更多学习资料,并拉你进“IC设计交流群”。

QQIC设计交流群 群号:866169462。

通过 FABulous 所提供的唯一一个 demo 来学习下 eFPGA Fabric 的建模方法。

目前在研究eFPGA,学术界目前最新发表了用于RTL TO GDSII Flow 的开源框架 OpenLane

后续我的研究会使用到该框架,故先进行开发环境搭建,过程记录如下。

| Version | Date |

|---|---|

| V1.0 | 2022.1.30 |

一、代码下载编译

系统:ubuntu20.04

1.1 依赖

- Docker 19.03.12+

- GNU Make

- Python 3.6+ with PIP

- Click, Pyyaml:

(1)Docker的安装可参考我之前博客OpenFPGA系列(一)开发环境搭建 2.1节

(2)GNU Make的安装教程很多,自行搜索

(3)Python建议下载Anaconda,方便后续建立虚拟环境来进行管理,可参考我之前的博客PyTorch深度学习入门笔记(一)PyTorch环境配置及安装 1.1节

(4)在(3)步完成后,打开终端,输入下述命令:

conda create -n openlane python=3.7

source activate openlane

pip install pyyaml

pip install click

即创建一个 名为openlane python版本为 3.7 的虚拟环境,并激活环境安装python包。(由于我已经创建过了一个名为 FABulous 的虚拟环境,所以接下来我都是在此虚拟环境下进行操作的)

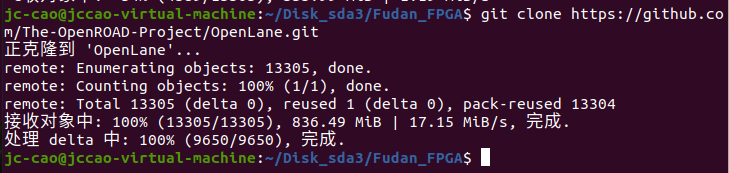

1.2 代码下载

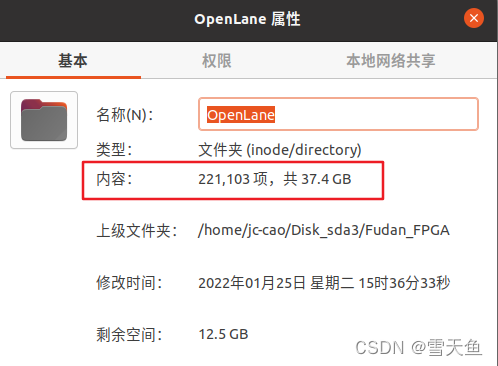

注:完整编译后,所需空间是37.4GB,提前检查存储空间是否足够。

在存放目录下,打开终端,输入:

git clone https://github.com/The-OpenROAD-Project/OpenLane.git

下载完成后输入:

cd OpenLane

make pull-openlane

如果报下述错误:

docker: Error response from daemon: Get https://registry-1.docker.io/v2/: net/http: request canceled while waiting for connection (Client.Timeout exceeded while awaiting headers).

就修改docker镜像源,docker默认的源为国外官方源,下载速度较慢,可改为国内,进行加速。更换Docker镜像源参考博客

FULL_PDK=1 make pdk

获取SkyWater130nm 开源PDK,这里我选择下载完整的PDK,默认保存到 OpenLane/pdks/skywater-pdk 路径下

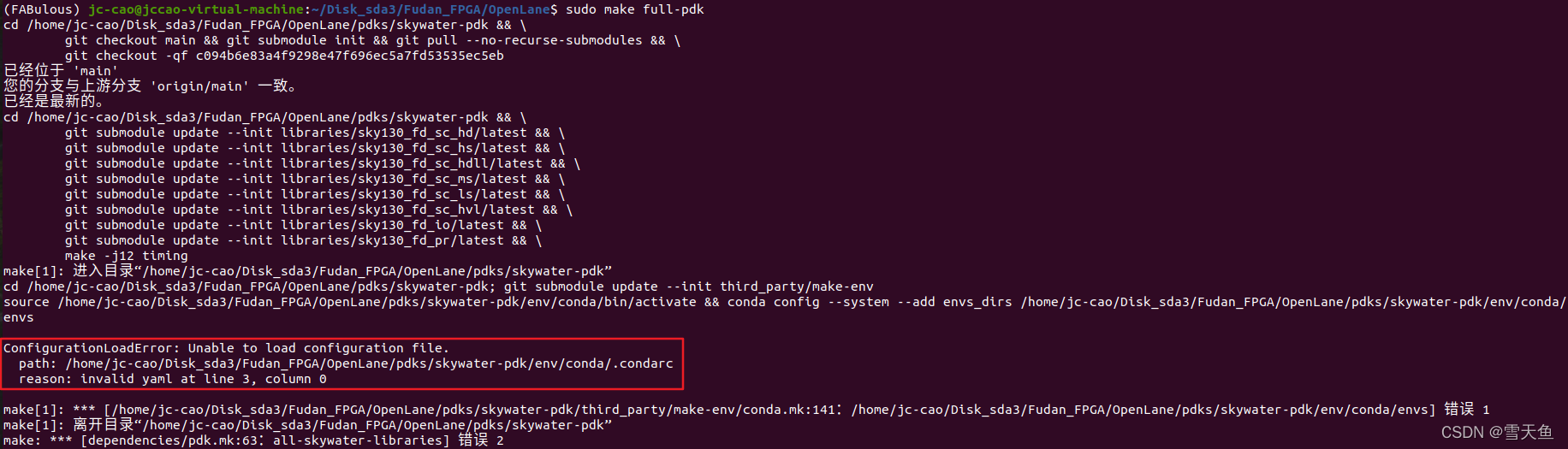

这个过程中所遇到的问题:

ConfigurationLoadError: Unable to load configuration file.

path: /home/jc-cao/Disk_sda3/Fudan_FPGA/OpenLane/pdks/skywater-pdk/env/conda/.condarc

reason: invalid yaml at line 3, column 0

错误原因:由于当前所在虚拟环境是FABulous,有其自己的配置文件,所以无法将OpenLane/pdks/skywater-pdk/env/conda/.condarc作为配置文件加载。

解决方法:删除OpenLane/pdks/skywater-pdk/env/conda/.condarc,重新输入命令make pdk

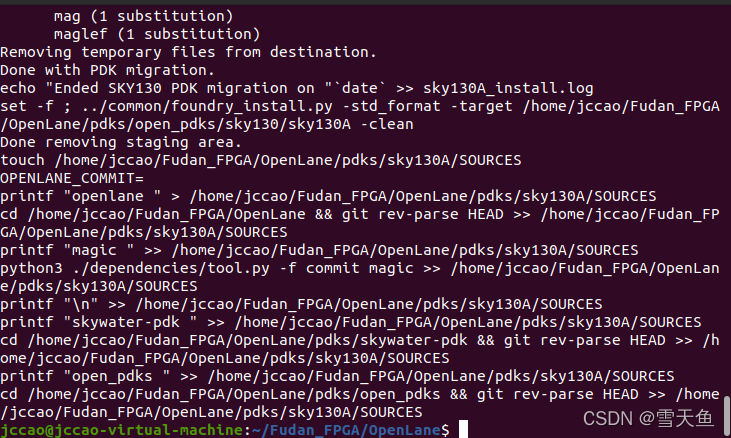

到这里OpenLane的开发环境便编译搭建好了。

*注:

(1)执行 make pdk过程中遇到的其他问题,可以查看第二节 make pdk 解析进行解决,在此不再赘述。

(2)我的虚拟机总是下载包时卡住,以为是梯子的问题,后来检查了发现不是,而是因为有线连接导致的,换成了WIFI后就可以了。

*

1.3 测试

然后在 openlane 的根目录,先激活虚拟环境,我的命名为了 FABulous,即source activate FABulous,再输入 make test 开始测试:

可以看到测试通过了,说明编译没有问题!

后续将使用此框架进行一些 RTL to GDS Flow的测试

二、make full-pdk 解析

2.1 pdk.mk解析

注;2022年1月29号OpenLane进行了一次更新,目前pdk环境搭建指令是

make pdk,通过变量 FULL_PDK

来设置是否获取完整的 PDK。下述的错误记录及解决方法适用于之前版本,现在仅供参考。

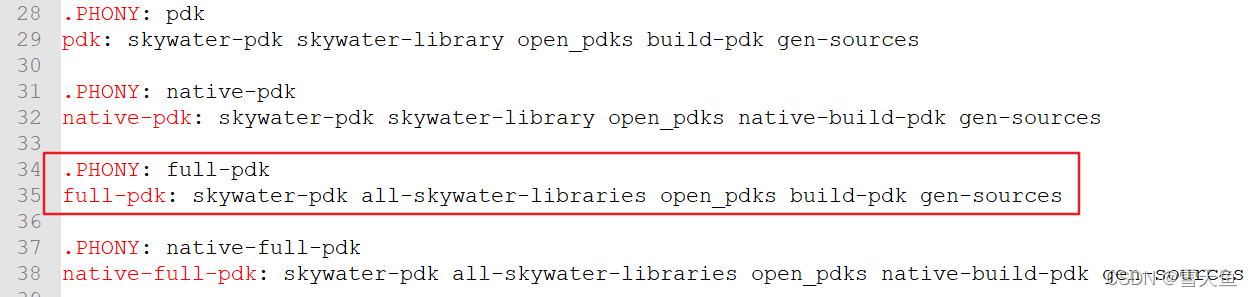

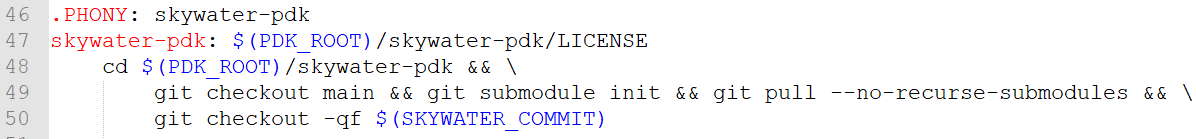

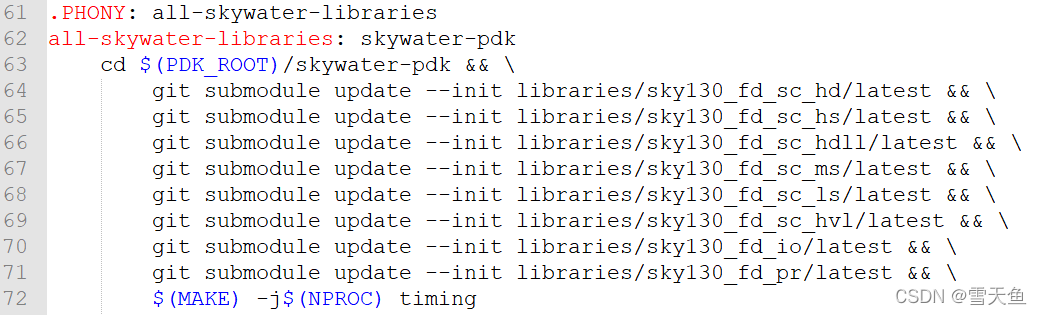

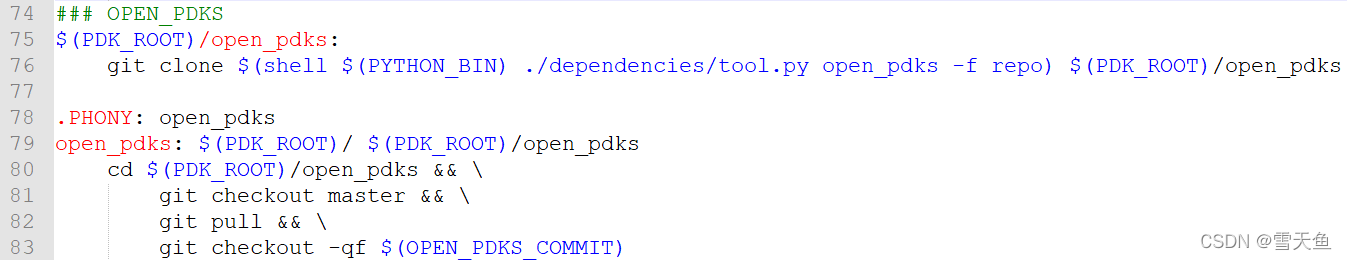

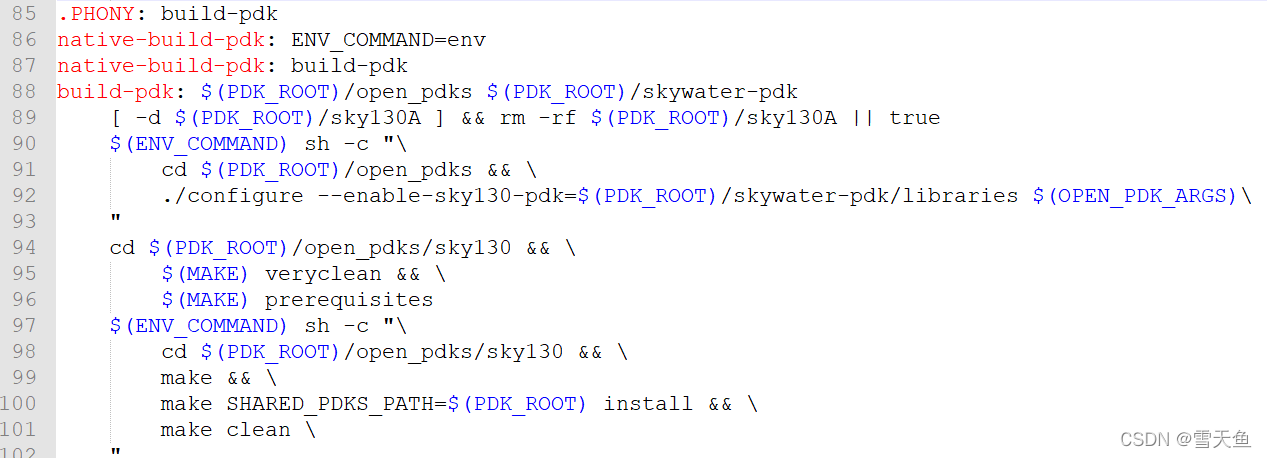

full-pdk是个伪目标,在 OpenLane/dependencies/pdk.mk 中定义:

包括五个子伪目标,一个个来进行查看分析:

- skywater-pdk

- all-skywater-libraries

- open_pdks

- build-pdk

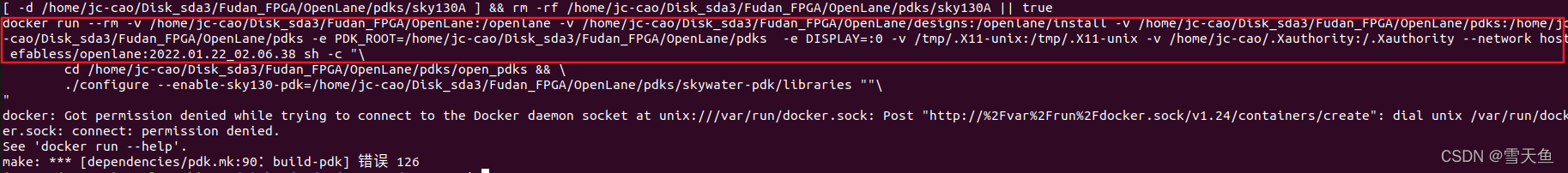

我在编译是,卡在了第90行:

这是因为我的 docker 需要 root权限才能运行,那么让其运行时加个sudo就可以解决问题 ,

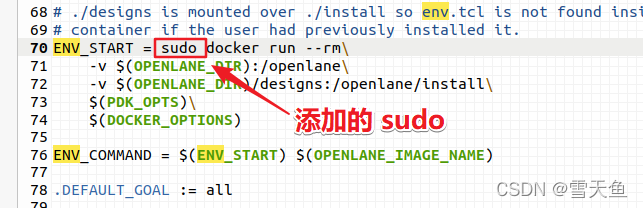

ENV_COMMAND变量在OpenLane/Makefile第76行定义:

那么加个sudo就行:

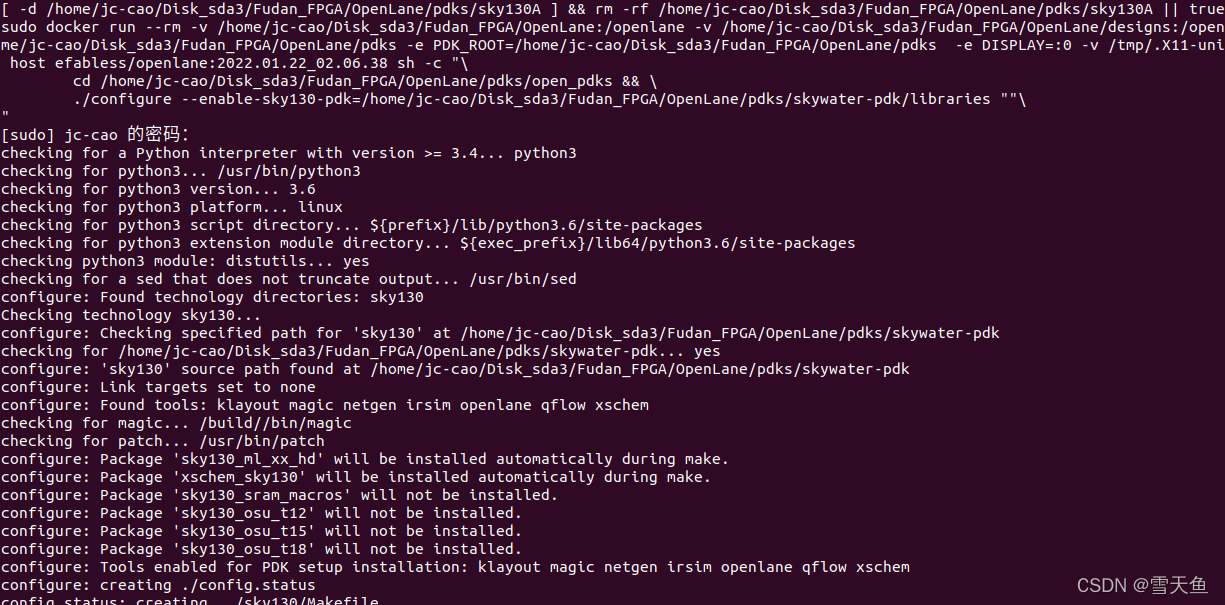

重新输入make full-pdk测试,可以看到sudo后就可以正常继续编译了

2.2 卡住了怎么办?

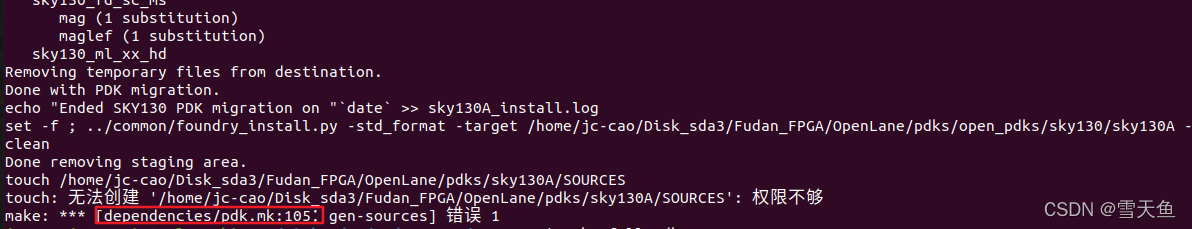

我pdk.mk的105行,编译目标 gen-sources卡住了

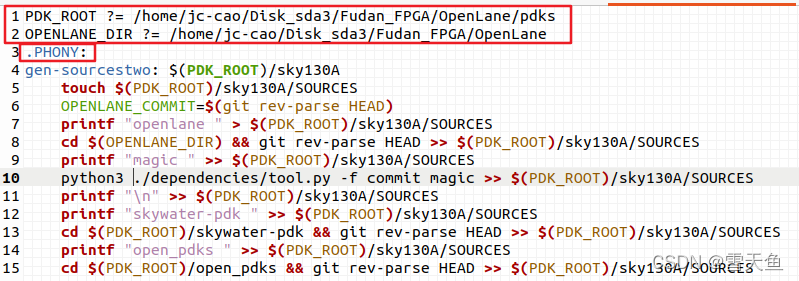

那么此时为了避免重复编译之前编译过的目标,则直接将 gen-sources 目标对应的命令给复制到单独的一个文件中,并将 gen-sources 改名为 gen-sourcestwo:

(1)给变量进行赋值

(2)将 gen-sourcestwo 设置为伪目标

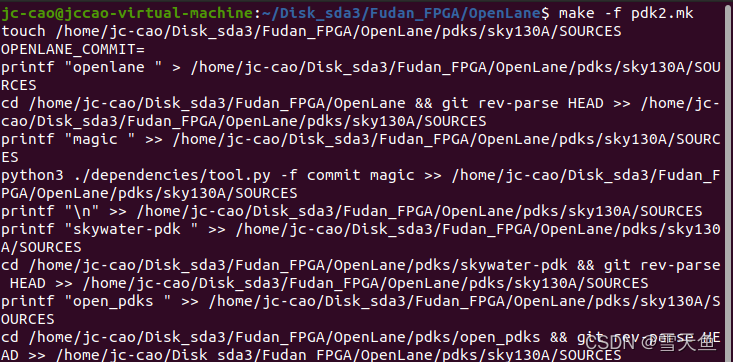

将此文件命名为 pdk2.mk,放在openlane的根目录下,然后输入

make -f pkd2.mk

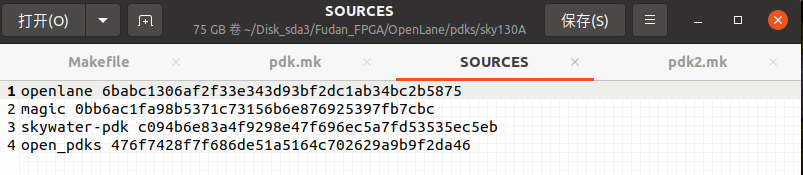

source文件:

308

308

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?