我是雪天鱼,一名FPGA爱好者,研究方向是FPGA架构探索。

笔记同步在我的个人网站进行更新,欢迎来访查看。

IC/FPGA 设计学习交流群号: 866169462

实验手册和数据来自 Innovus Lab和Lab Guide下载地址

实验所需

- 可以使用 Cadence Innovus 软件

- 已经下载上述链接中的实验数据

一、导入设计

目标: 打开 Innovus GUI 界面并导入设计

在这个实验中,将学习

(1)如何导入门级网表和库到 Innovus 中,并创建 floorplan;

(2)可以熟悉 floorplanning 流程和 power planning 流程;

(3)将学会如何用盲键去检查库,设计。

- 在

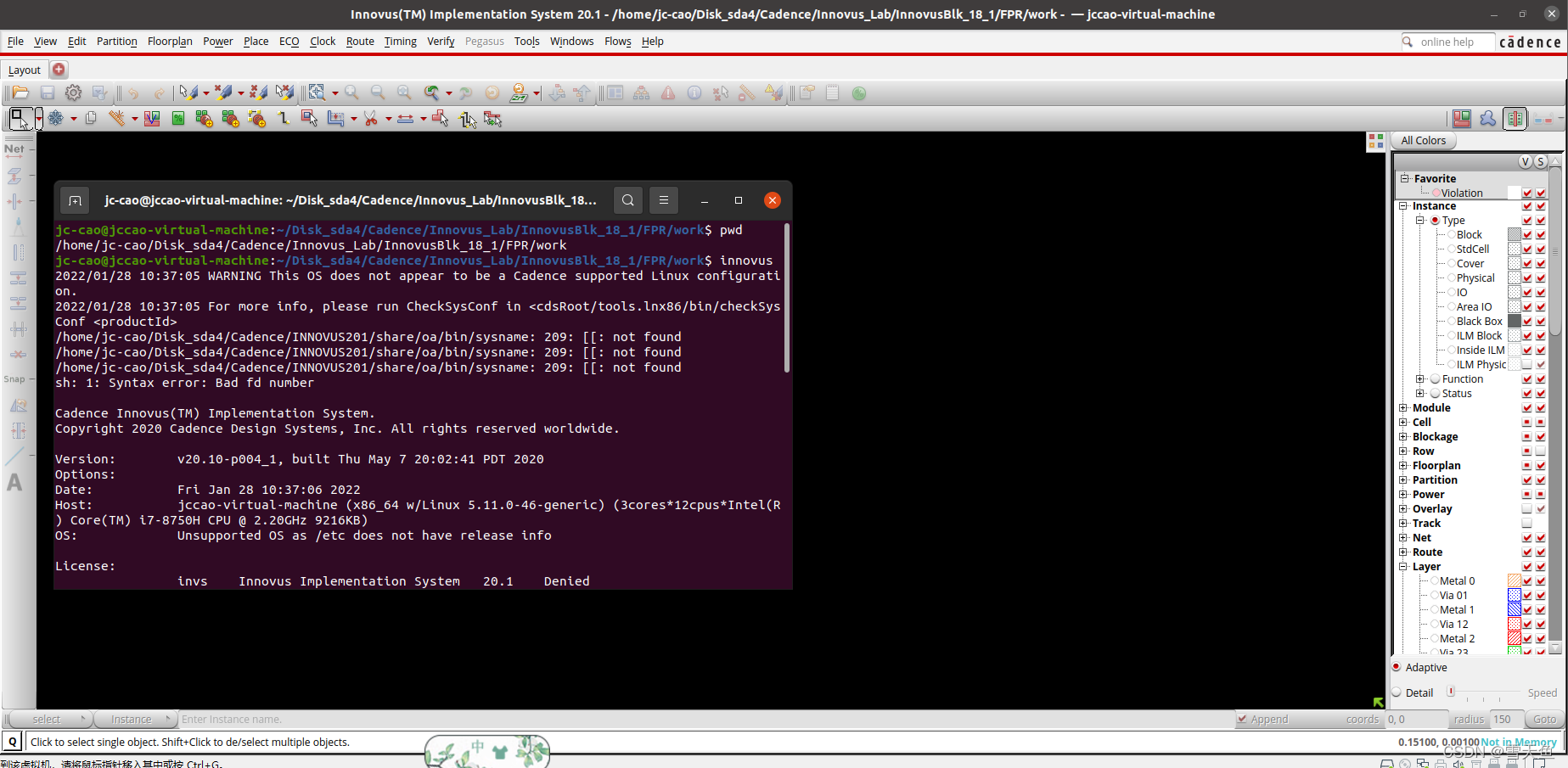

InnovusBlk_18_1/FPR/work目录下打开终端,输入innovus打开软件:

- 点击 菜单栏中的

File -> Import Design

自动弹出导入设计的窗口:

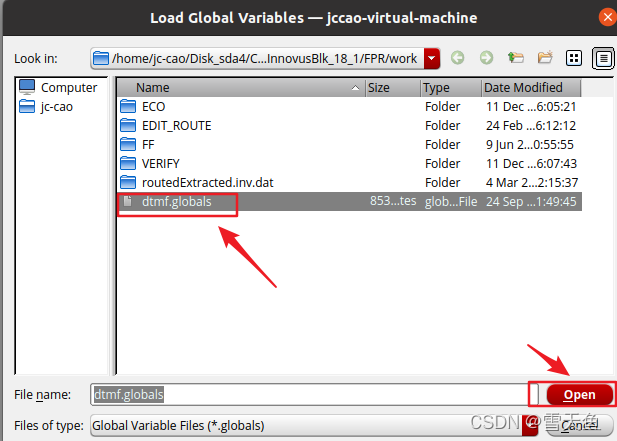

直接点击窗口最下方的五个按钮中的 Load...:

选中 dtmf.globals 文件,点击 open:

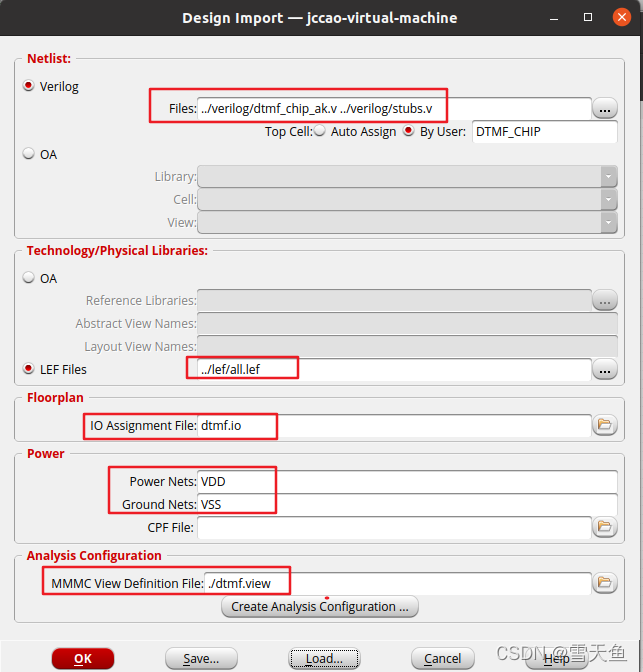

可以看到设计导入的窗口各栏都已经配置好了。

dtmf.view文件包含指向时序库和约束文件的指针。dtmf.io文件是 I/O 分配文件,包含有关在 core 区域外围放置 I/O 焊盘的指令。

窗口各个部分的介绍如下:

| 名称 | 作用 |

|---|---|

| Netlist-Verilog | 添加综合好后的门级Verilog网表,即.v文件 |

| LEF Files | 包含元件库和元件的物理信息,也包含布线层和DRC规则 |

| IO Assignment File | 包含了用于放置 IO Pad 到core外围的指令,如果没添加此文件,则软件会随机放置IO pad |

| MMMC View Definition File | 包含了指向时序库和SDC约束文件的指针 |

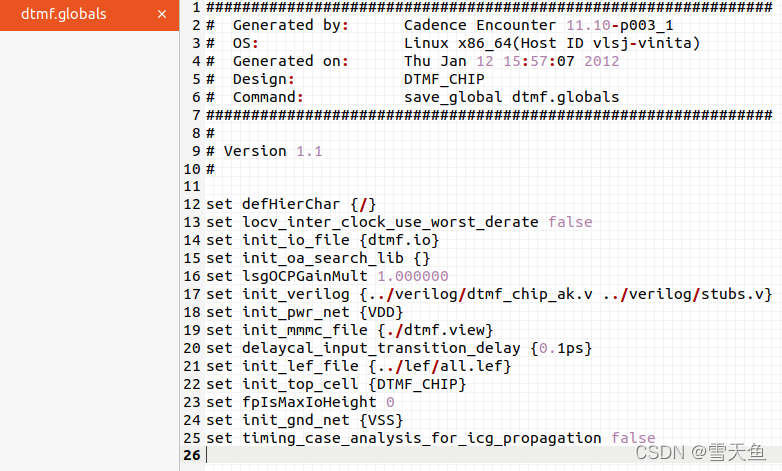

这里查看了下 dtmf.globals 文件:

可以看到在这个文件中,通过很多命令去定义了设计的一些配置,比如gnd/Power 信号,要导入的门级网表,顶层单元名,工艺库文件lef 等信息。在导入设计时只需要 Load 一下这个配置文件,就可以很方便的导入自己的设计,所以以后可以仿照着此文件写自己设计的配置文件。

- Load 好了这个配置文件后,就点击 OK:

二、查看设计

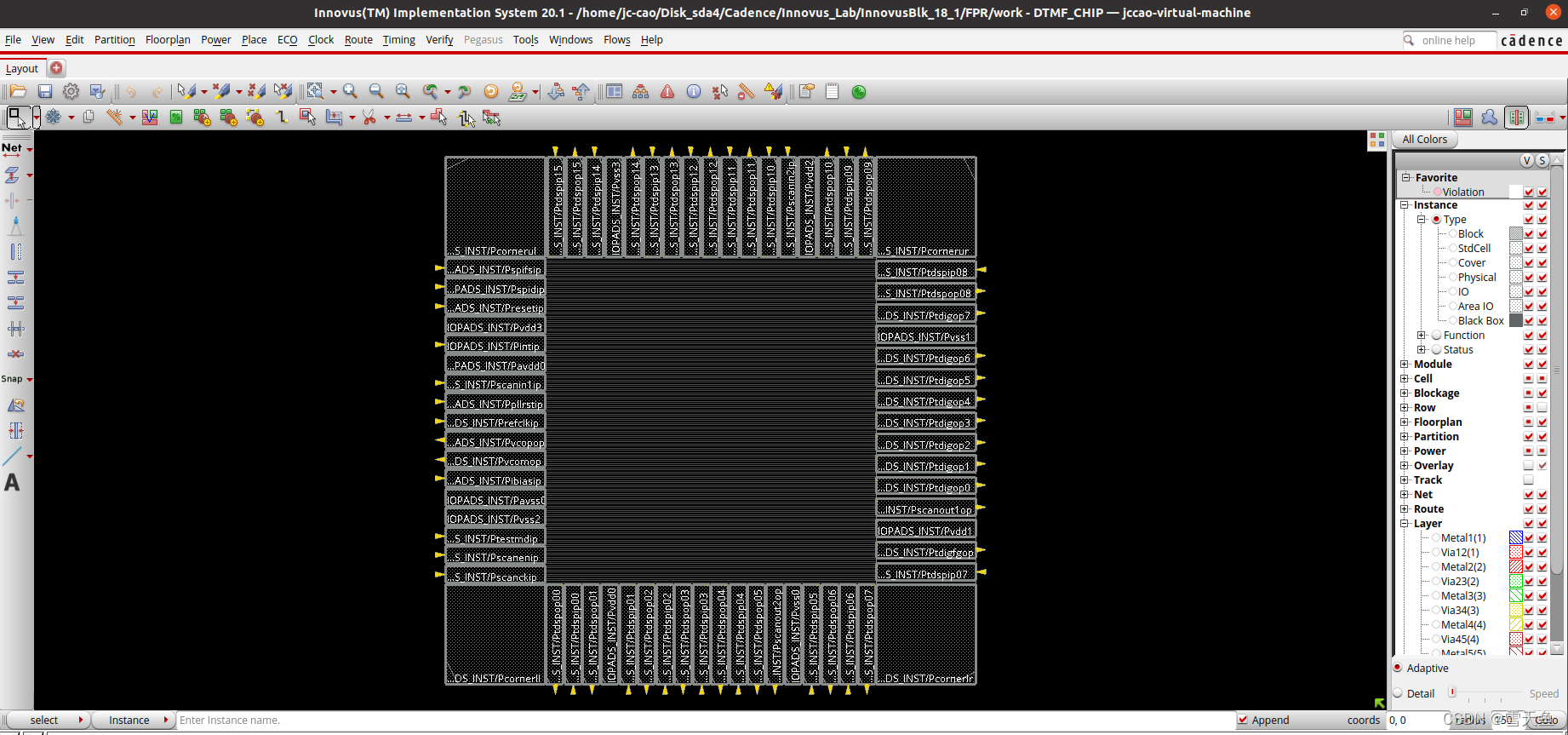

1.点击 Innovus 右侧 Floorplan view 图标:

再按 F ,将设计置于窗口中间

2. 在右侧的 All Colors 面板上,选中 Cell ,将 Pin Shapes 勾选上,使其可见。

3. 可通过菜单栏 Tools -> Log Viewer 查看log

可以看到,log中包含 Innovus 每一步操作的信息。

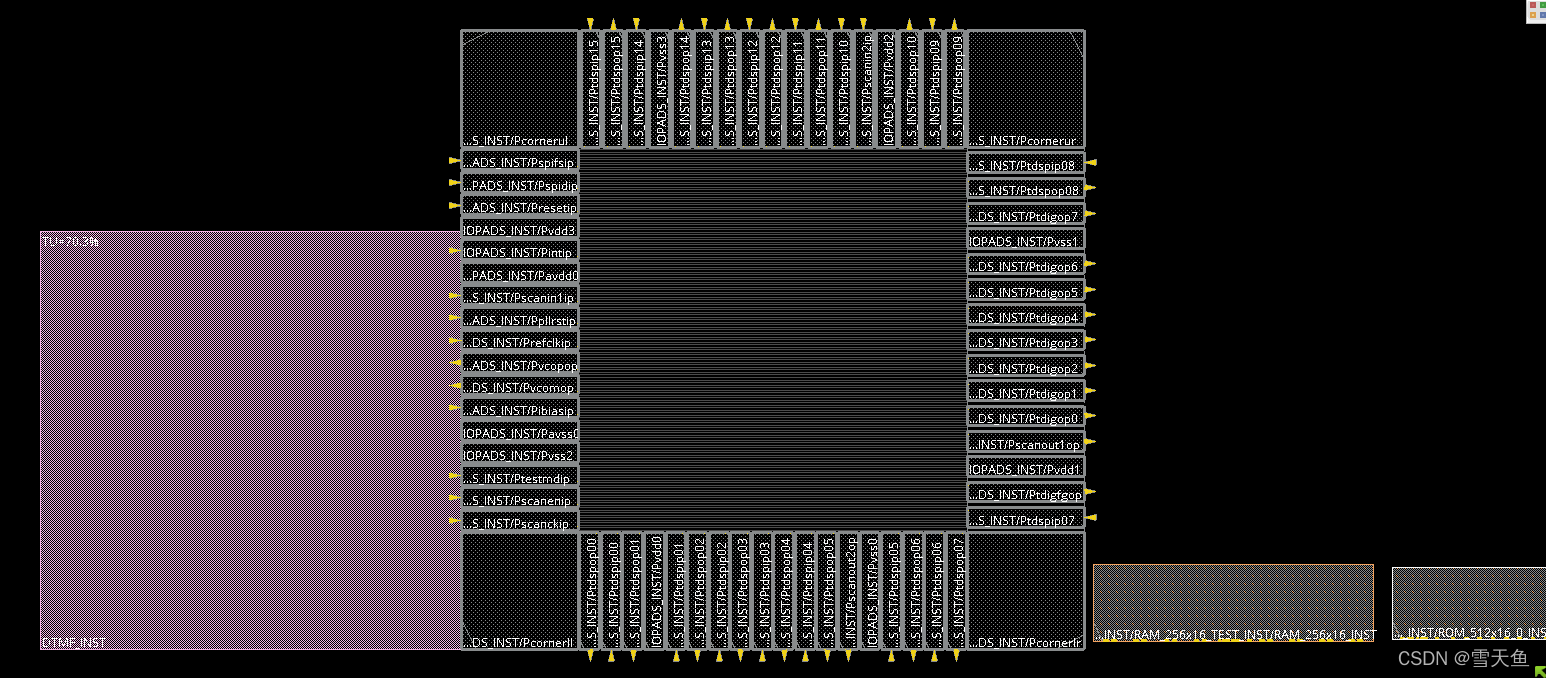

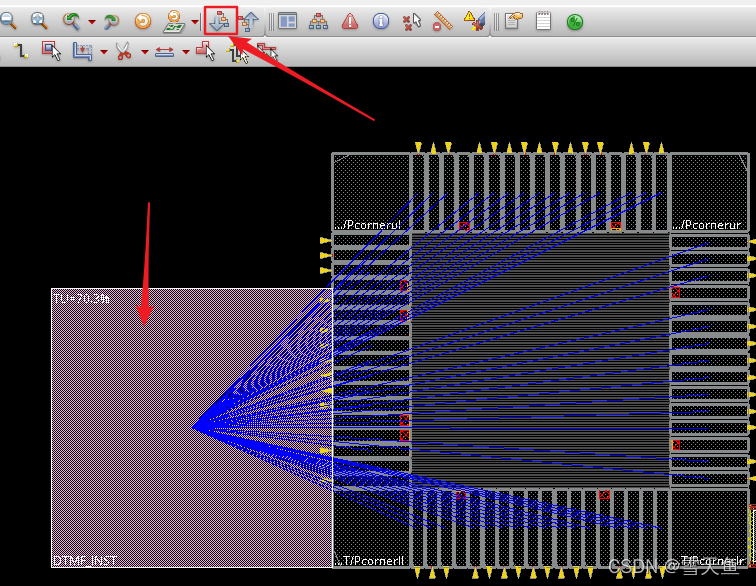

4. 选中设计左侧的模块 DTMF_INST,点击 Ungroup 图标一次,取消组合:

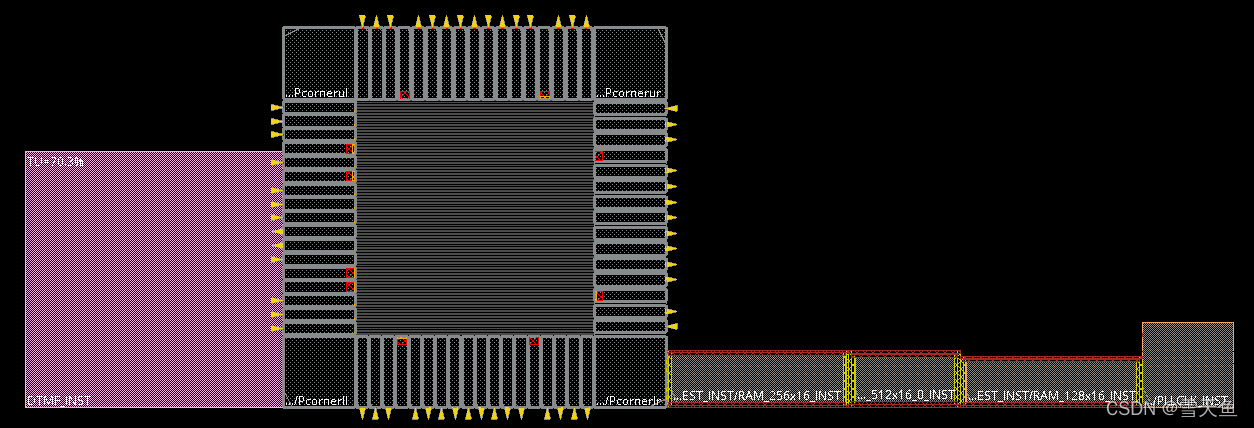

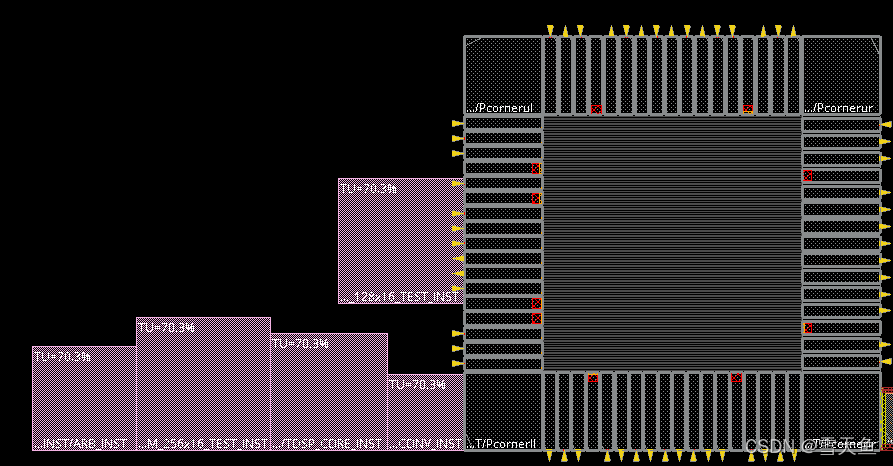

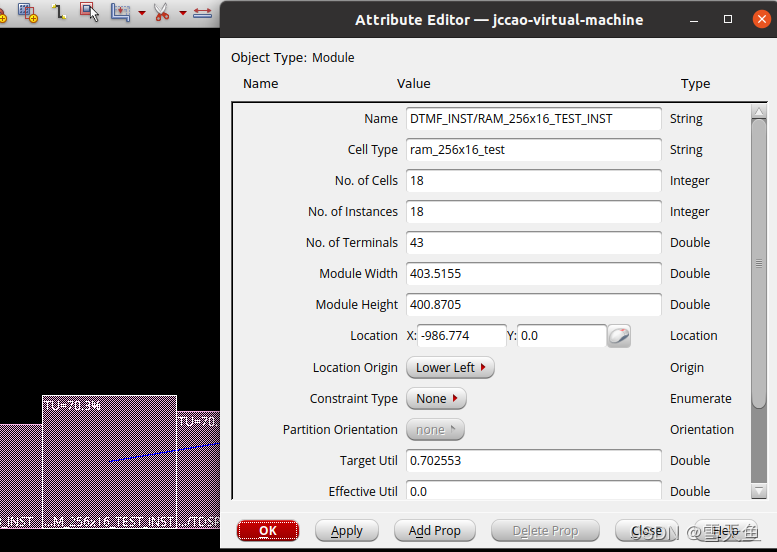

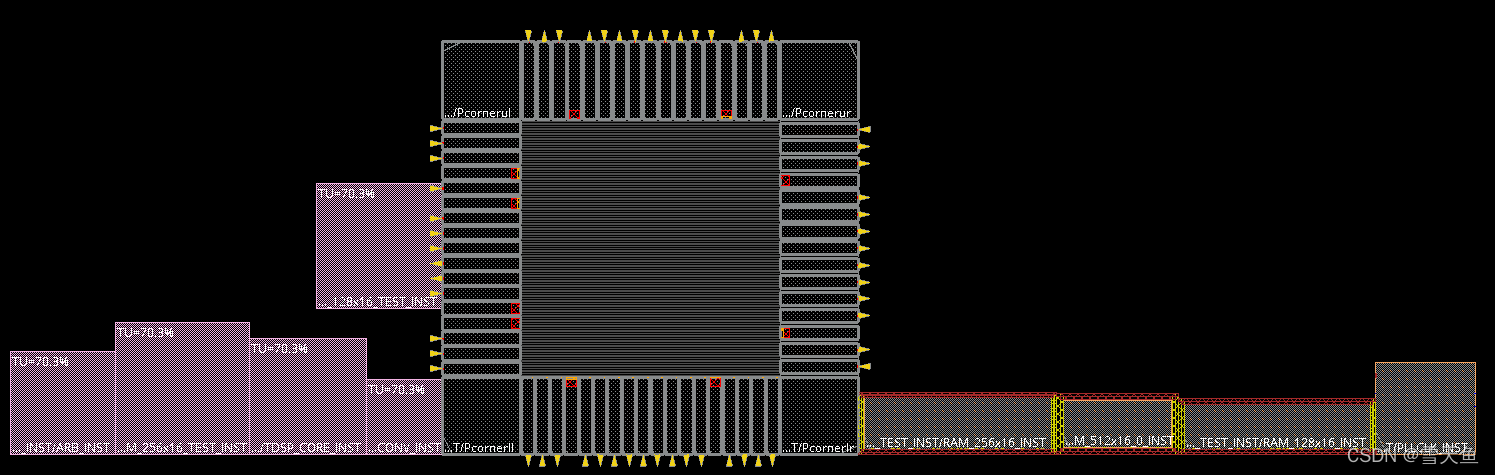

将该模块拆分为了多个模块。双击这些子模块可以看到其名称和属性:

在上图中,左侧粉色模块是在导入的网表文件中所定义的模块,右侧的是硬宏或者IP。

5. 选中一个粉色模块,点击组合,进行重组。

三、查看设计层次

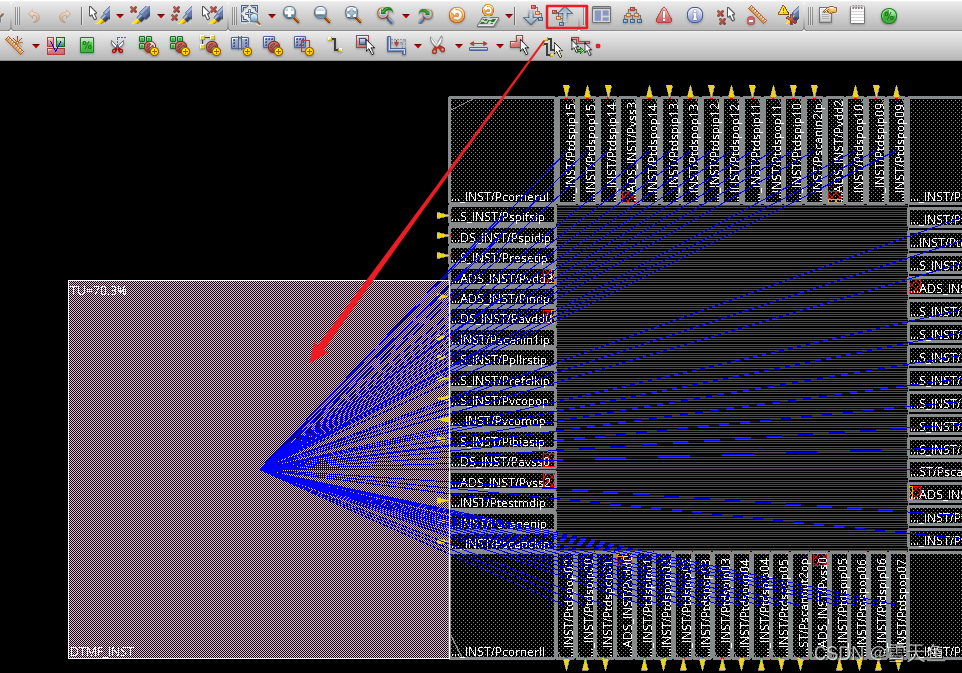

- 在所有objects 都没被选中的情况下,点击菜单栏中的

Tools->Design Browser:

可查看 DTMF_CHIP 的设计层次。

这次Lab到此结束!主要学习了如何导入设计,然后对Innovus的一些基本操作进行了讲解。

812

812

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?