学习笔记同步发布在我的个人网站上,欢迎来访查看。

个人学识有限,理解可能有误,仅供参考。

先贴图,后续学习了,慢慢添加个人理解。

文章目录

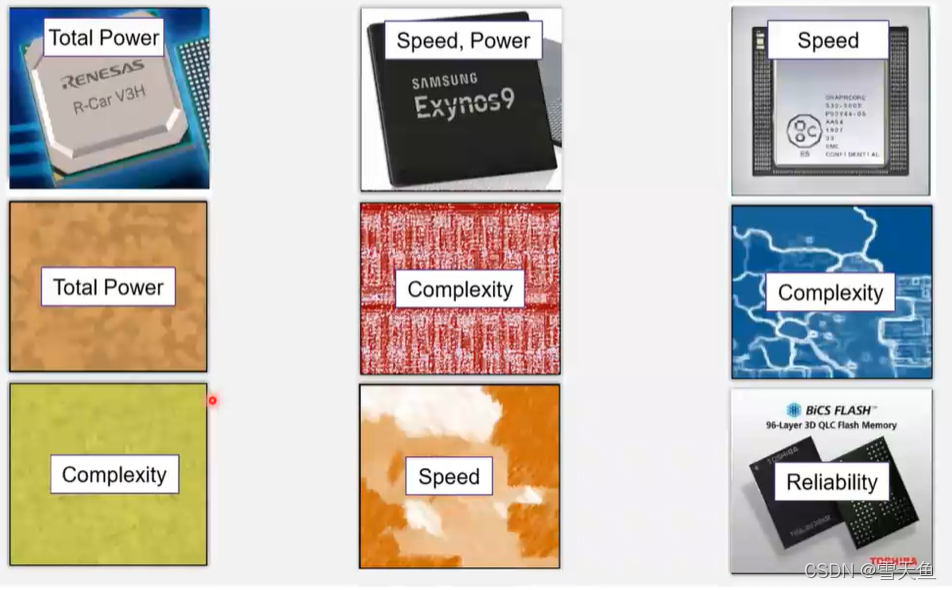

课程主题:如何用 ICC II来实现最好的PPA

一、前言

现在的芯片都在追求一个极致的PPA

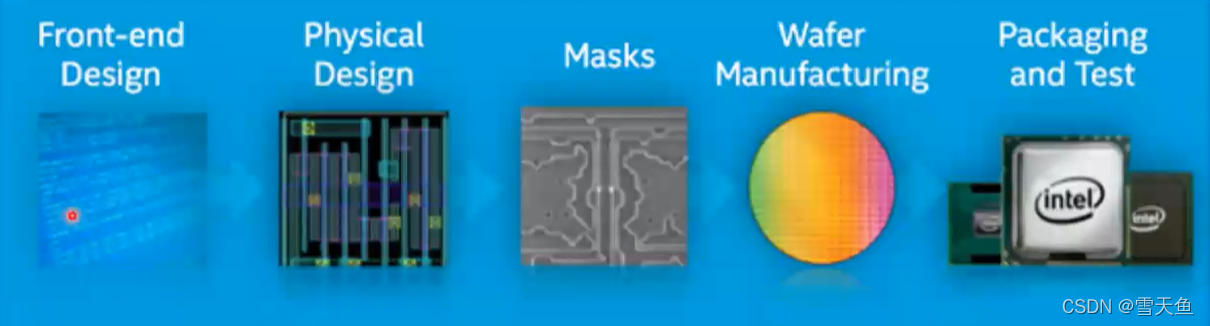

芯片的生成可以分为以下 5大步骤:

- Front-end Design:前端设计,最终产生门级网表,提供给后端工具。

- Physical Design :后端物理实现,最终产生 sign off 的GDSII文件,交付给晶圆加工厂

- Masks: Foundry 生产对应的掩膜版

- Wafer Manufacturing:通过掩膜版生产芯片,又称为 tape out

- Packaging and Test:对上一步生产好的芯片进行封装测试

而ICC II就是用于 Physical Design这一步的 IC 工具

ICC II 引入了 Fusion的概念,将整个后端的一些工具都集成在一起,所以可以进行综合考虑,达到更好的PPA,同时也减少 runtime。

二、 ICC II 简介和 GUI

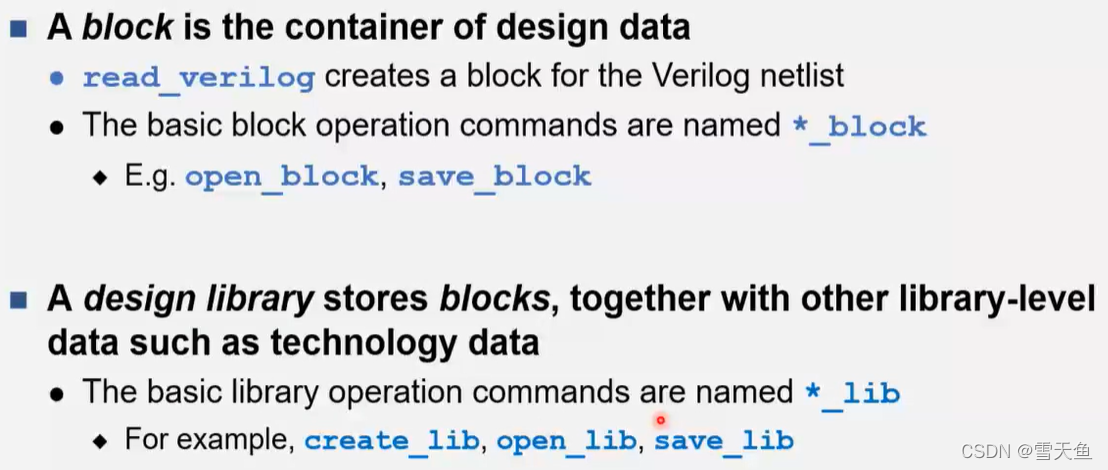

2.1 Blocks 和 Design Libraries

在ICC II中有两个很重要的概念,即 Blocks 和 Design Libraries

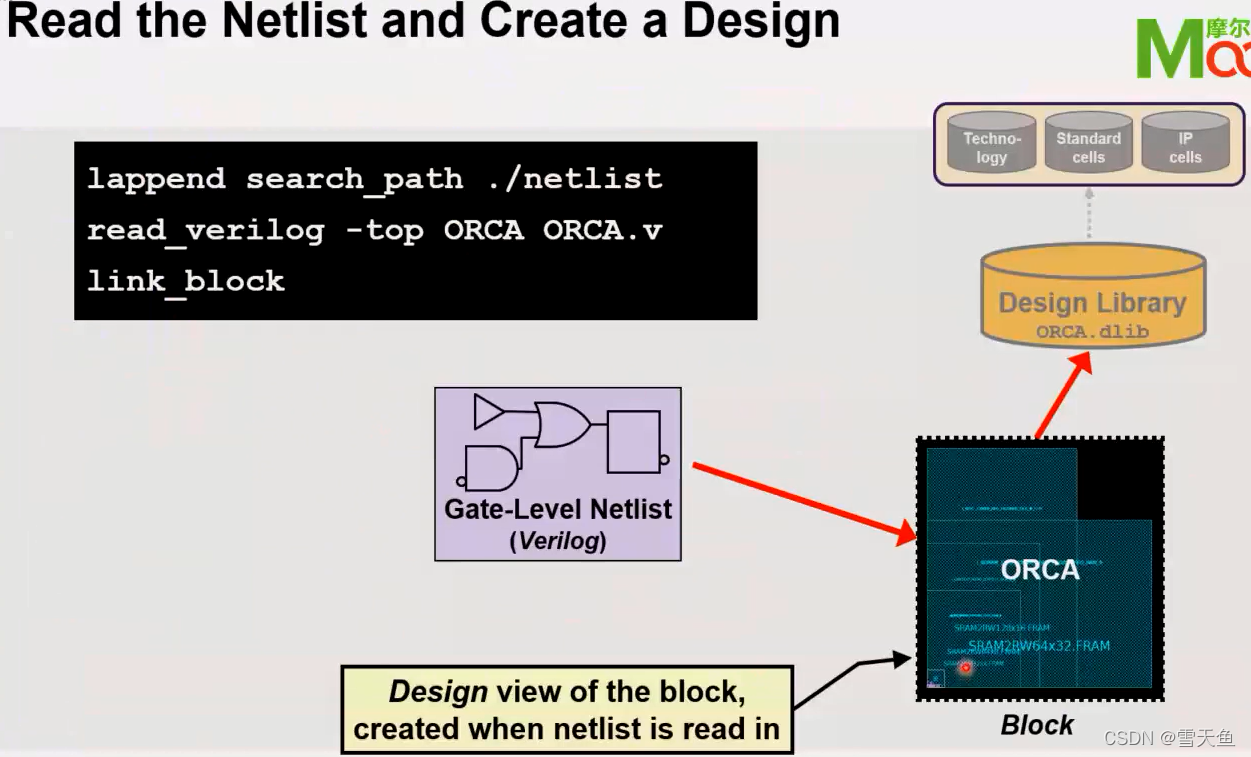

即 Blocks是 Verilog 网表的容器,而 design library 是 blocks和其他一些库级数据的容器。

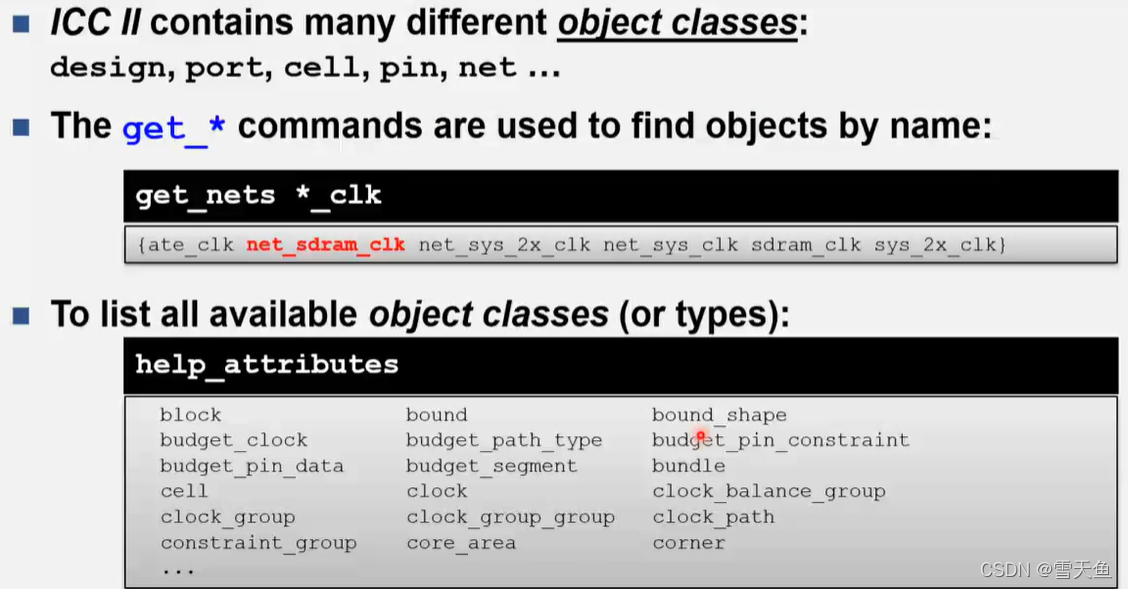

2.2 Objects

即ICC II由很多对象种类组成,有 design/port/cell/pin/net…

可以通过命令

get_<object class> <object name>搜索设计中所用到的对象。

例 找 net 种类对象中命名带后缀 _clk 的对象,对应指令为: get_nets *_clk

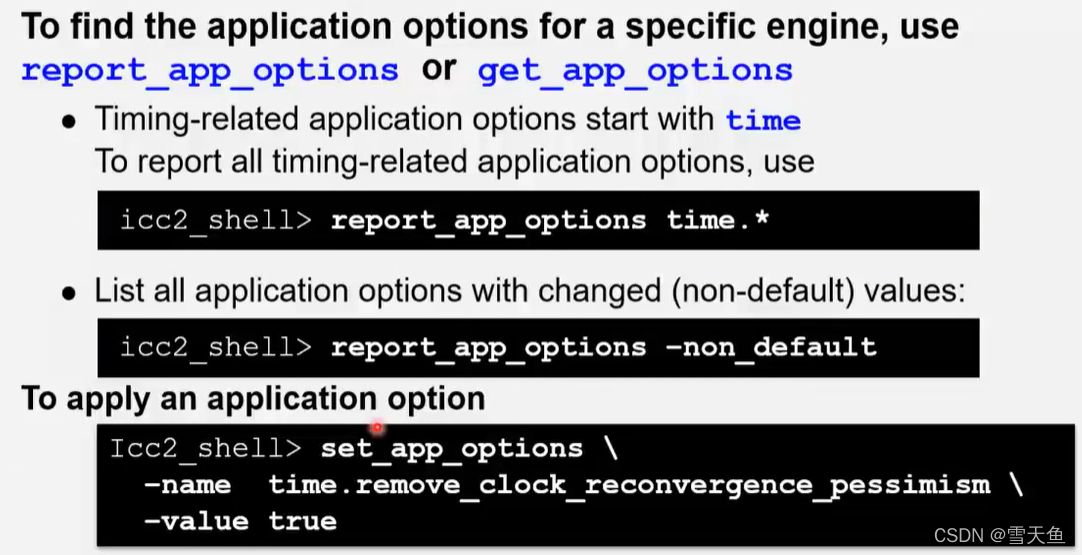

2.3 Application Options

SPG: Synopsys Physical Guidence,在综合的时候采用后端物理 floor plan的信息去综合,突出一些问题信息,用来给后端流程使用

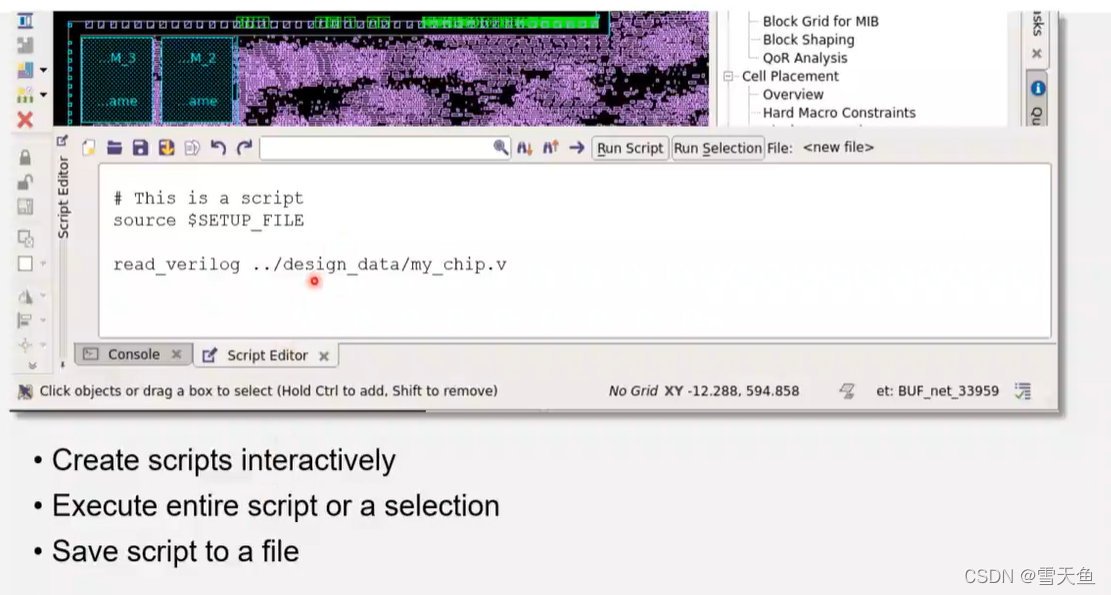

2.4 ICC II图形化界面

三、Design Setup

接下来介绍如何用 ICC II进行一个Design flow

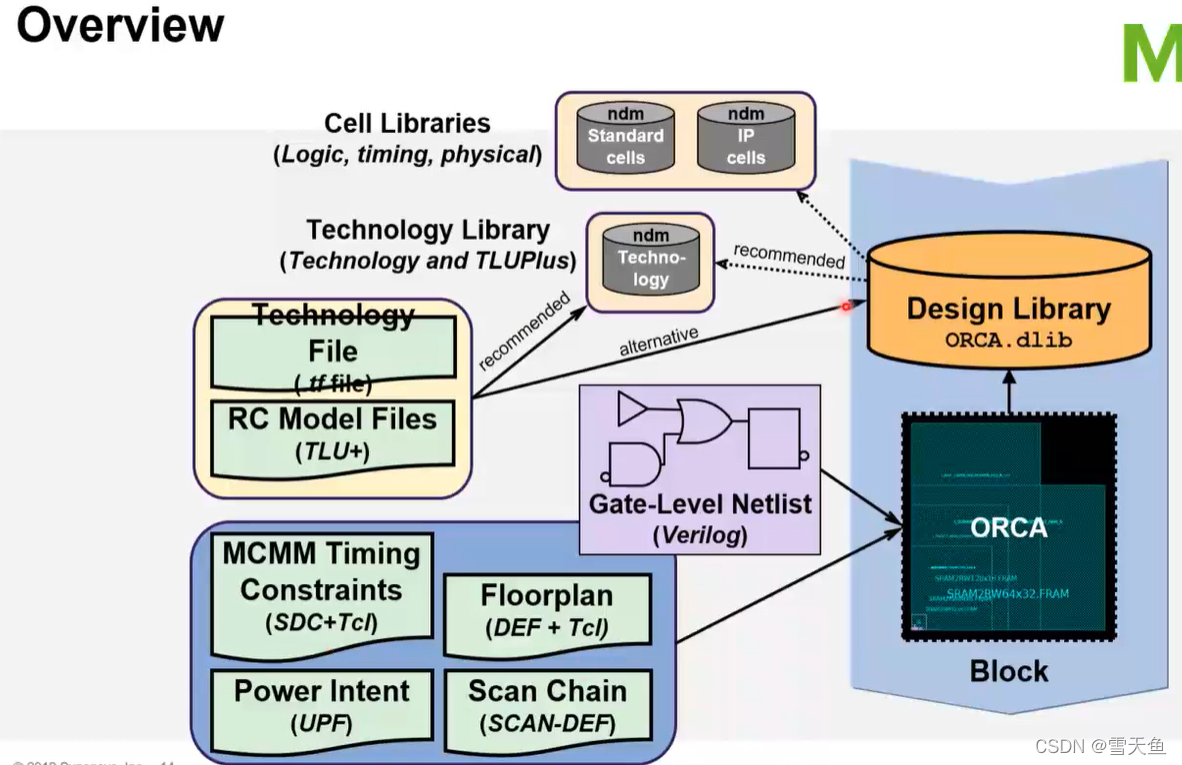

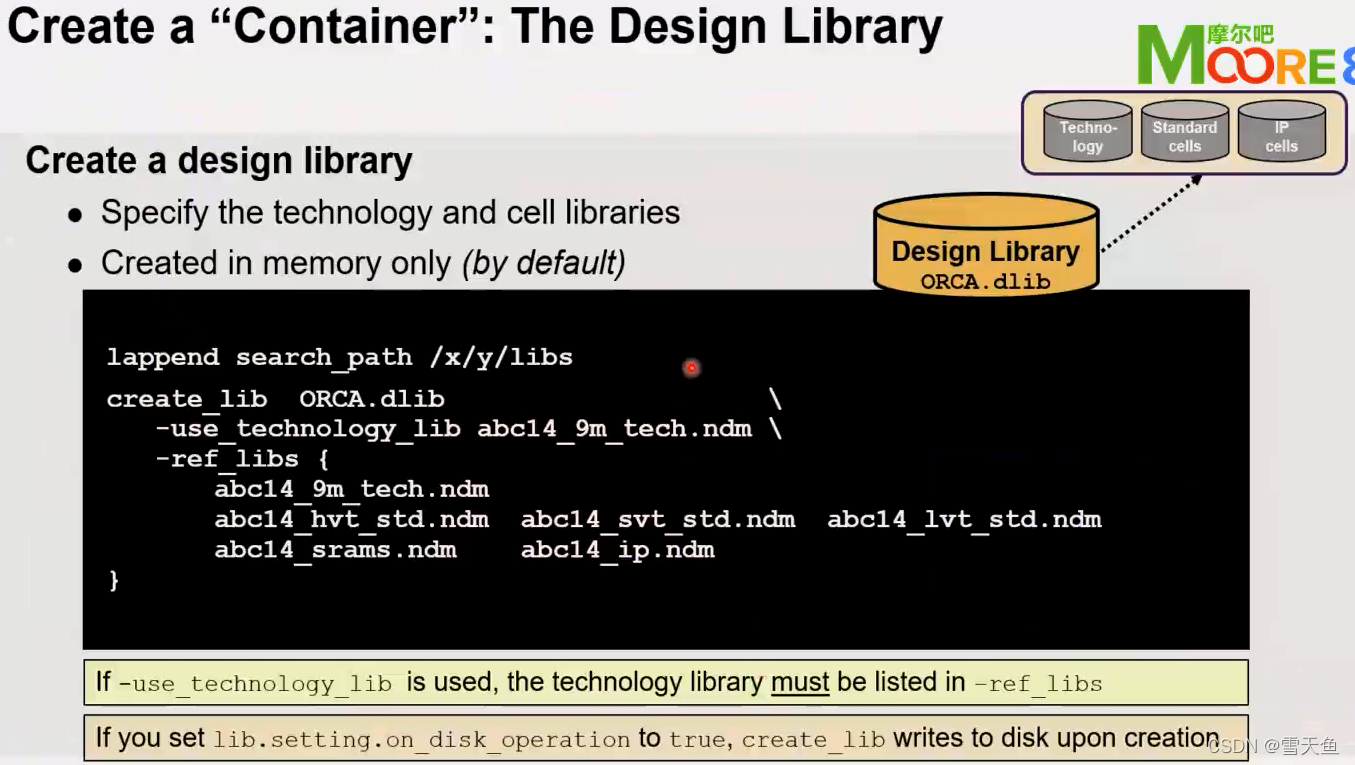

Design Library是一个大的容器,包括了Block(Block里则包含了门级网表,设计约束文件)、Cell Libraries(标准单元库和IP单元库)、Technology Library。后两者都是采用 NDM 形式,等下将介绍怎么产生对应的 NDM。

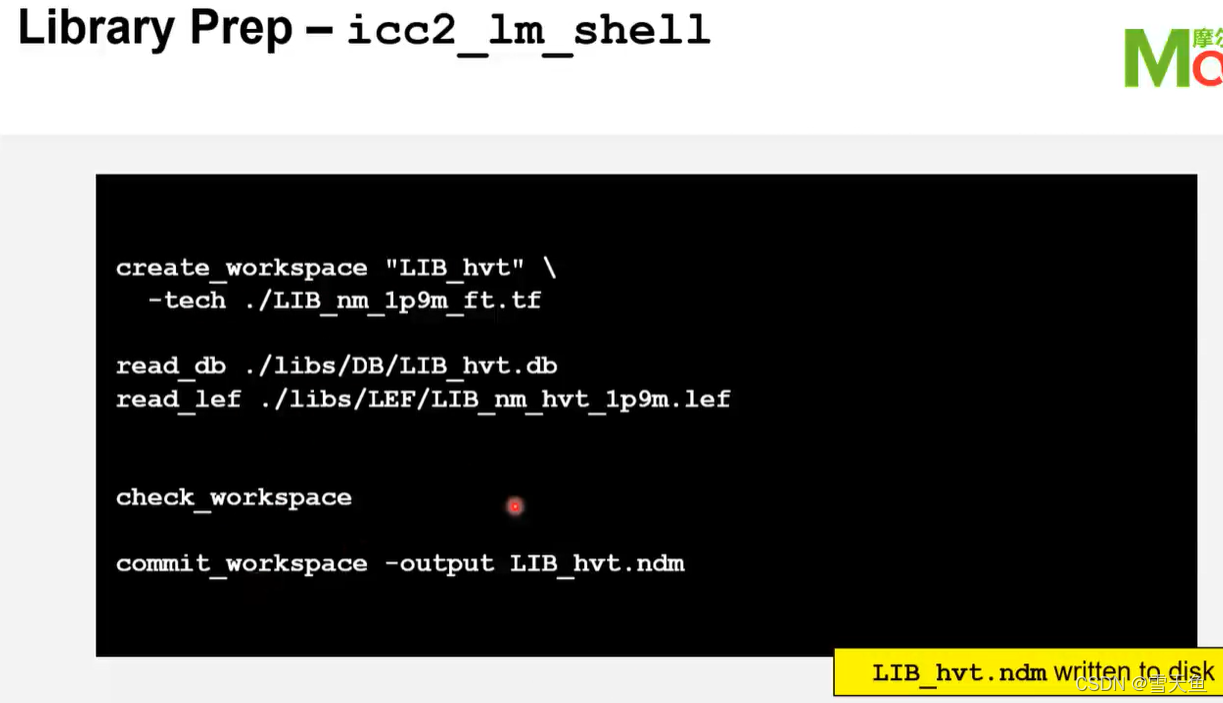

3.1 NDM Library Generation

使用流程:

示例:

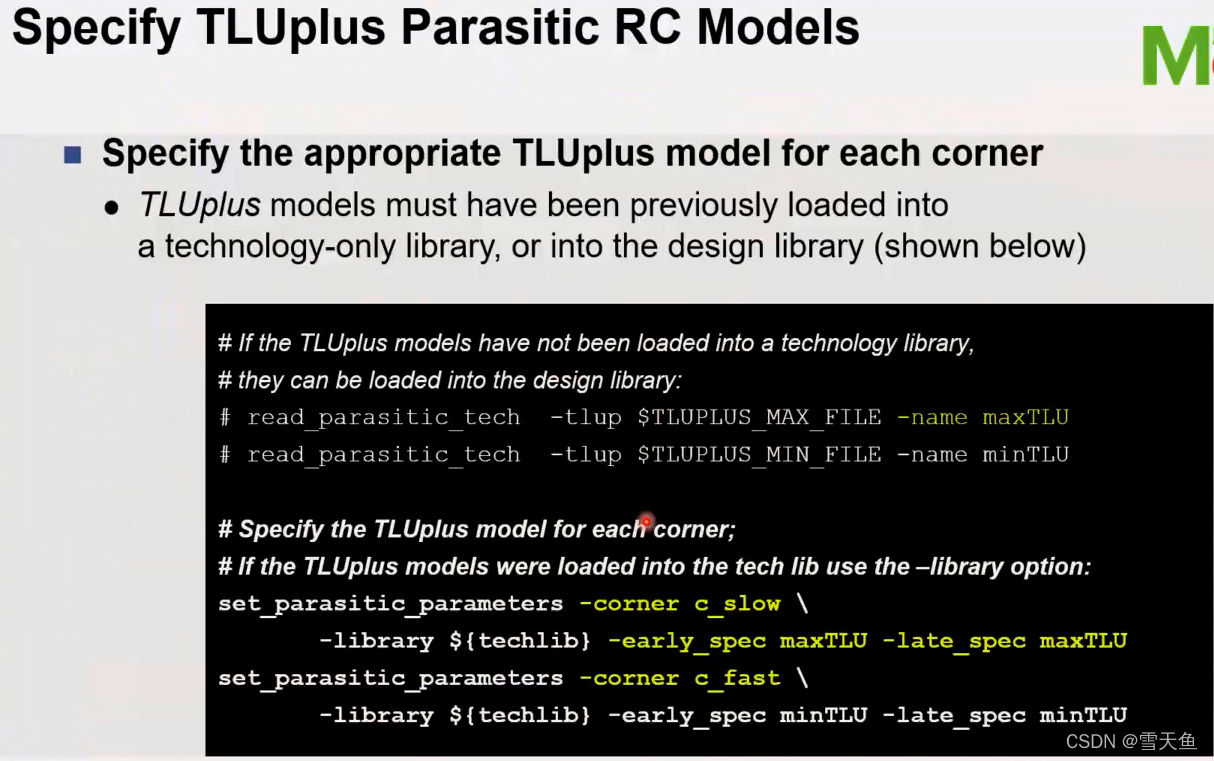

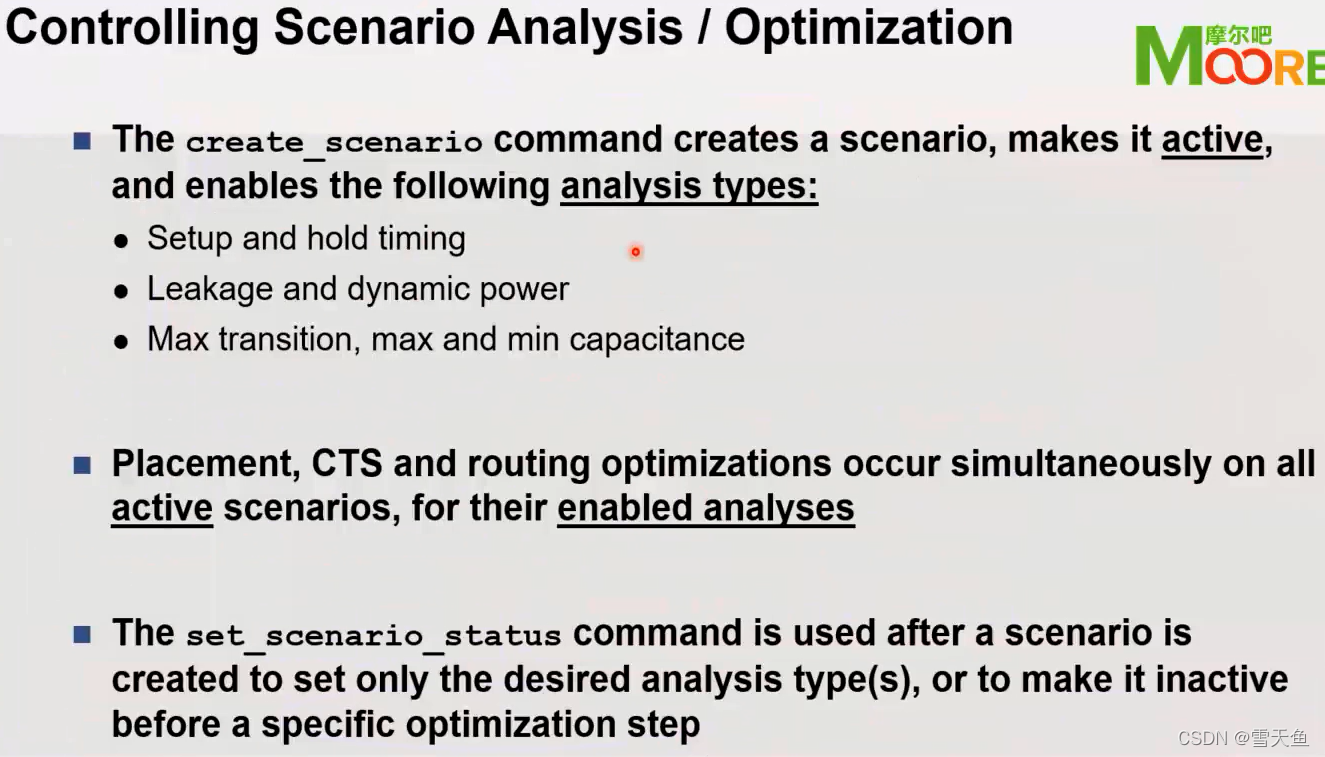

3.2 Design & Timing Setup

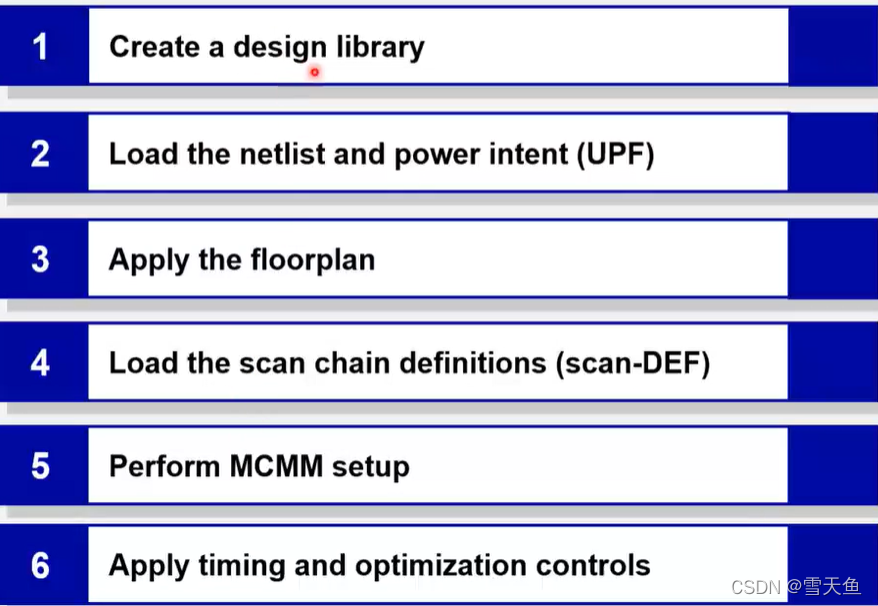

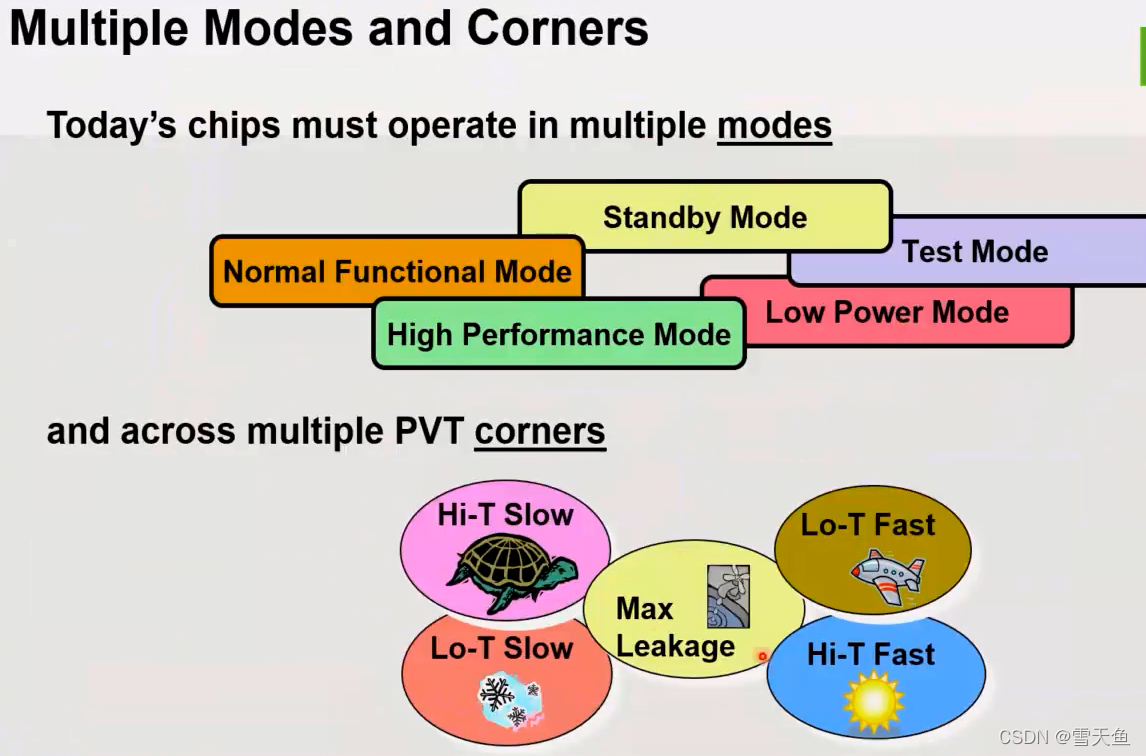

有了 NDM后,就可以进行 Design 和 Timing Setup,大致流程如下:

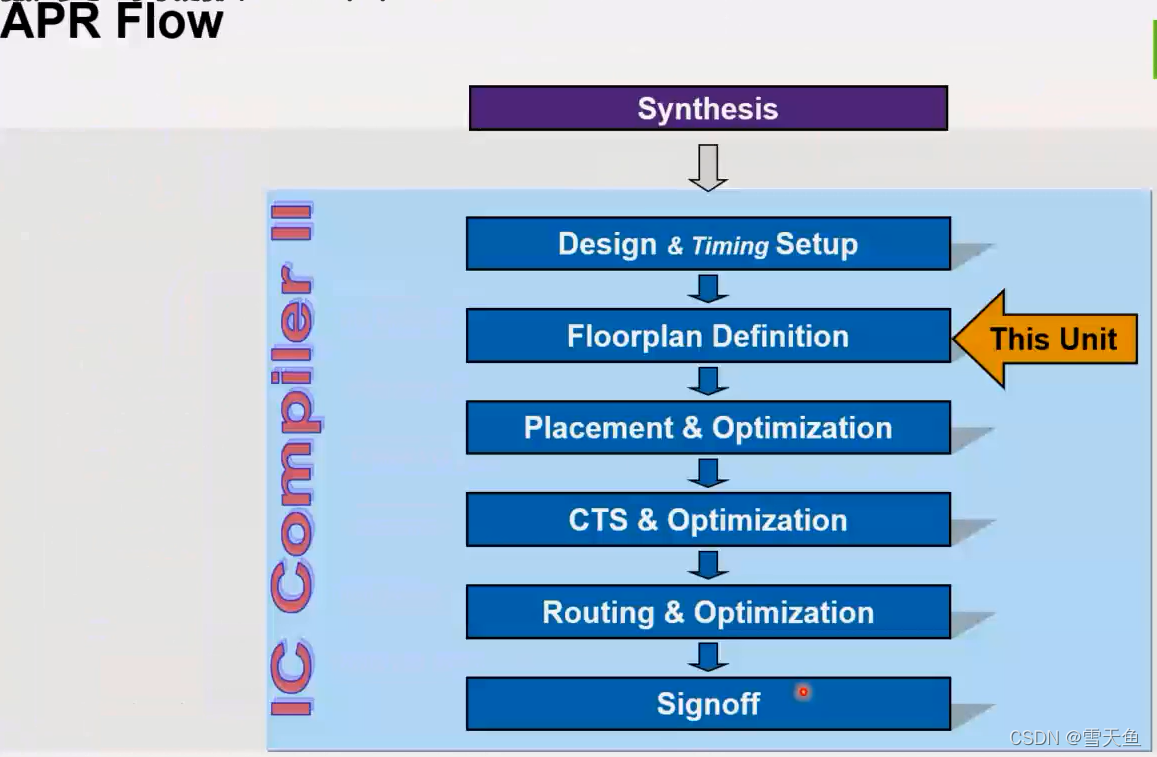

四、APR flow

名词解释

APR:是 Automatic place and route的缩写,即自动布局布线。

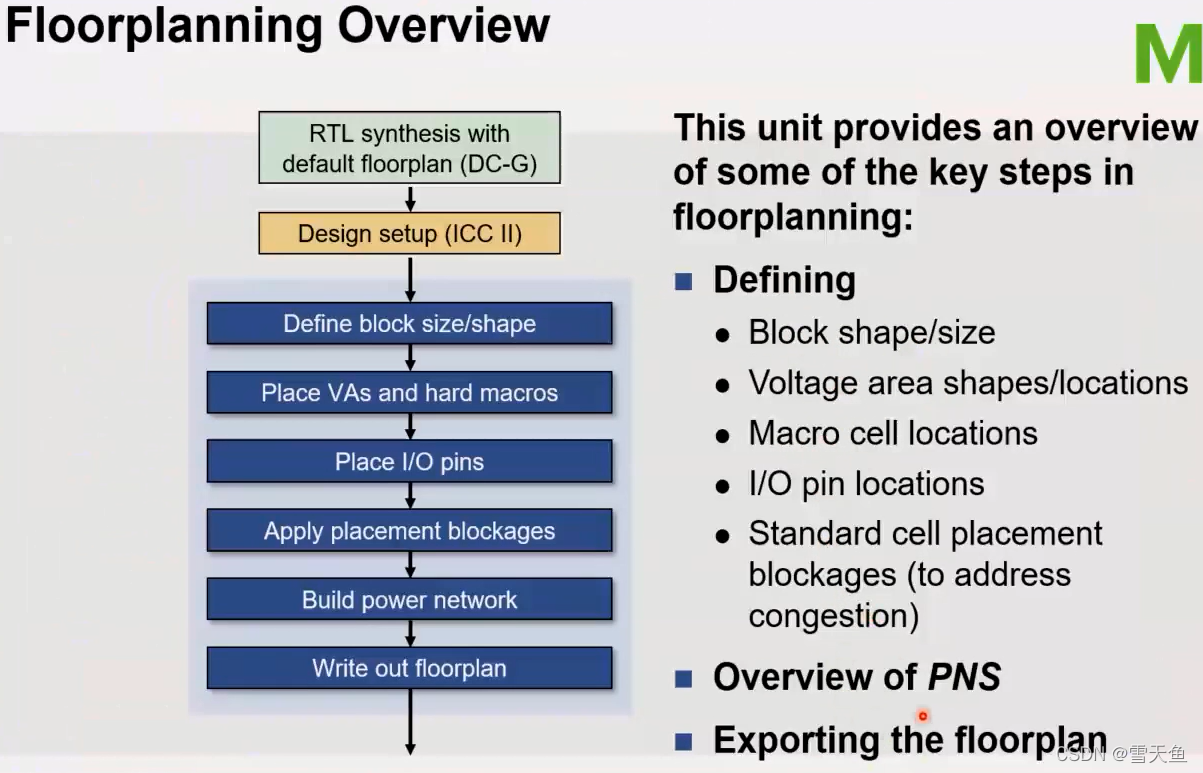

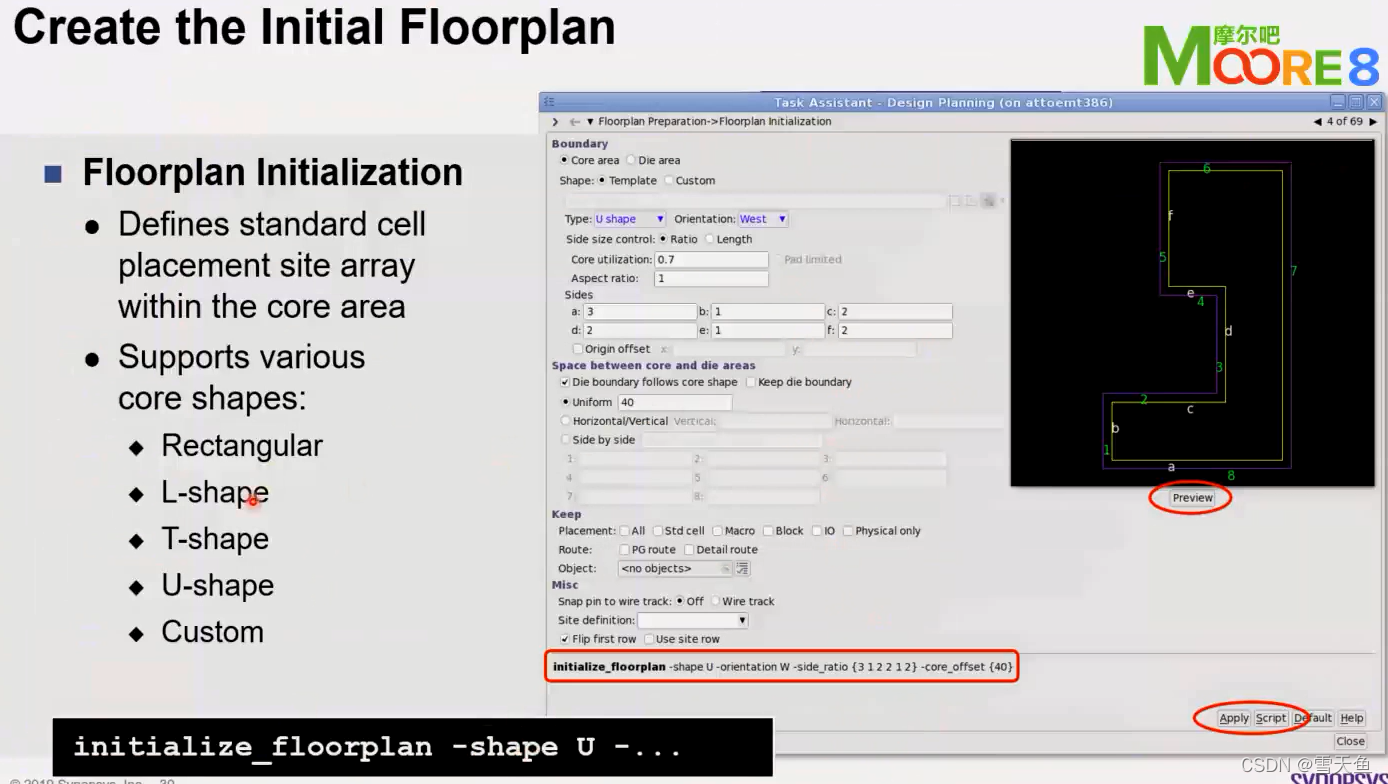

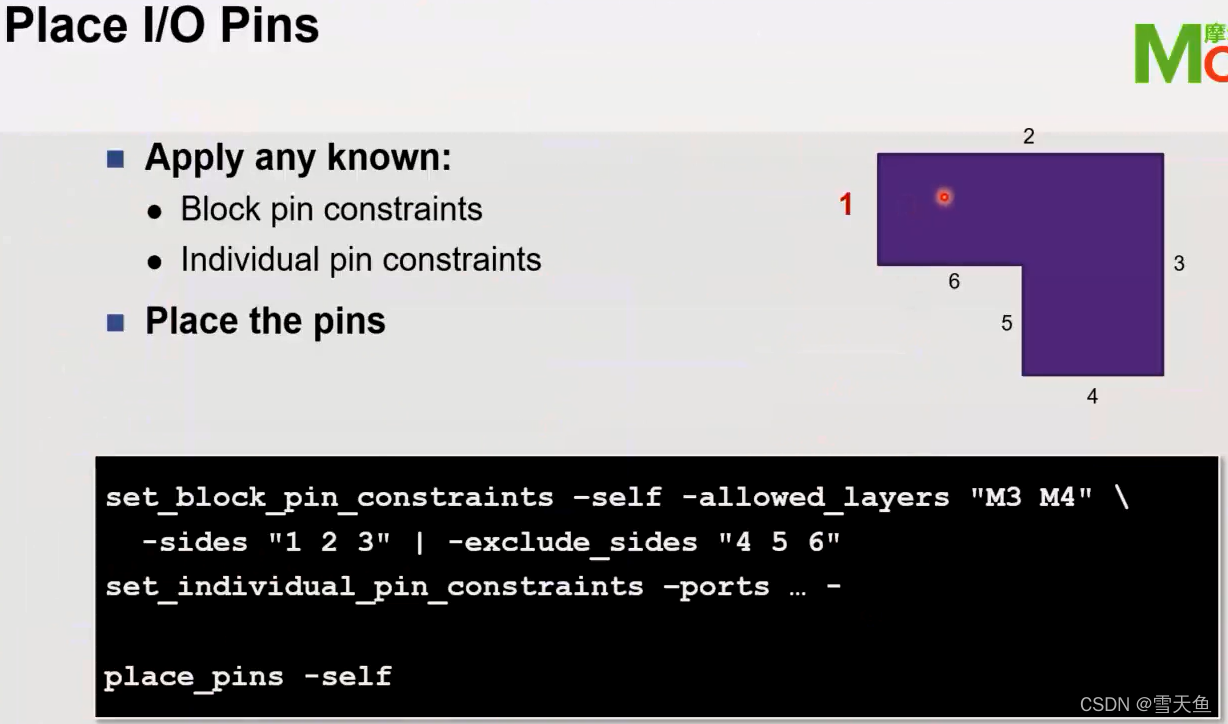

4.1 Floorplan Definition

Floorplan,中文翻译是布局规划。位于后端设计的最前端。

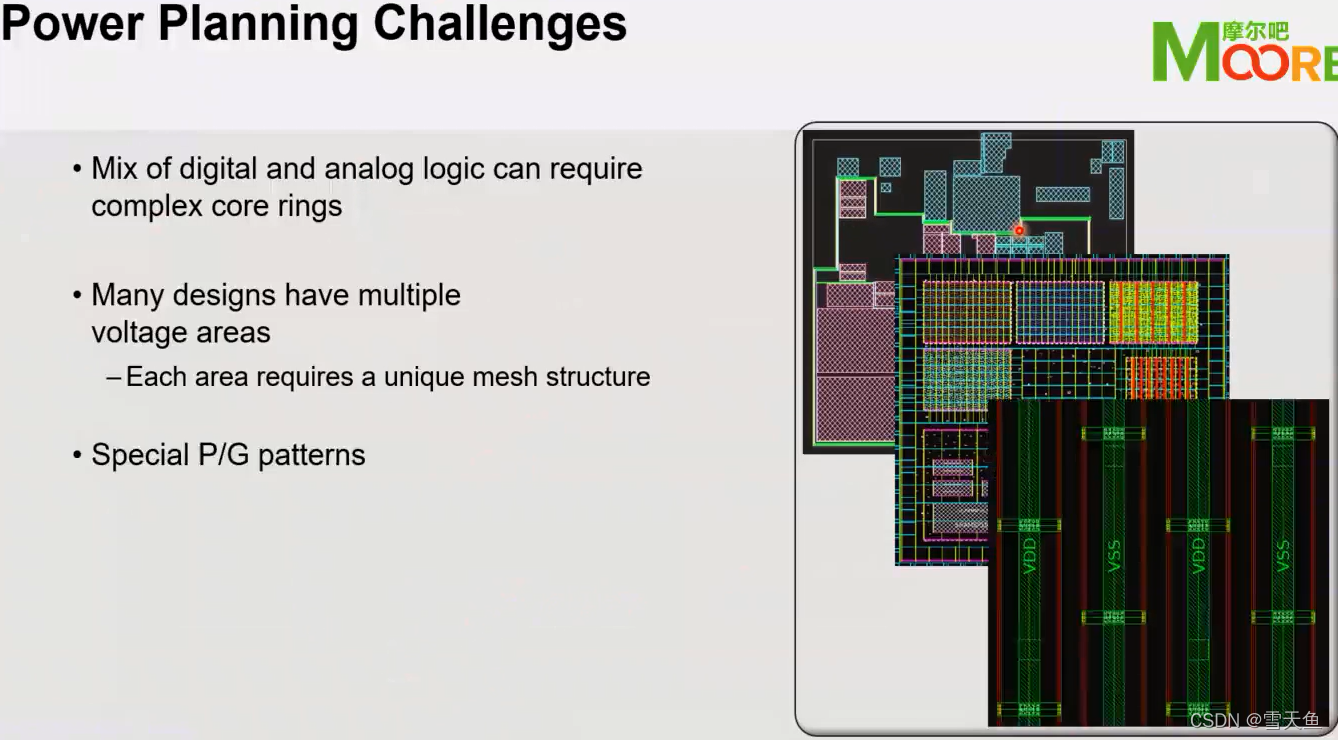

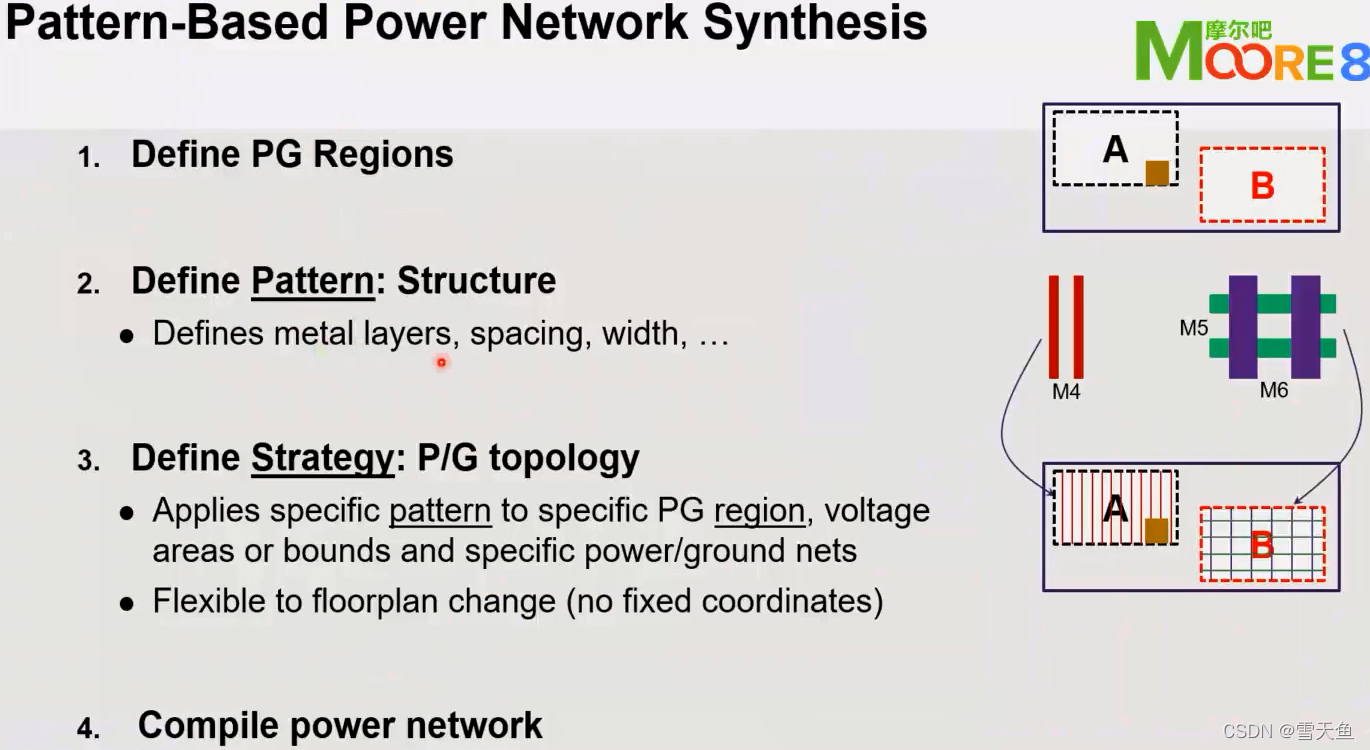

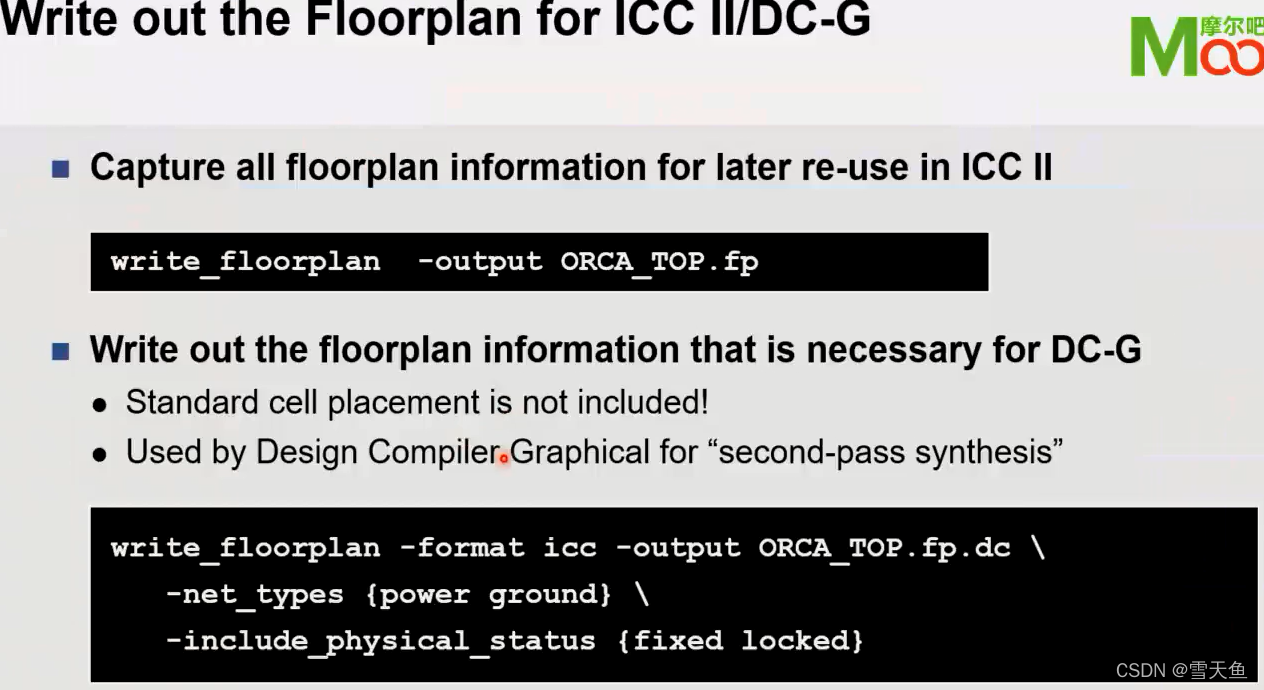

把元素都摆放好后进行电源网络设计:

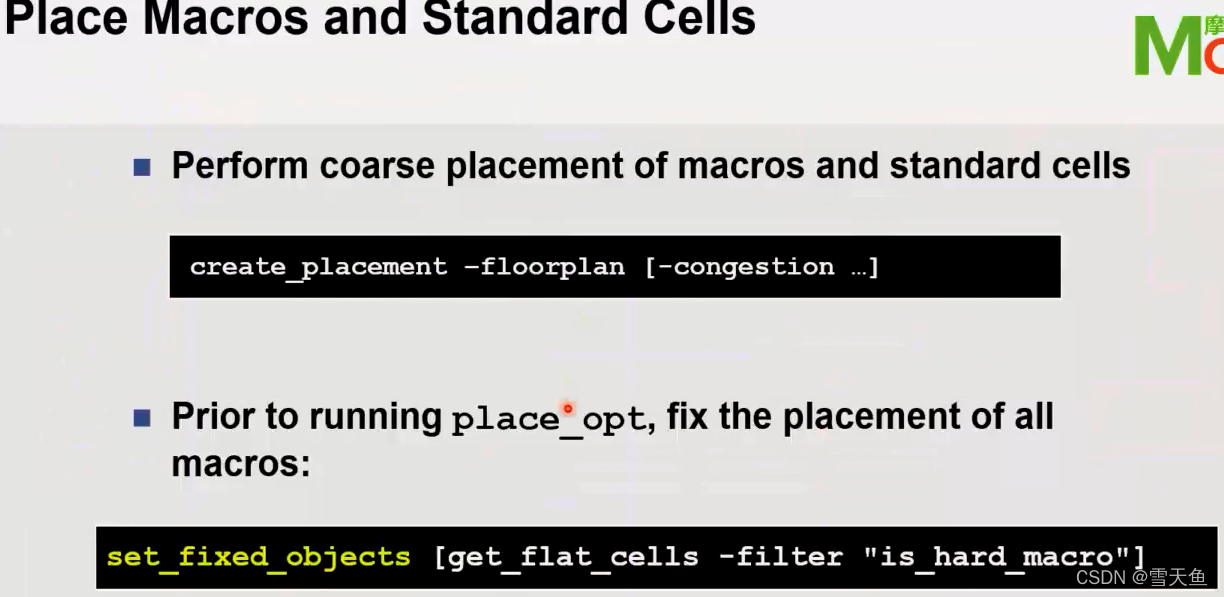

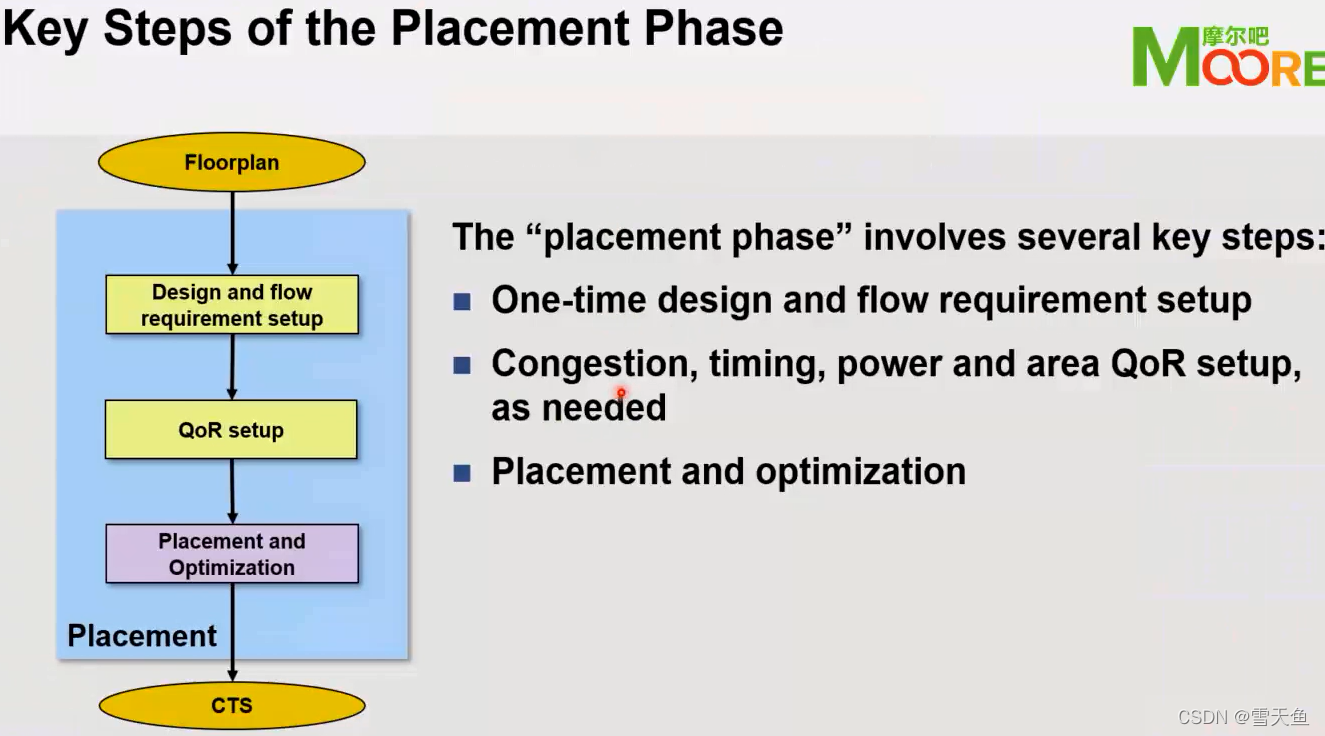

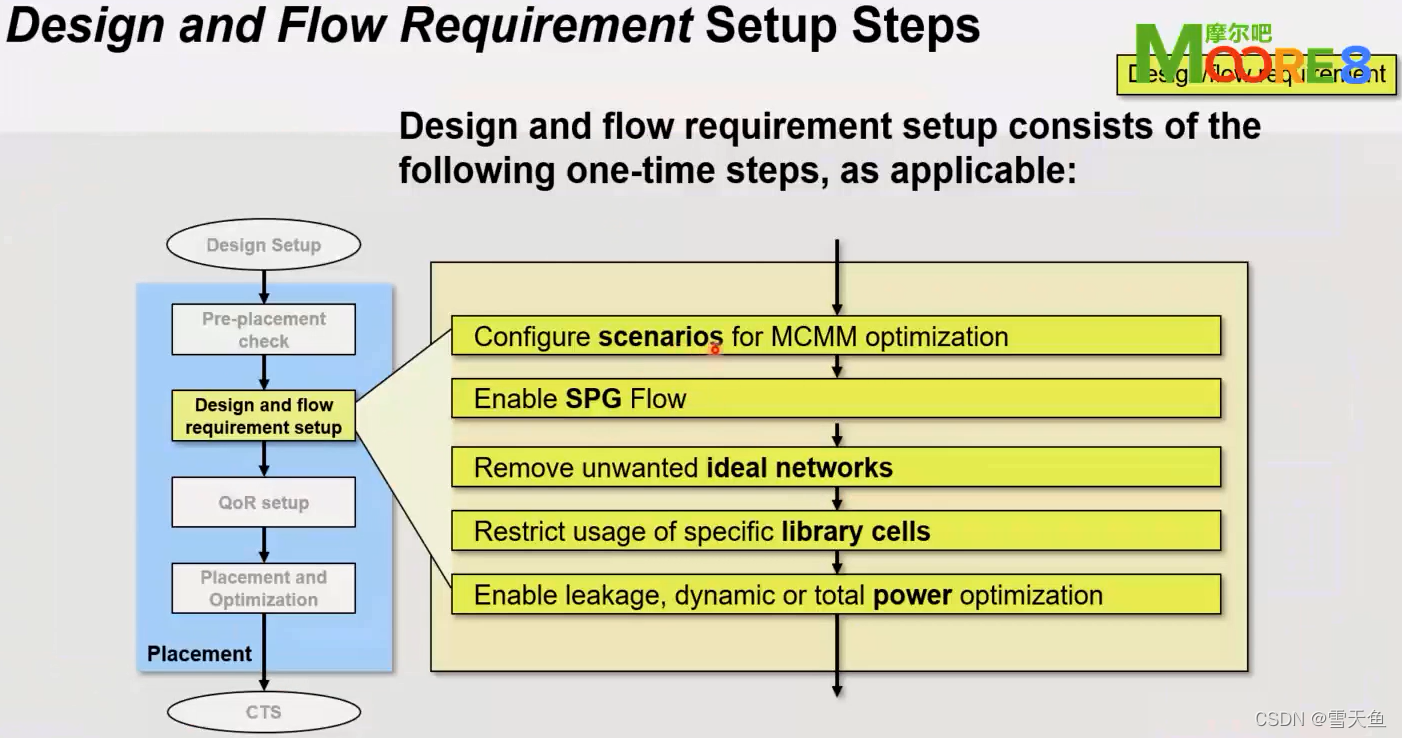

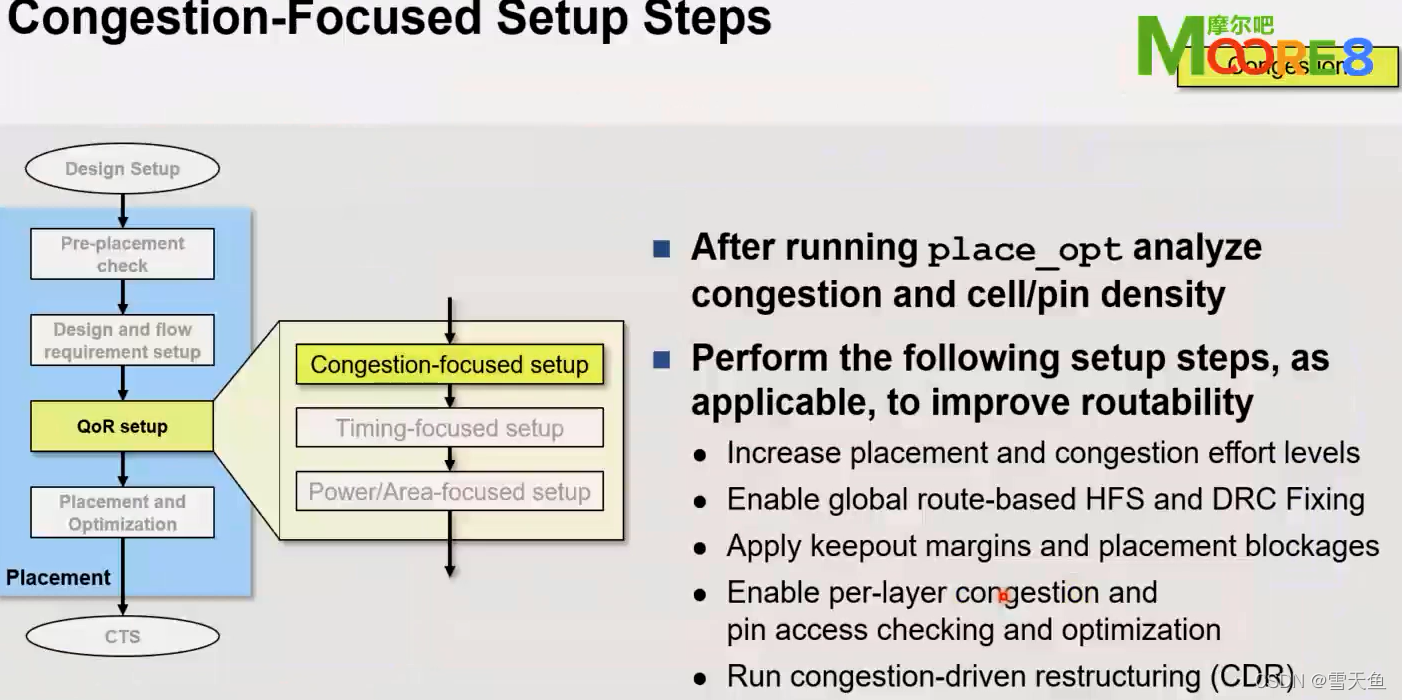

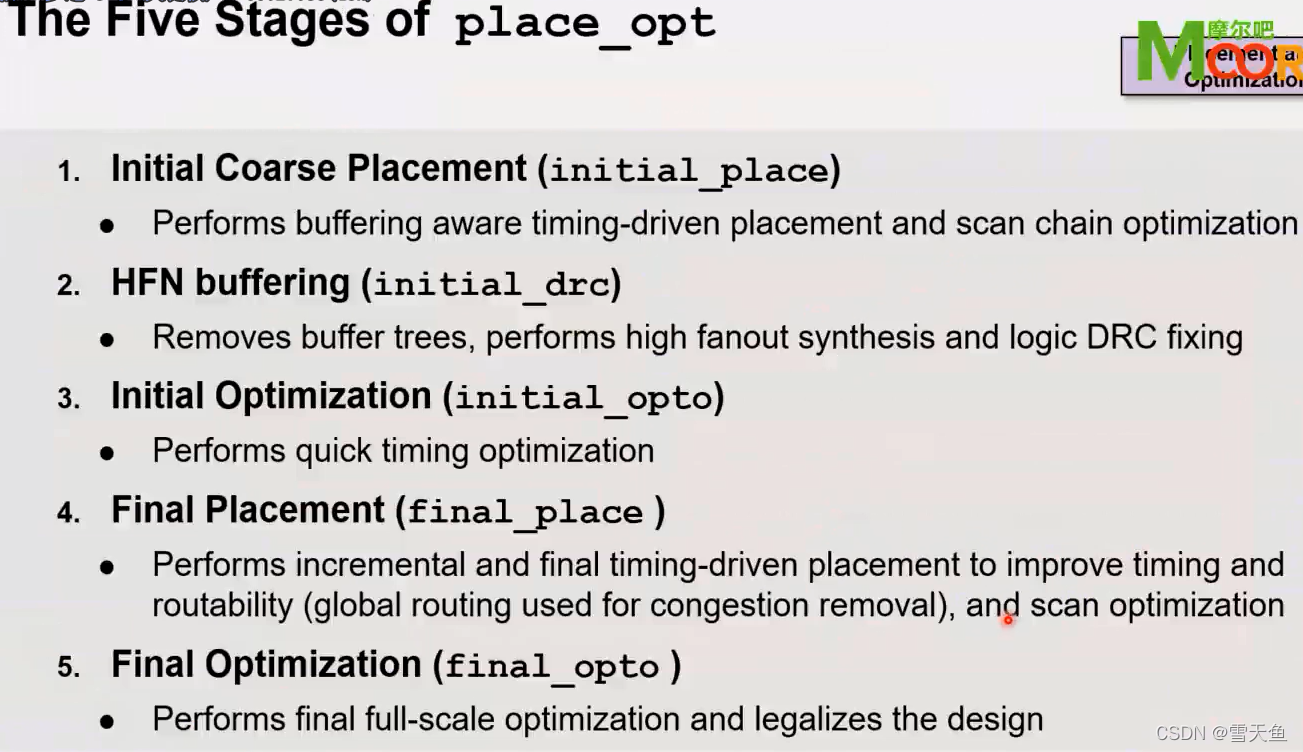

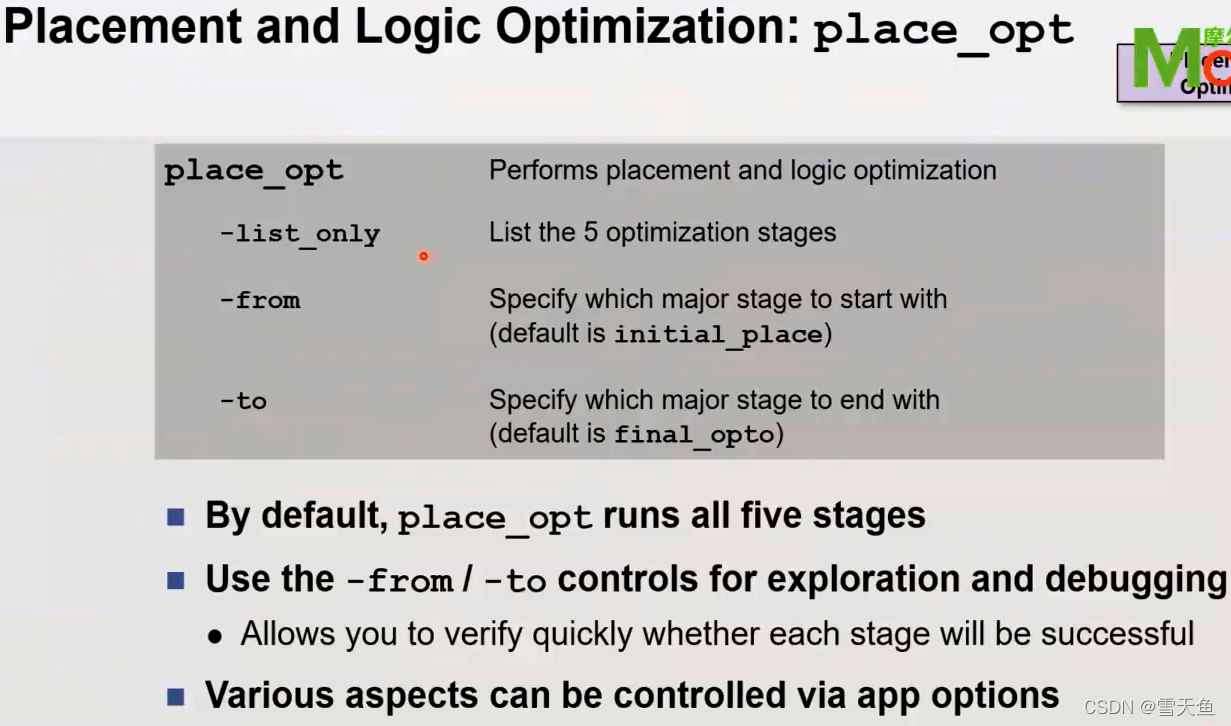

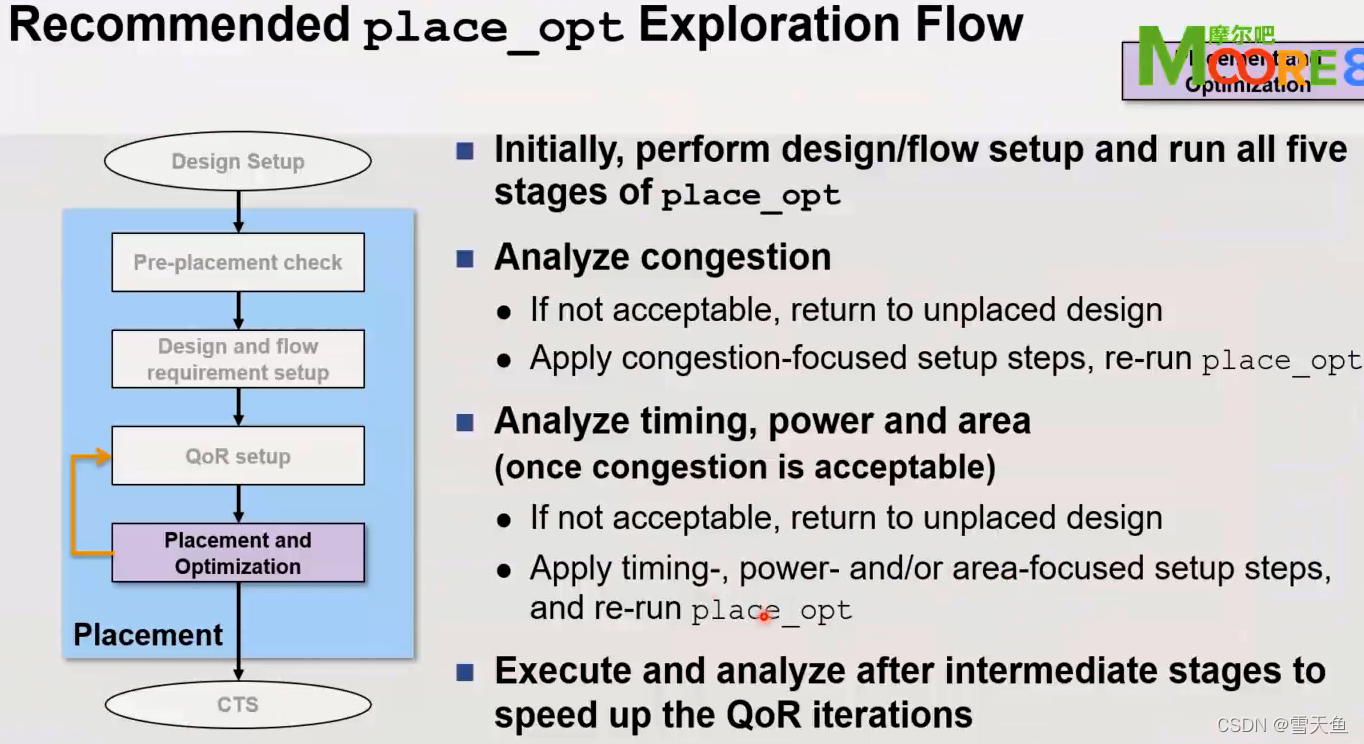

4.2 Placement & Optimization

4.3 CTS & Optimization

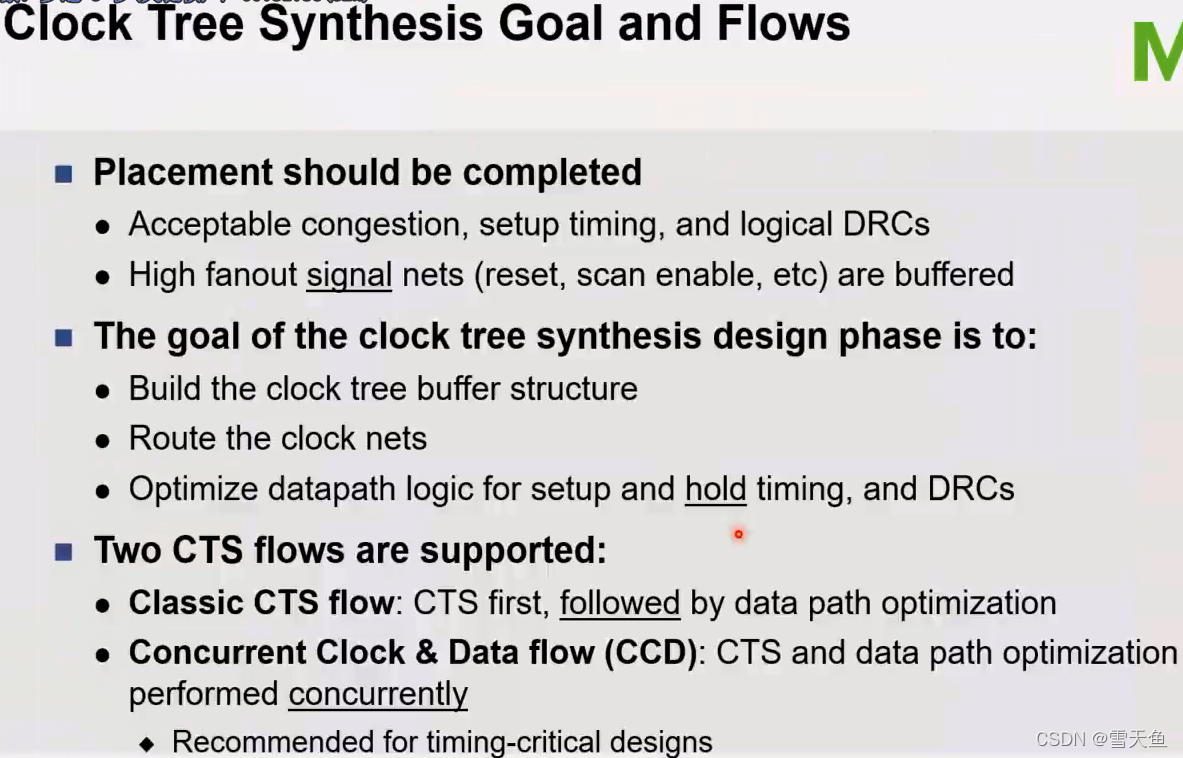

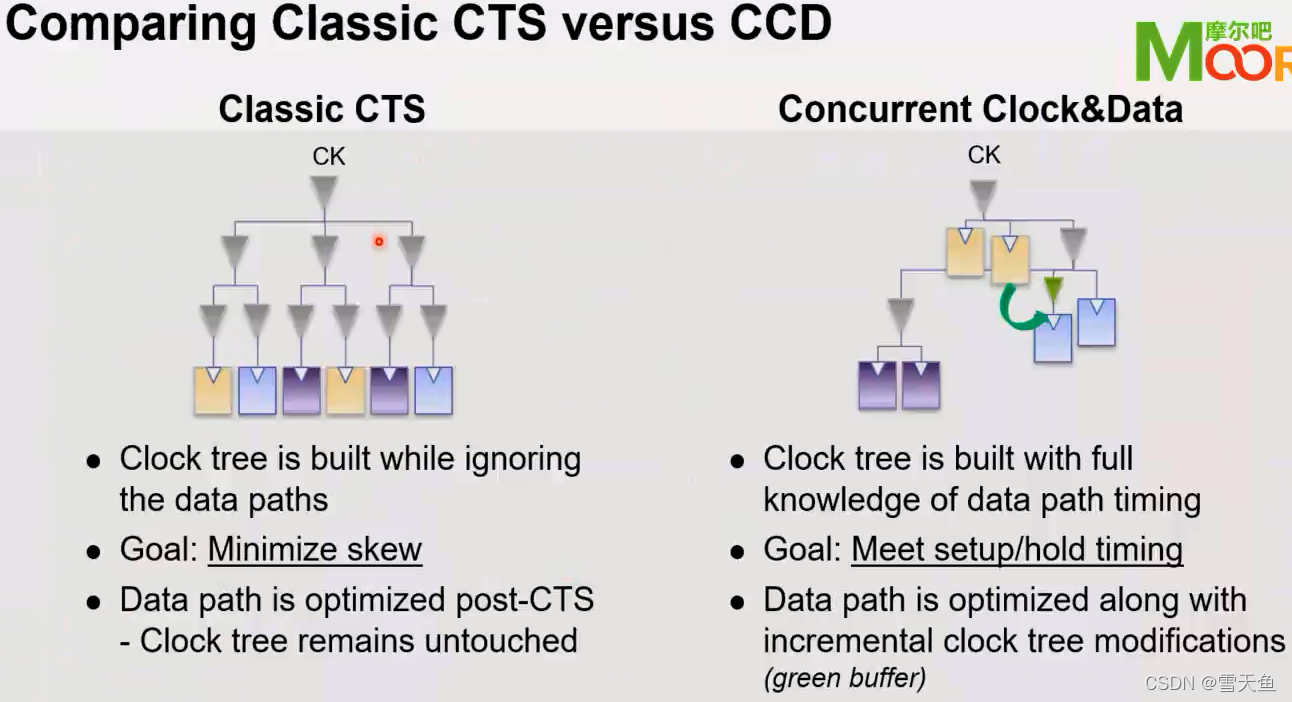

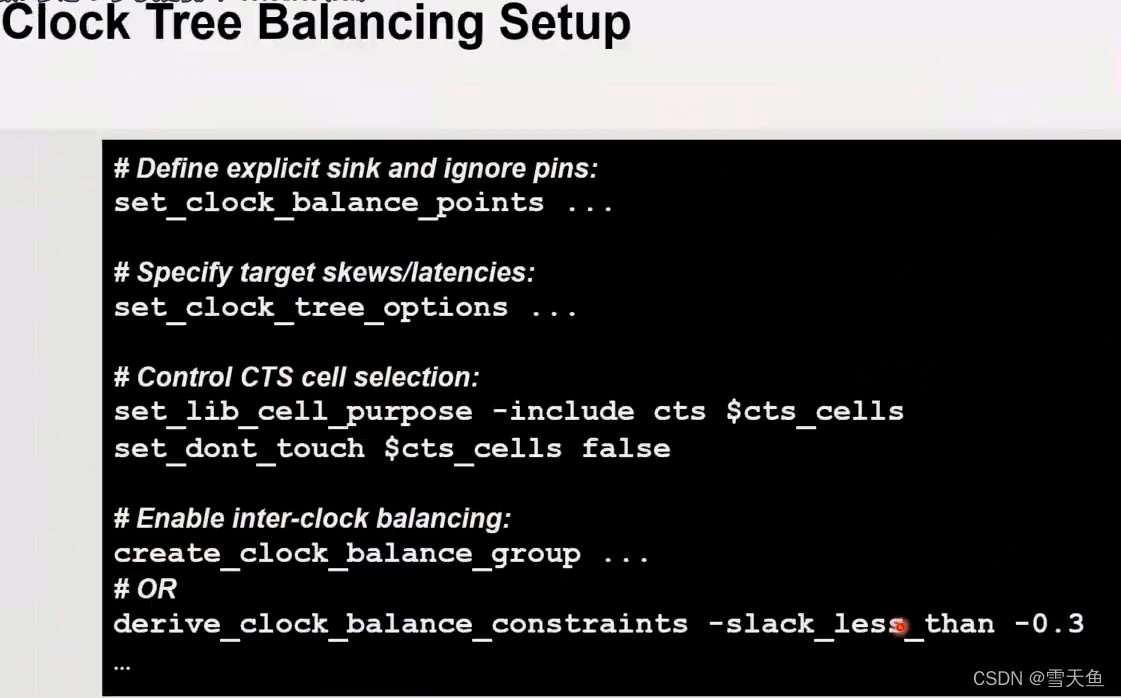

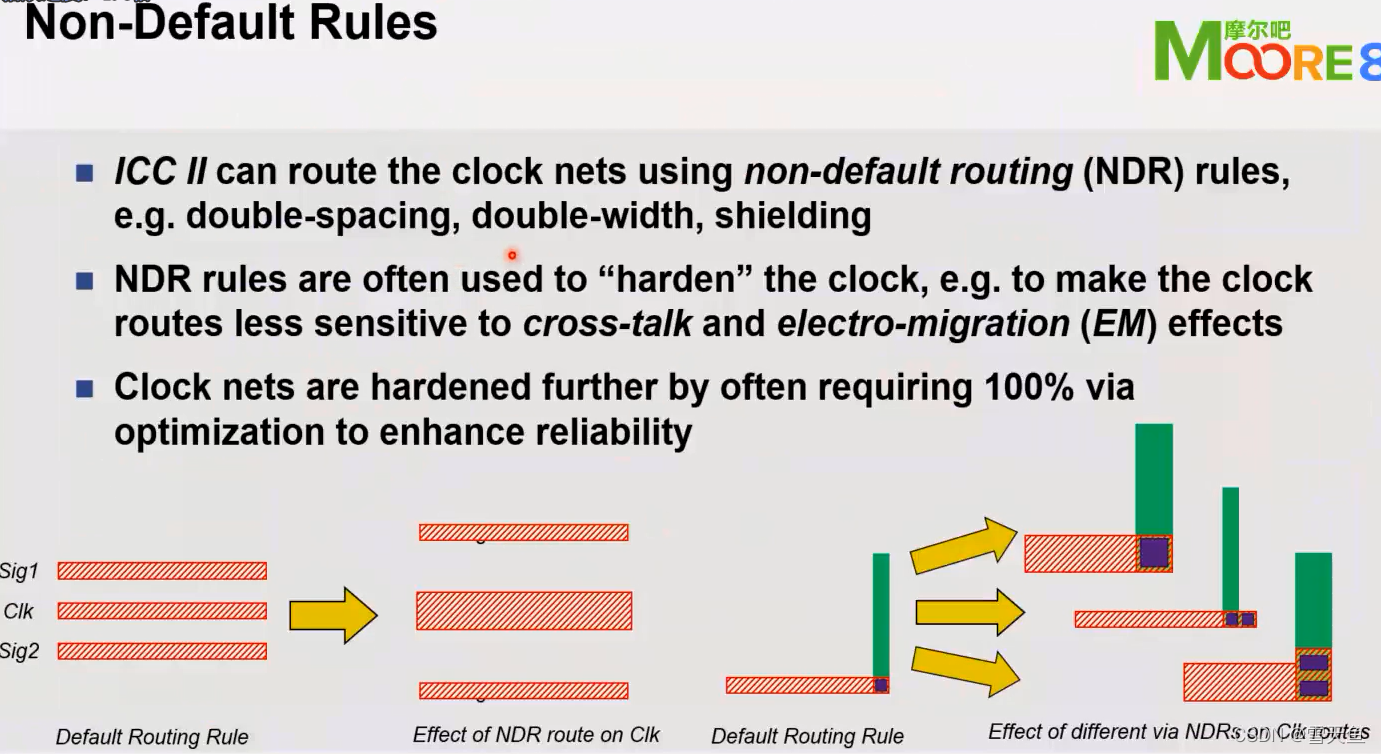

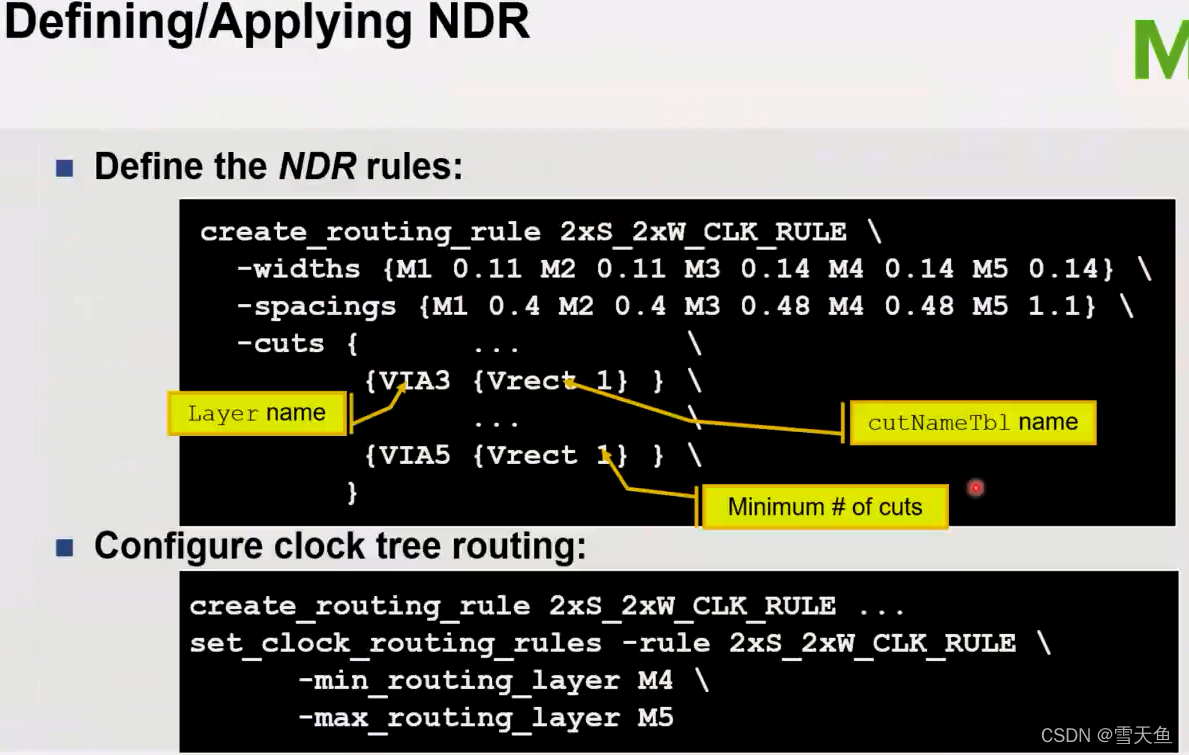

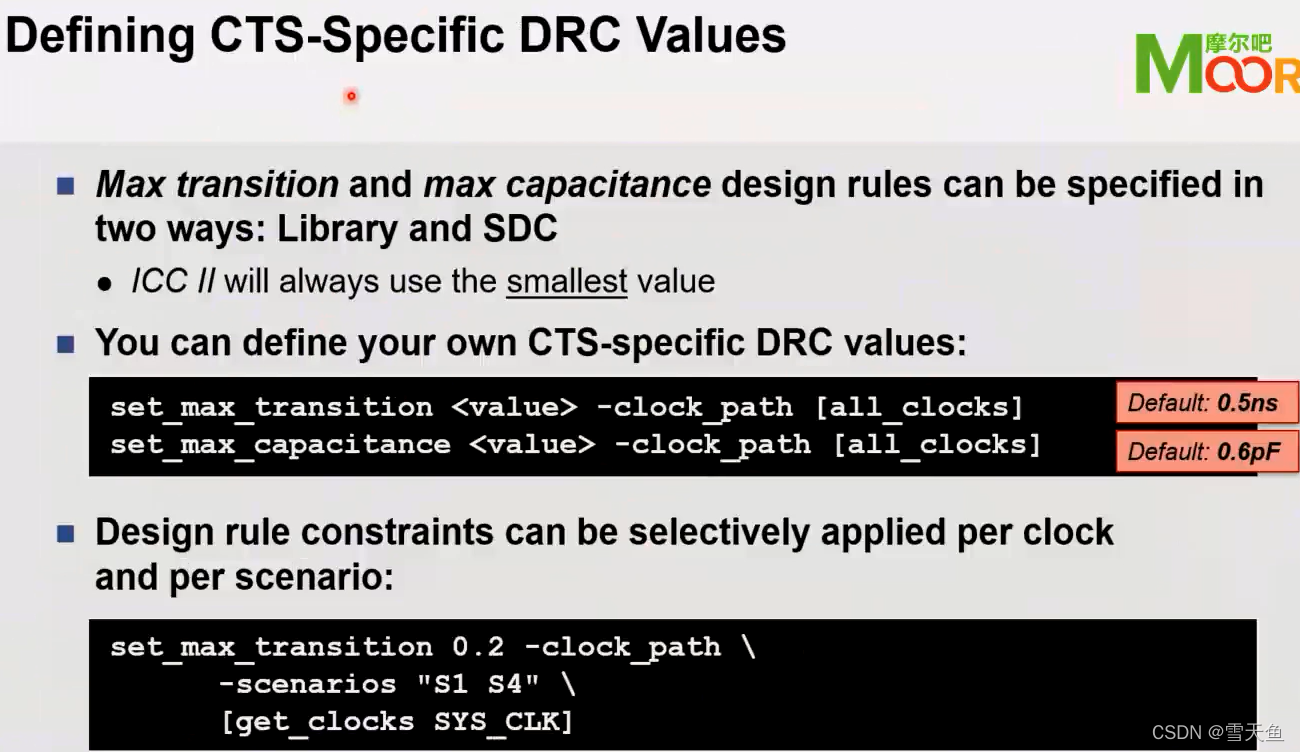

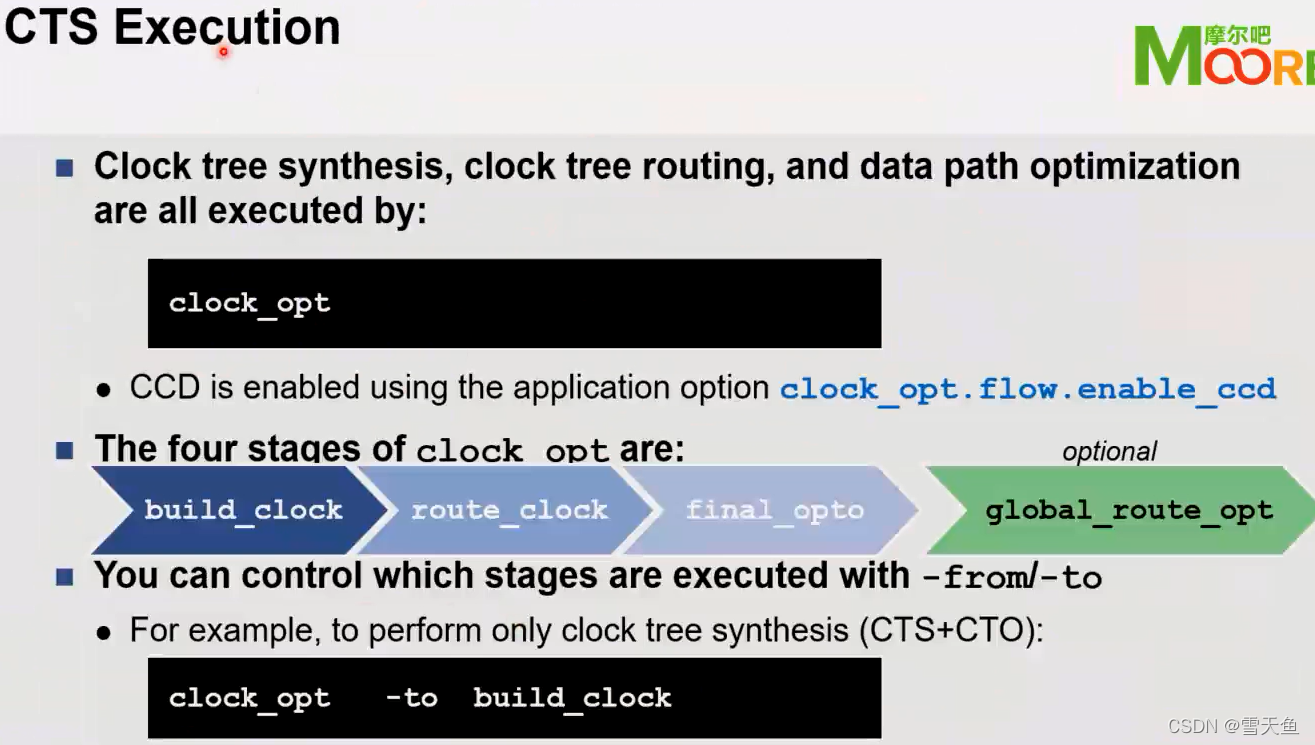

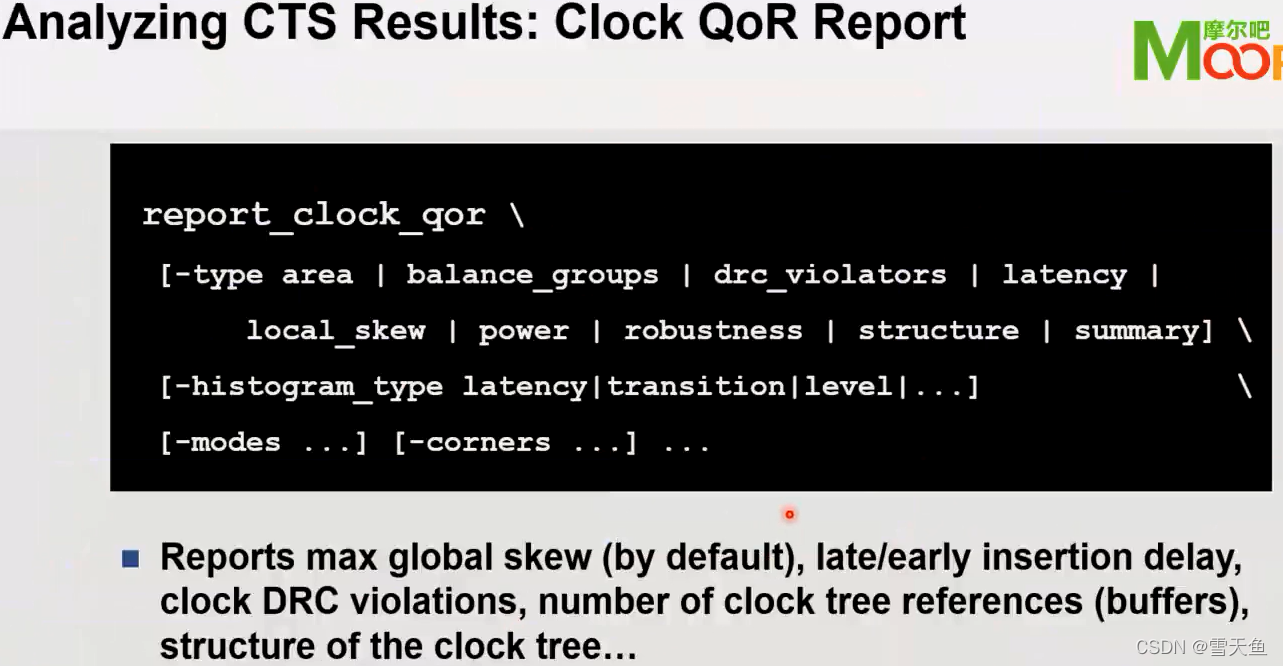

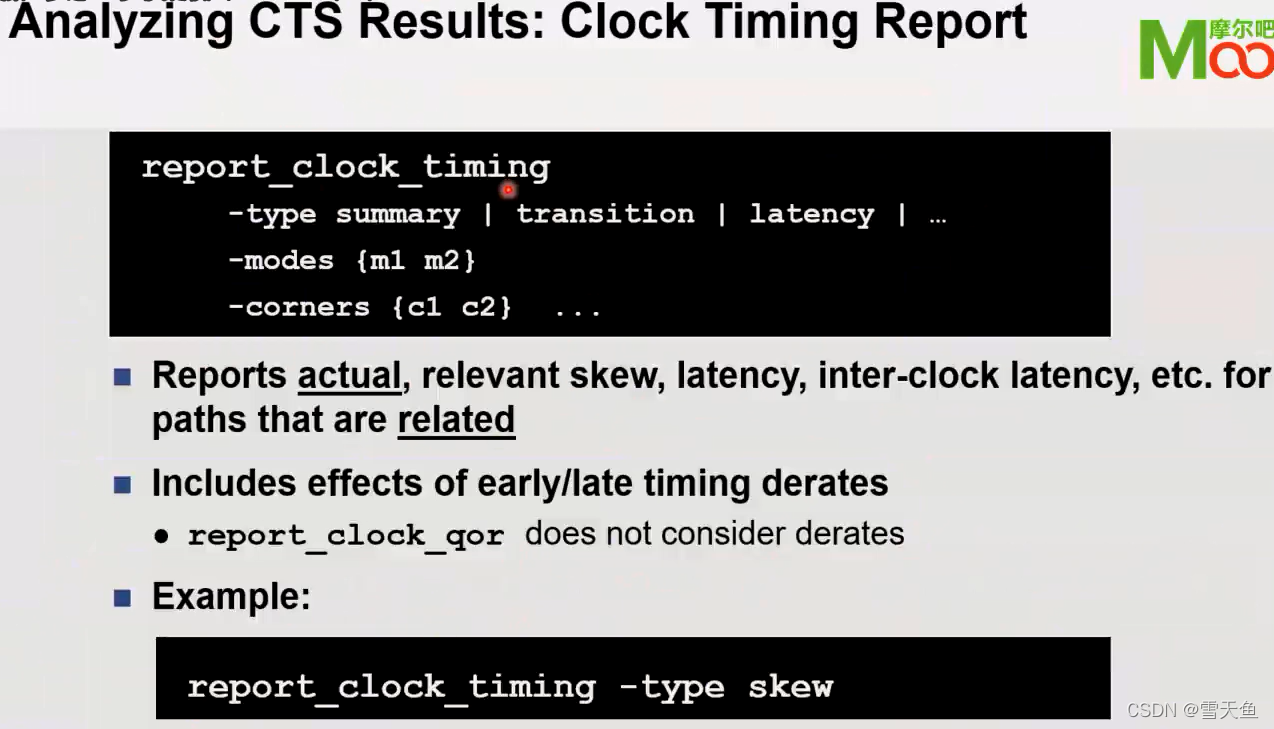

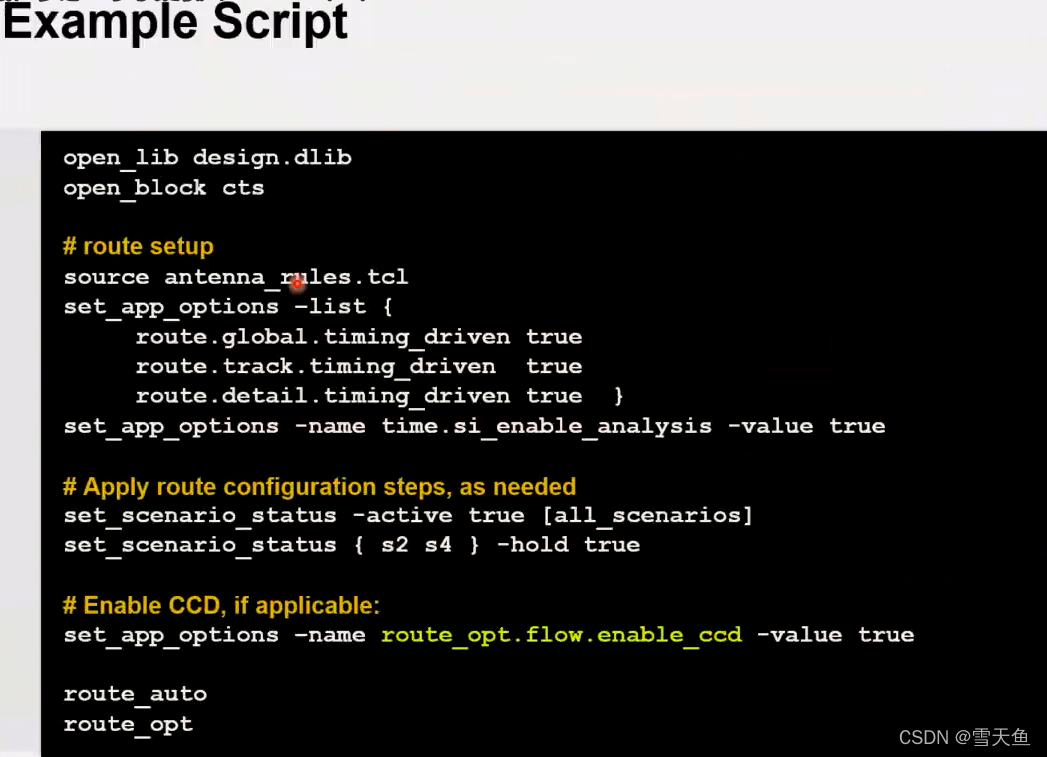

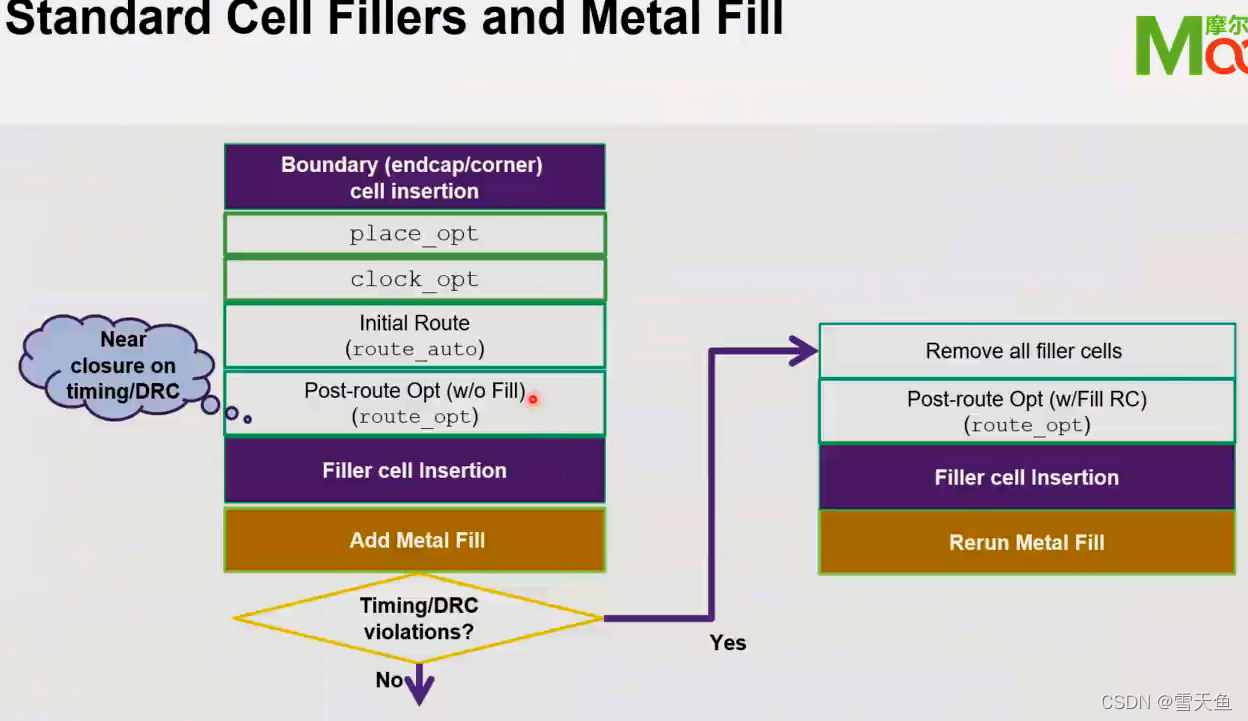

4.4 Routing & Optimization

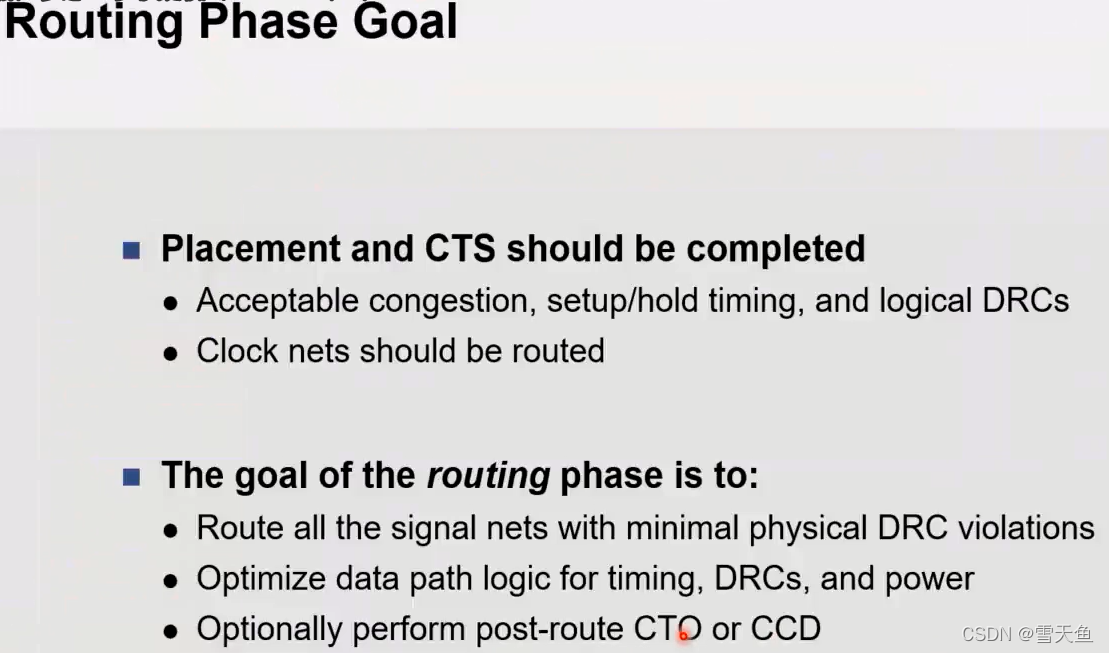

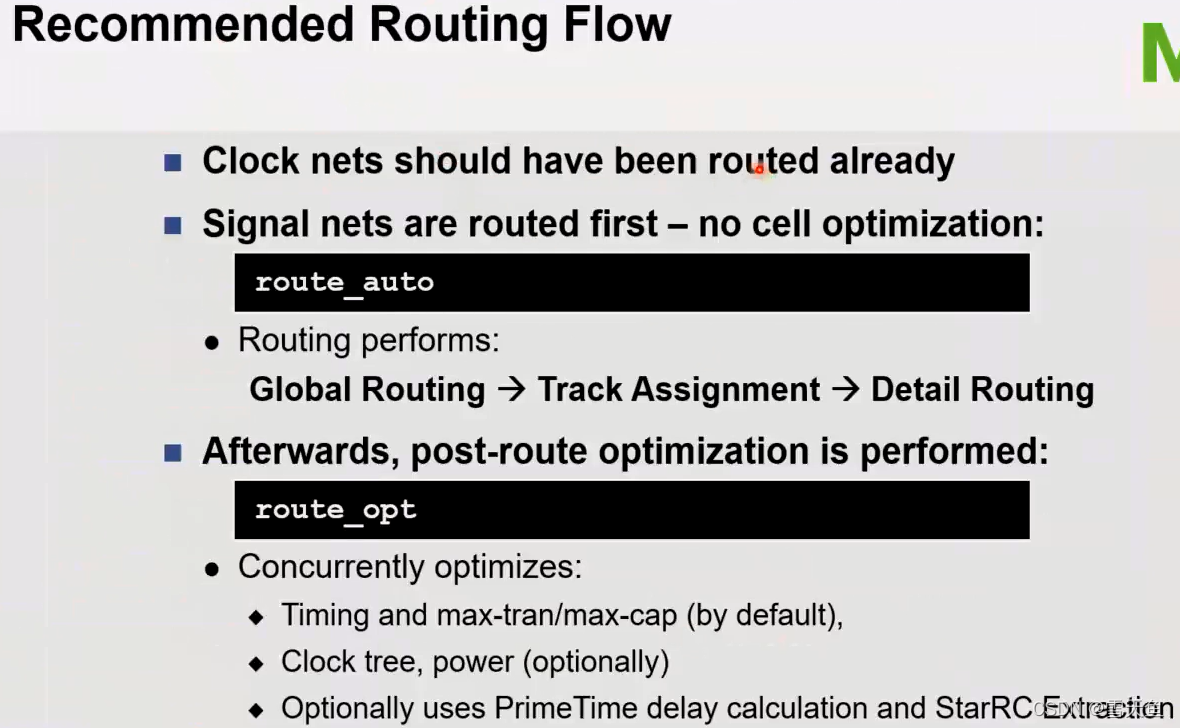

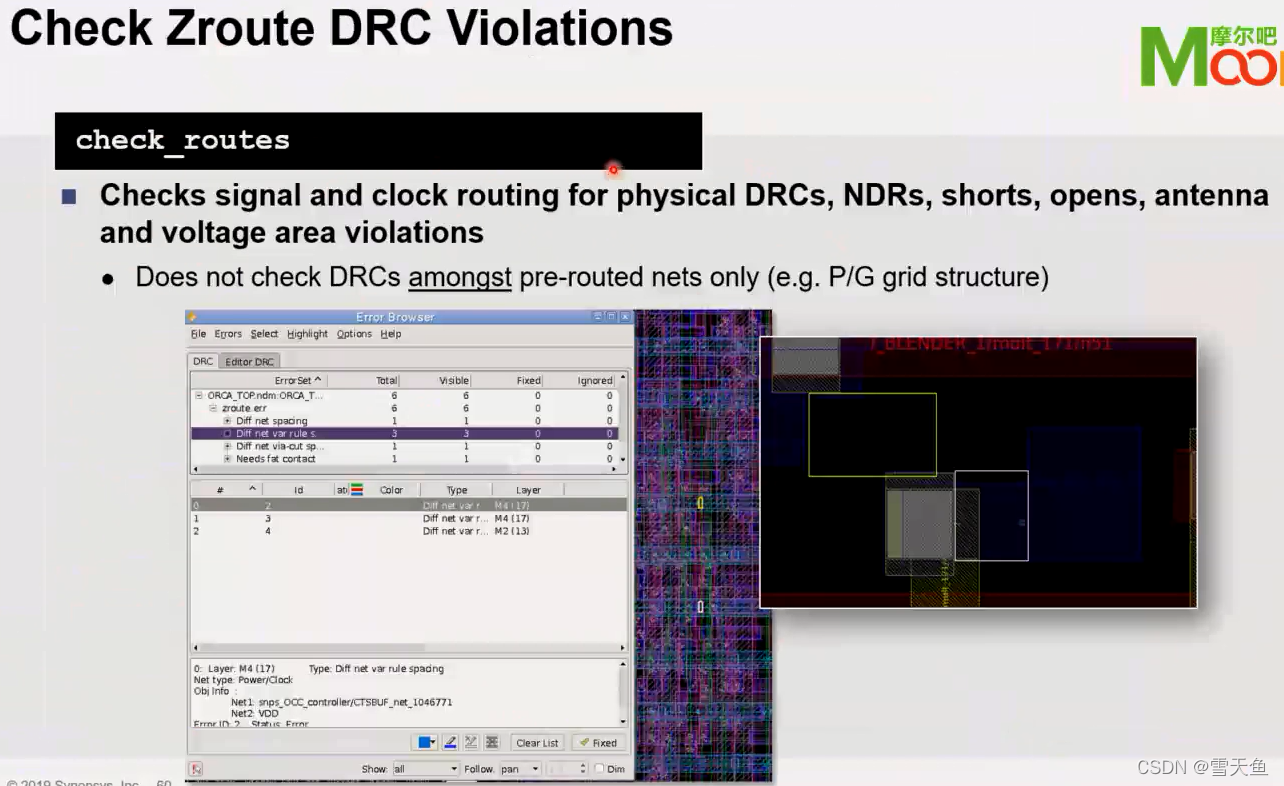

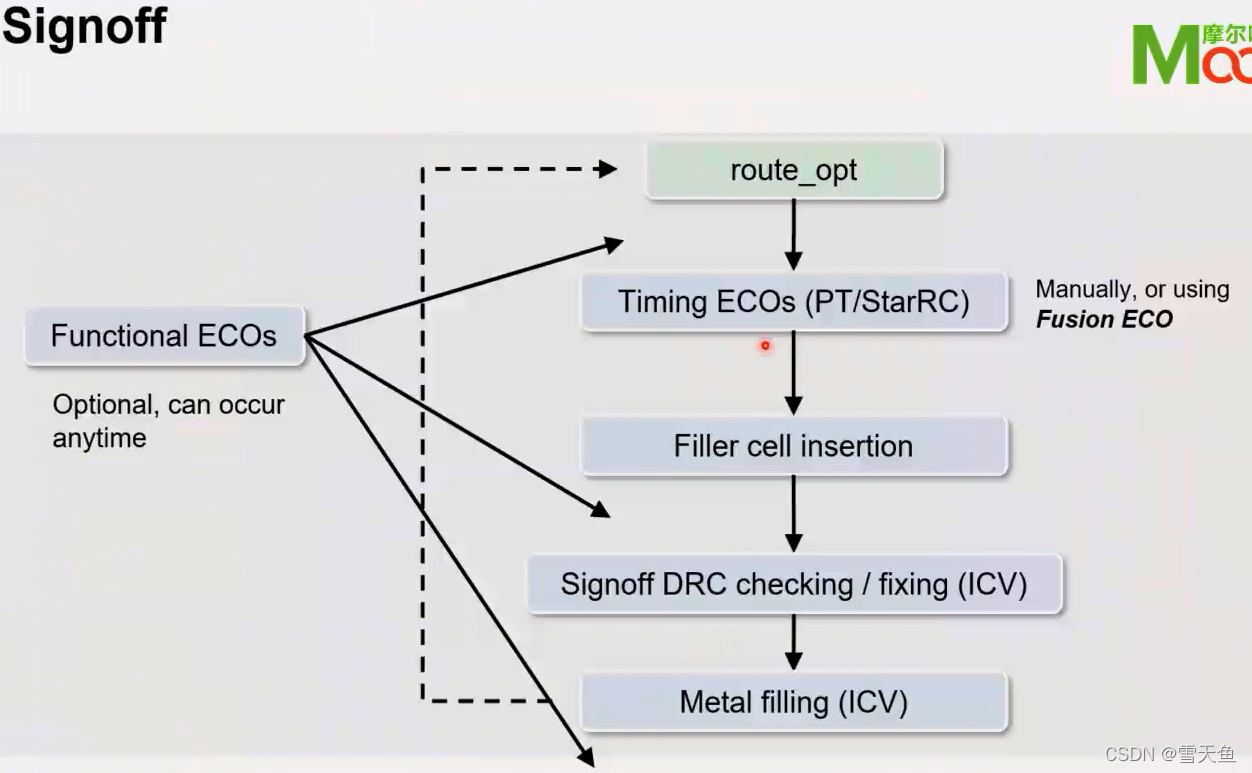

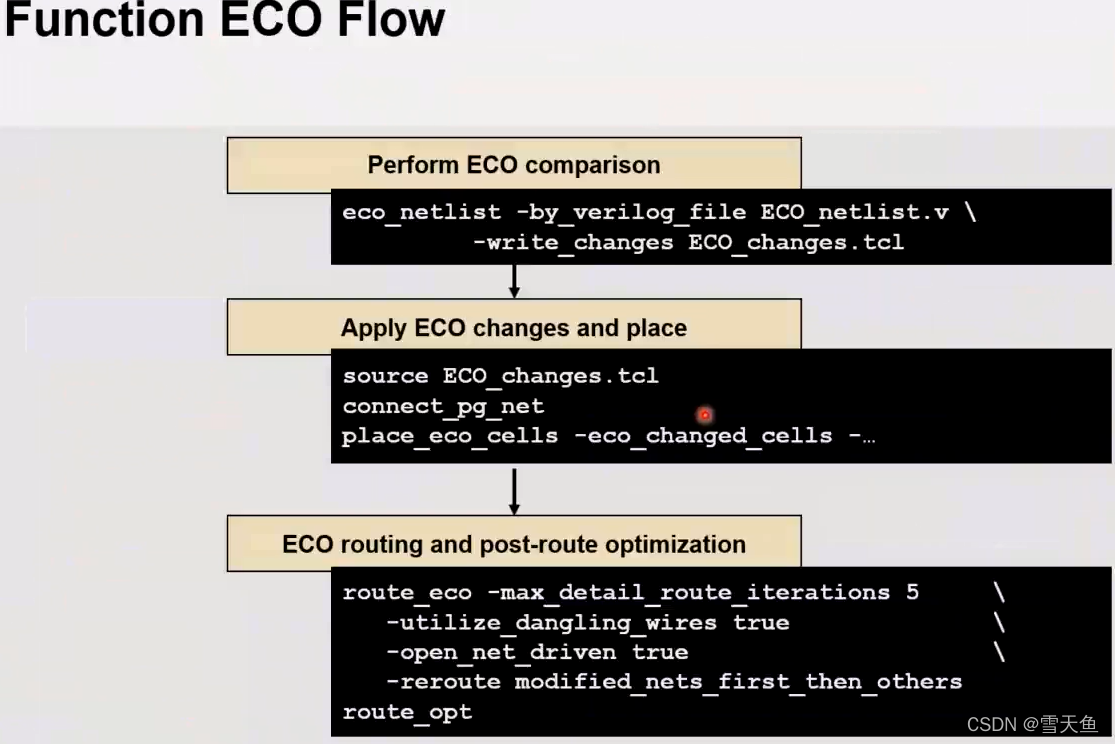

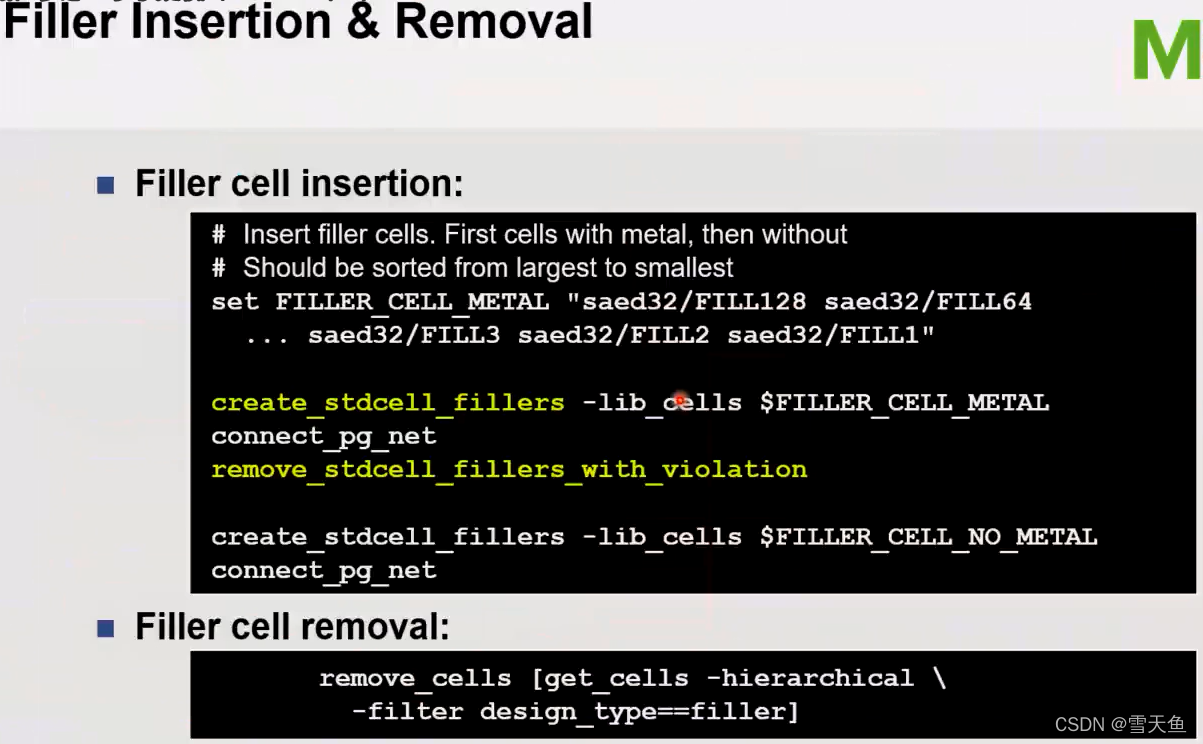

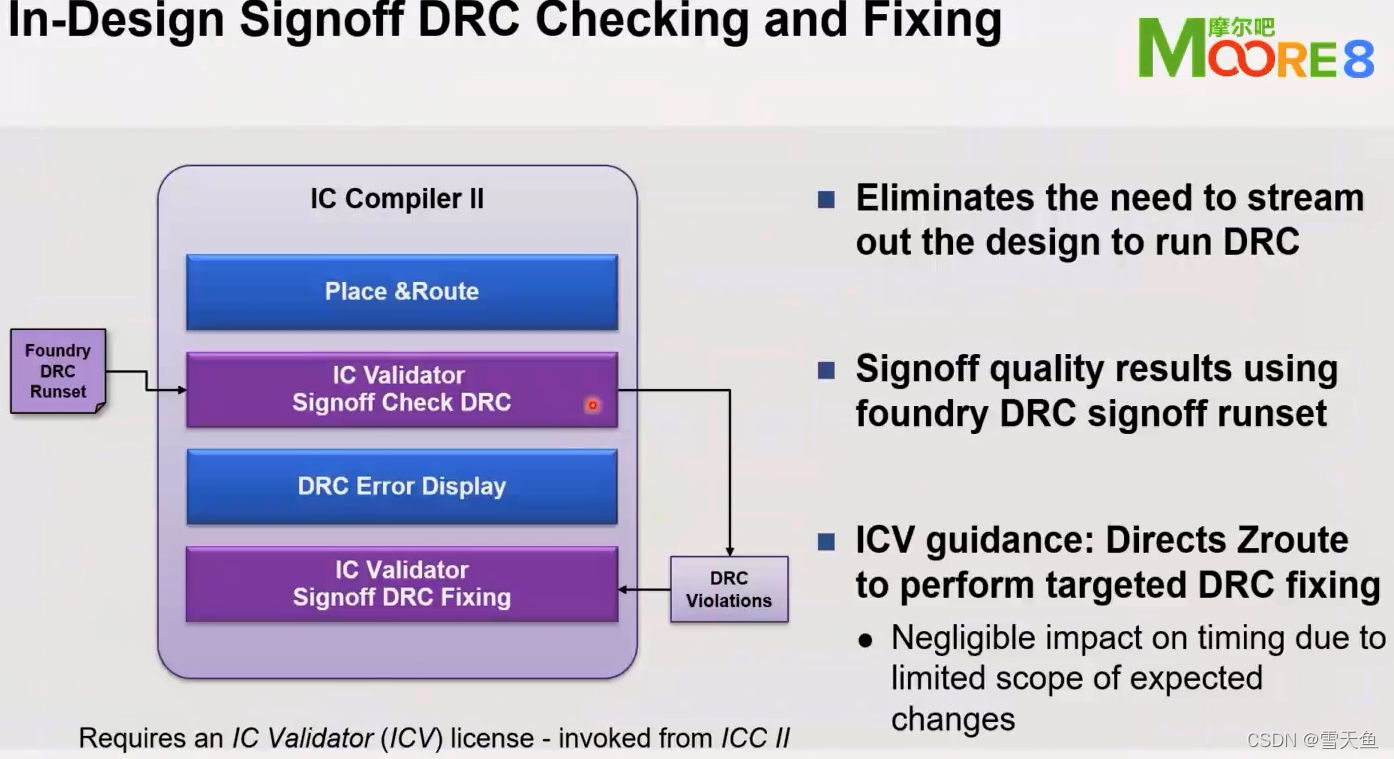

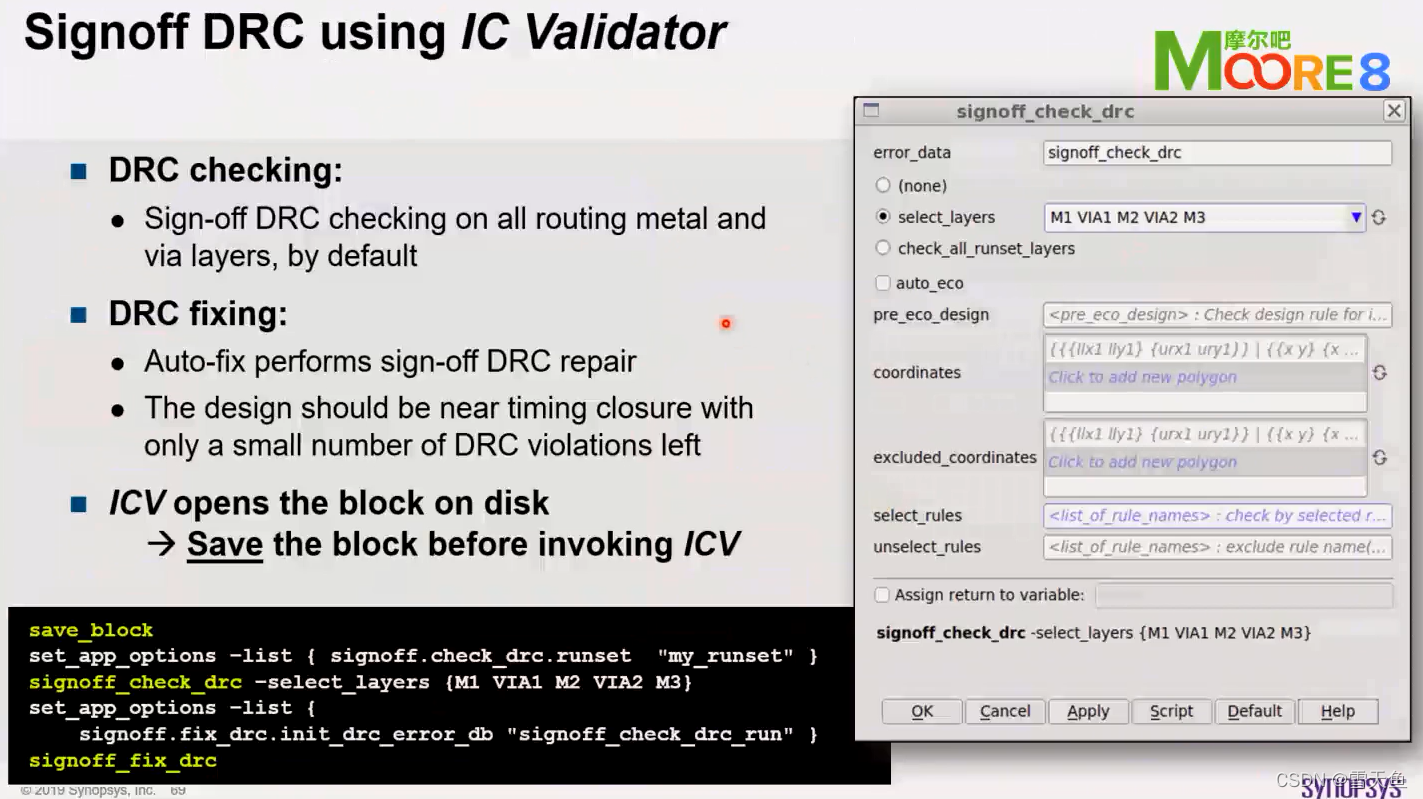

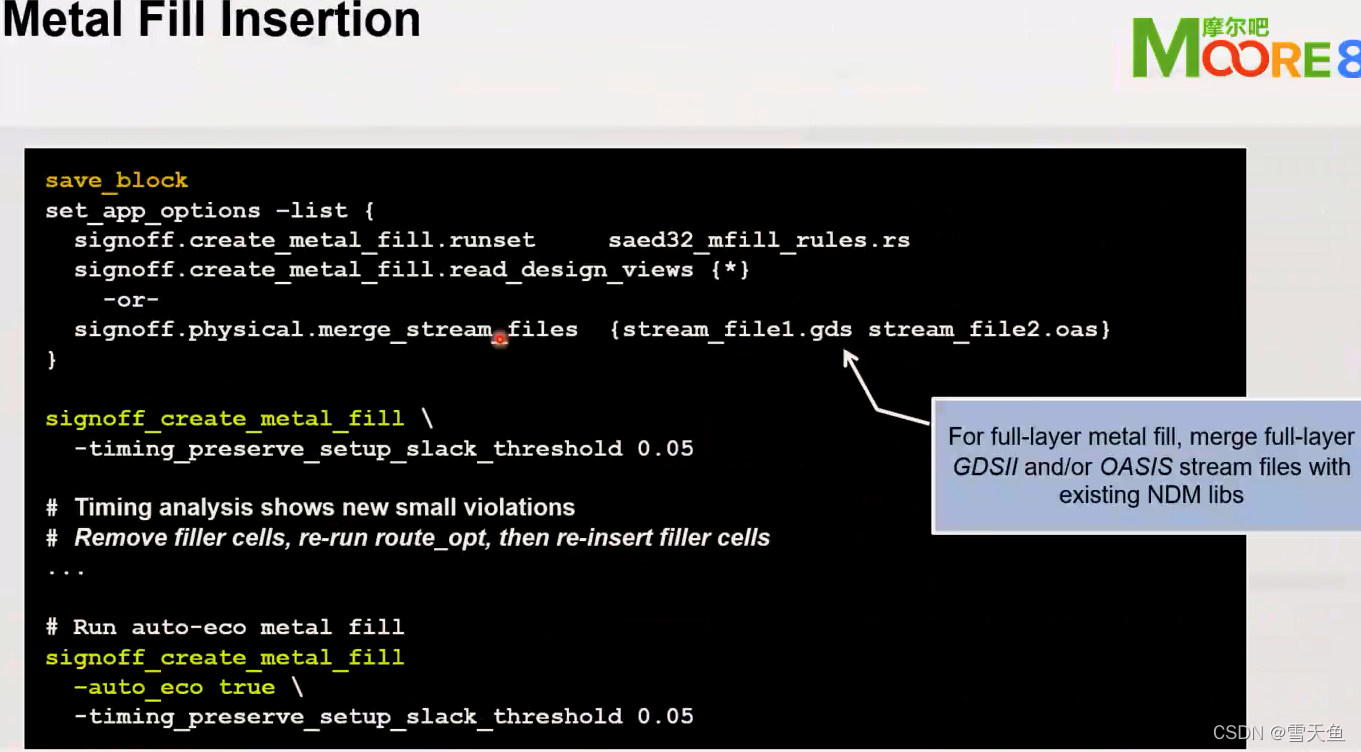

4.5 Signoff

五、相关学习资源

学不完学不完了,开冲开冲!!

8197

8197

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?