目录

2.1.7 在多通道自动模式下使用TX和RX缓冲旁路共享TXUSRCLK和RXUSRCLK

2.3 RX时钟纠正(RX Clock Correction)

1 内容简介

本章主要介绍GTH IP核接收端(Receiver)的RX缓冲旁路(RX Buffer Bypass),RX弹性缓冲(RX Elastic Buffer)和RX时钟纠正(RX Clock Correction)。

| Receiver 目录 | 描述 |

| 1.RX Buffer Bypass | RX缓冲旁路 |

| 2.RX Elastic Buffer | RX弹性缓冲 |

| 3.RX Clock Correction | RX时钟纠正 |

本章节涉及的功能块:

2 Receiver

2.1 RX缓冲旁路(RX Buffer Bypass)

2.1.1 功能描述

旁路 RX 弹性缓冲是 GTH 收发器的一项高级功能。RX 相位对齐电路用于调整 SIPO 并行时钟域和 RX XCLK 域之间的相位差,以实现从 SIPO 到PCS的可靠数据传输。它还通过调整 RXUSRCLK 来补偿温度和电压变化,从而执行 RX 延迟对齐。GTH 收发器可自动或手动执行 RX 相位和延迟的综合调整。

当 RX 恢复时钟用于 RXUSRCLK 和 RXUSRCLK2 时,可绕过 RX 弹性缓冲器以减少延迟。当绕过 RX 弹性缓冲器时,通过 RX 数据通路的延迟较低且确定,但无法进行时钟校正和通道绑定。

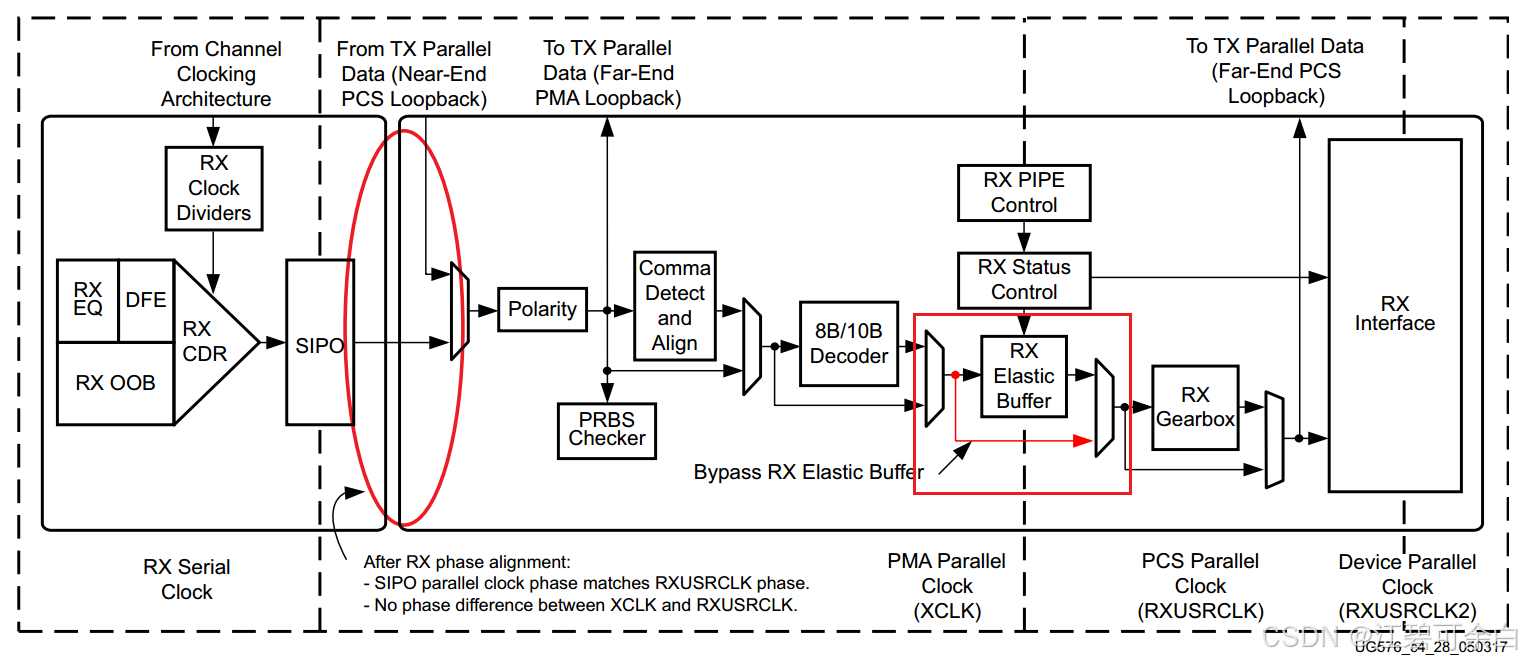

图2.1显示了 RX 相位对齐如何绕过 RX 弹性缓冲器。在 RX 相位对齐之前,SIPO 并行时钟域和 RX XCLK 域之间没有保证的相位关系。使用 RX 相位对齐时,RX XCLK 被配置为使用 RXUSRCLK。RX 相位对齐从 CDR(XCLK)中选择 RX 恢复时钟的相移版本,使 SIPO 并行时钟和 RX XCLK 之间没有明显的相位差。

使用 RX 缓冲器旁路时,RXSLIDE_MODE 不能设置为自动或 PMA。

图2.1

2.1.2 端口和属性

注:端口和属性过多,该部分不再展示,具体可参考UG576 目录Receiver - RX Buffer Bypass - Ports and Attributes的描述

2.1.3 RX缓冲旁路使用模型

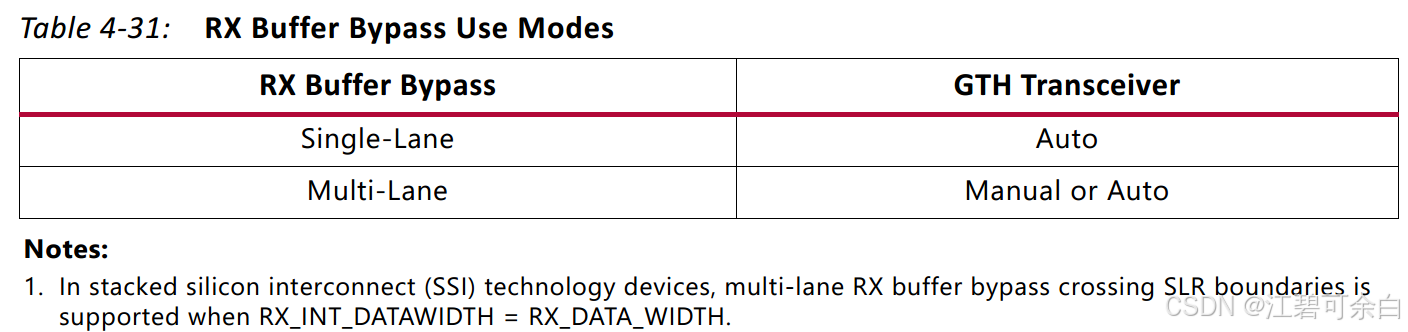

RX 相位对齐可在一个通道(单通道)或共享单个 RXOUTCLK 的一组通道(多通道)上执行。RX 缓冲器旁路支持单通道自动模式,以及手动和自动模式下的多通道应用(表2.1)。

表2.1

2.1.4 在多通道手动模式下使用RX缓冲旁路

注:该部分主要是使用步骤,可参考UG576 目录Receiver - RX Buffer Bypass - Using RX Buffer Bypass in Single-Lane Auto Mode

2.1.5 在多通道自动模式下使用RX缓冲旁路

注:该部分主要是使用步骤,可参考UG576 目录Receiver - RX Buffer Bypass - Using RX Buffer Bypass in Multi-Lane Manual Mode

2.1.6 在多通道自动模式下使用RX缓冲旁路

注:该部分主要是使用步骤,可参考UG576 目录Receiver - RX Buffer Bypass - Using RX Buffer Bypass in Multi-Lane Auto Mode

2.1.7 在多通道自动模式下使用TX和RX缓冲旁路共享TXUSRCLK和RXUSRCLK

对于 GTH 收发器,当多通道应用需要 TX 和 RX 缓冲器旁路时,可以共享 TXUSRCLK 和 RXUSRCLK。有关此用例的更多详情,请参阅 TX 缓冲器旁路(第 137 页)。

2.2 RX弹性缓冲(RX Elastic Buffer)

2.2.1 功能描述

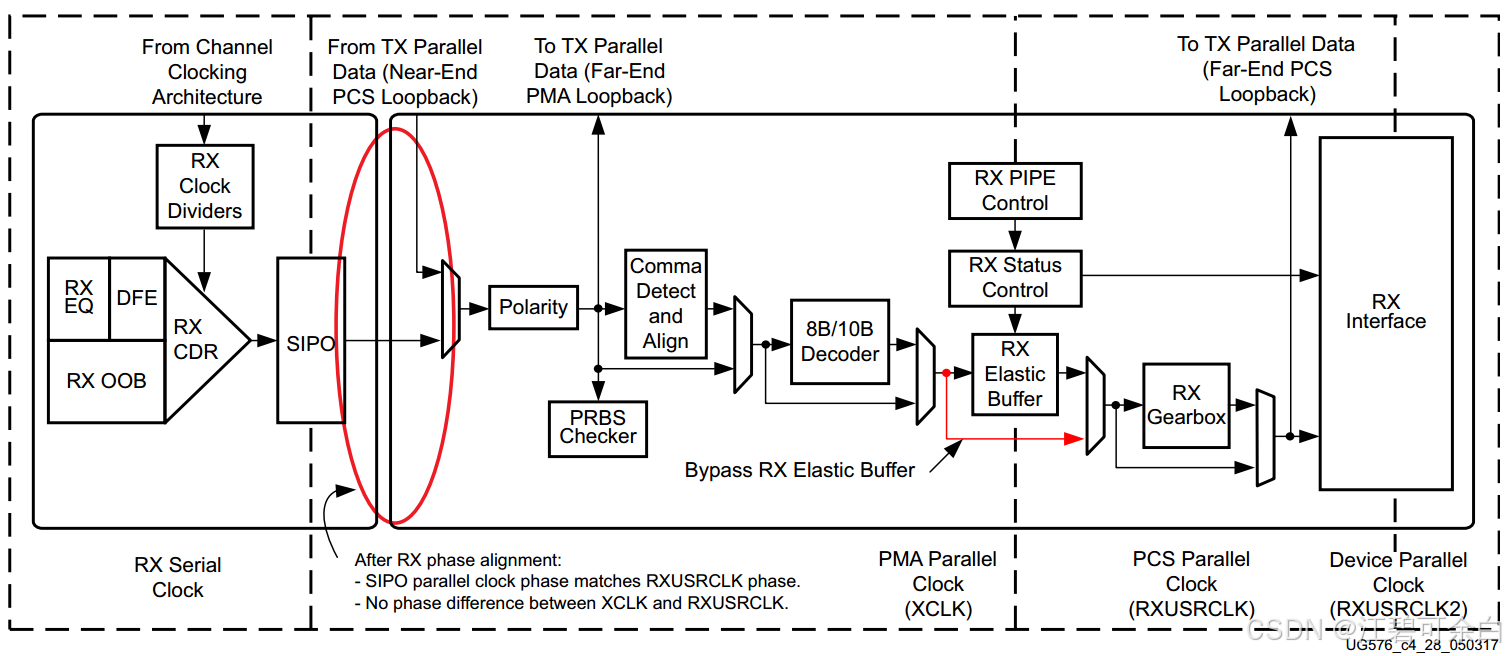

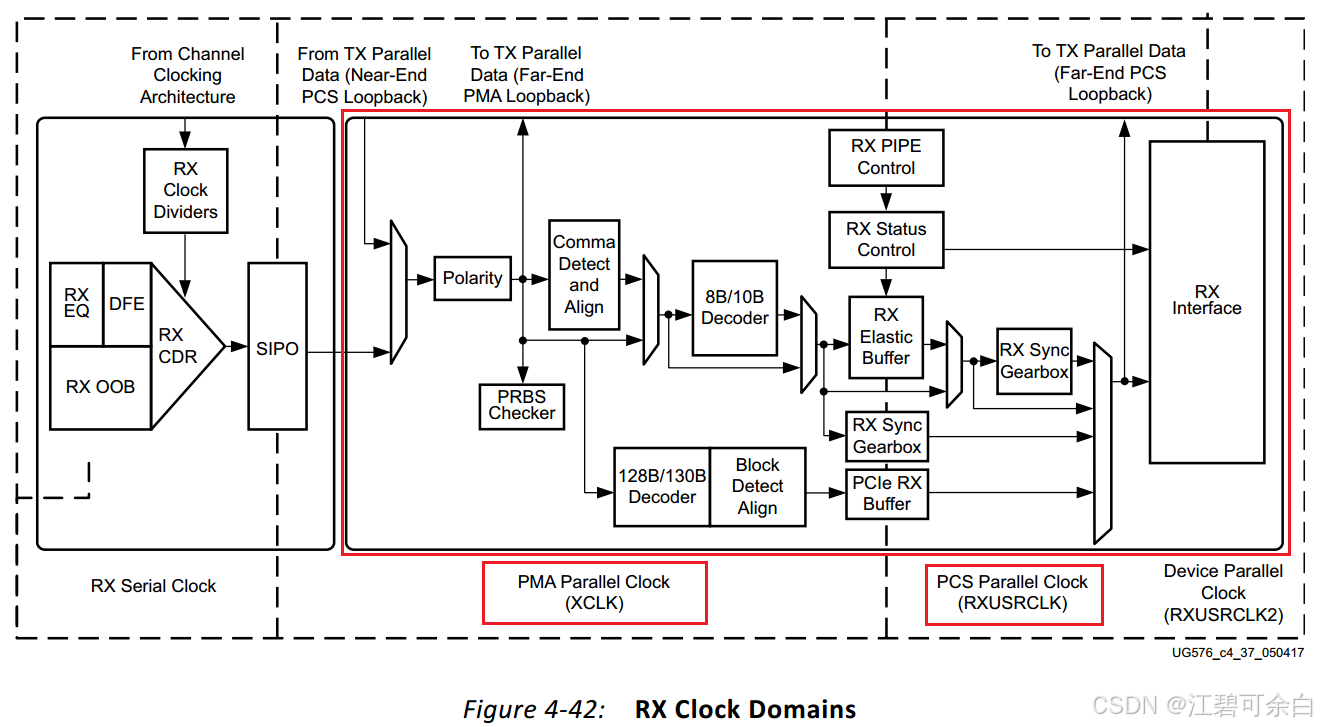

GTH 收发器 RX 数据通路有两个内部并行时钟域,用于 PCS: PMA 并行时钟域 (XCLK) 和 RXUSRCLK 域。要接收数据,PMA 并行速率必须足够接近 RXUSRCLK 速率,并且必须消除两个域之间的所有相位差。图2.2显示了两个并行时钟域: XCLK 和 RXUSRCLK。

图2.2

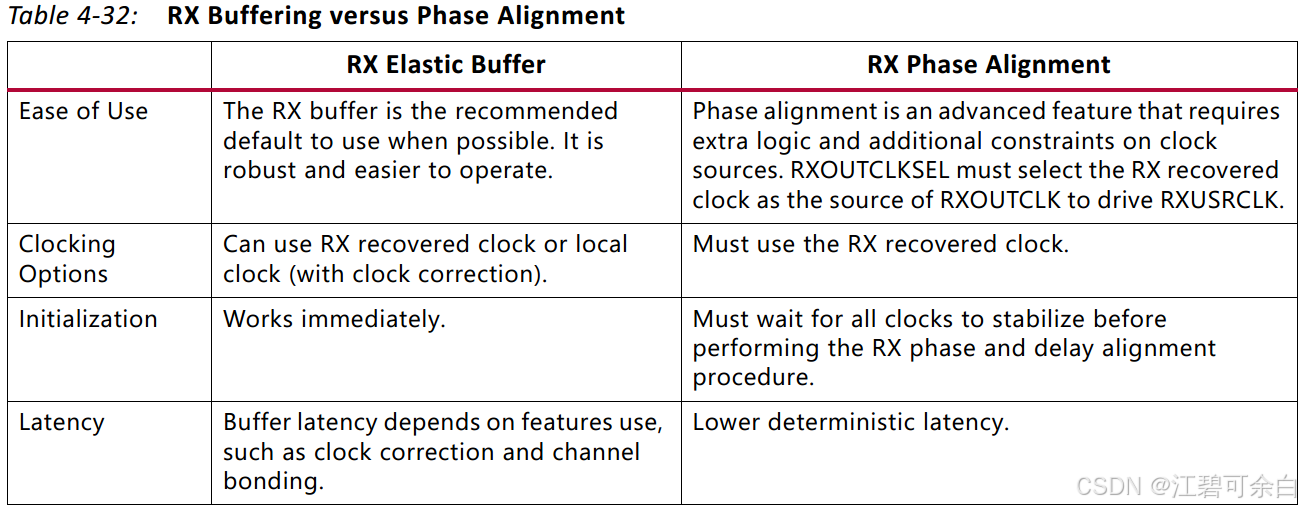

GTH 收发器包括一个 RX 弹性缓冲器,用于解决 XCLK 和 RXUSRCLK 域之间的差异。两个时钟域的相位也可以通过以下方式匹配:使用收发器的 RX 恢复时钟驱动 RXUSRCLK,并在旁路 RX 缓冲器时调整其相位以匹配 XCLK。所有 RX 数据通路都必须使用其中一种方法。表2.2列出了每种方法的成本和优势。

表2.2

上表中文释义:

| TX缓冲 | TX相位对齐 | |

| 易用性 | RX缓冲区是建议尽可能使用的默认缓冲区。它功能强大且易于操作。 | 相位对齐是一项高级功能,需要额外的逻辑和对时钟源的额外约束。 RXOUTCLKSEL 必须选择 RX 恢复时钟作为 RXOUTCLK 的时钟源,以驱动 RXUSRCLK。 |

| 时钟选项 | 可使用 RX 恢复时钟或本地时钟(带时钟校正)。 | 必须使用 RX 恢复时钟 |

| 初始化 | 立即生效 | 在执行 RX 相位和延迟校准程序之前,必须等待所有时钟稳定下来。 |

| 延时 | 缓冲区延迟取决于所使用的功能,如时钟校正和通道绑定。 | 确定性延迟较低。 |

| 时钟校正和通道绑定 | 需要用于时钟校正和通道绑定。 | 不在收发器内部执行。需要在互连逻辑中执行。 |

| TXUSRCLK抖动灵敏度 | 对 RXUSRCLK 抖动不敏感 | 对 RXUSRCLK 抖动敏感 |

2.2.2 端口和属性

注:端口和属性过多,该部分不再展示,具体可参考UG576 目录Receiver - RX Elastic Buffer - Ports and Attributes的描述

2.2.3 使用RX弹性缓冲

这些设置用于启用 RX 弹性缓冲器,以解决 XCLK 和 RXUSRCLK 域之间的相位差:

(1)RXBUF_EN = TRUE

(2)RX_XCLK_SEL = RXDES

如果出现 RX 弹性缓冲区溢出或下溢情况,RX 弹性缓冲区的内容将失效。出现上述情况时,请使用 GTRXRESET、RXPCSRESET、RXBUFRESET 对 RX 弹性缓冲区进行复位和重新初始化,或 GTH 收发器内部生成的 RX 弹性缓冲区复位(请参阅 RX 初始化和复位)。内部生成的 RX 弹性缓冲区复位可在通道绑定变化、逗号重新对齐、电气空闲或速率变化条件下发生。

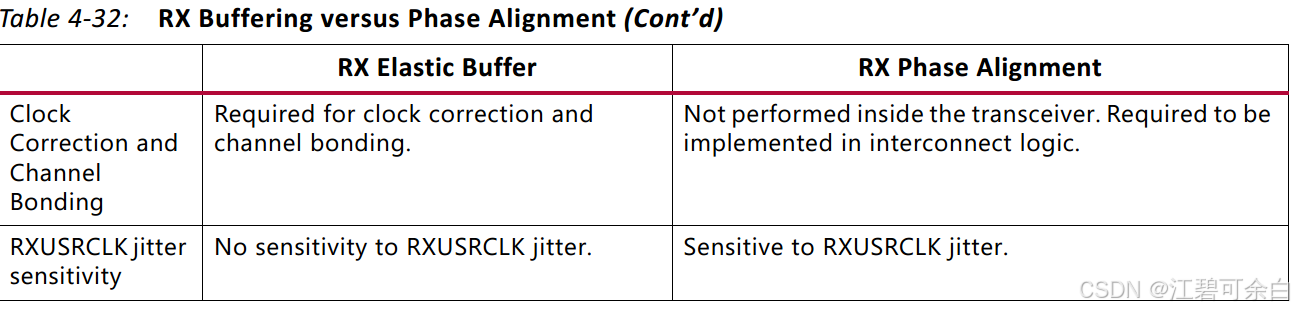

RX 弹性缓冲区还可用于时钟校正和通道绑定。时钟校正用于 XCLK 和 RXUSRCLK 频率不匹配的情况。表2.3列出了常见的时钟配置,并显示它们是否需要时钟校正。

表2.3

2.3 RX时钟纠正(RX Clock Correction)

2.3.1 功能描述

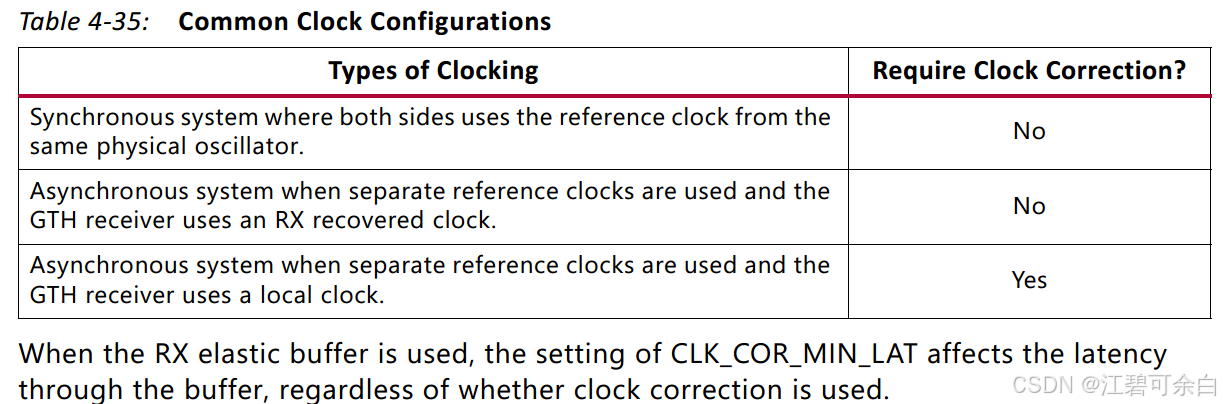

RX 弹性缓冲器的设计目的是在两个不同的时钟域 RXUSRCLK 和 XCLK(从 CDR 恢复的时钟)之间搭建桥梁。即使 RXUSRCLK 和 XCLK 以相同的时钟频率运行,也总会存在微小的频率差。由于 XCLK 和 RXUSRCLK 的频率并不完全相同,因此除非进行修正,否则差值会累积到一定程度,导致 RX 弹性缓冲器最终溢出或下溢。为了进行校正,每个 GTH 收发器 TX 都会定期发送一个或多个特殊字符,允许 GTH 收发器 RX 根据需要在 RX 弹性缓冲区中删除或复制这些特殊字符。当 RX 弹性缓冲区太满时删除字符,当 RX 弹性缓冲区太空时复制字符,接收器就能防止溢出或下溢。

2.3.2 端口和属性

注:端口和属性过多,该部分不再展示,具体可参考UG576 目录Receiver - RX Clock Correction - Ports and Attributes的描述

2.3.3 使用RX时钟校正

按照本节所述步骤使用接收机的时钟校正功能。

(1)使能时钟纠正

每个 GTH 收发器都包含一个时钟校正电路,该电路通过控制 RX 弹性缓冲器的指针来执行时钟校正。要使用时钟校正,必须将 RXBUF_EN 设为 “TRUE”,以打开 RX 弹性缓冲器,并将 CLK_CORRECT_USE 设为 “TRUE”,以打开时钟校正电路。

当 RX 弹性缓冲器延迟过高或过低,且时钟校正电路检测到匹配序列时,就会触发时钟校正。要使用时钟校正,必须配置时钟校正电路以设置这些项目:①RX 弹性缓冲区限制②时钟校正序列。

(2)设置 RX 弹性缓冲区限制

RX 弹性缓冲区的限制通过 CLK_COR_MIN_LAT(最小延迟)和 CLK_COR_MAX_LAT(最大延迟)来设置。当 RX 弹性缓冲区中的字节数低于 CLK_COR_MIN_LAT,时钟校正电路会从其匹配的第一个时钟校正序列中写入一个额外的 CLK_COR_SEQ_LEN 字节,以防止缓冲区下溢。同样,当 RX 弹性缓冲区中的字节数超过 CLK_COR_MAX_LAT 时,时钟校正电路会从其匹配的第一个时钟校正序列中删除 CLK_COR_SEQ_LEN 字节,从该序列的第一个字节开始。向导会根据应用要求为 CLK_COR_MIN_LAT 和 CLK_COR_MAX_LAT 选择最佳设置。必须遵循向导选择的值,以保持最佳性能,且不得覆盖该值。

(3)设置时钟纠正序列

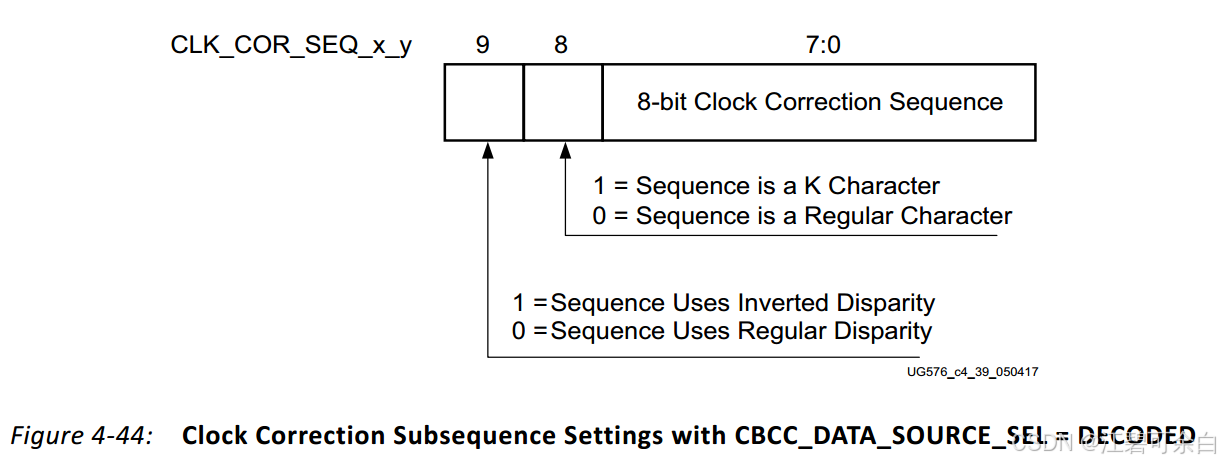

时钟校正序列通过 CLK_COR_SEQ_1_* 属性和 CLK_COR_SEQ_LEN 进行编程。每个 CLK_COR_SEQ_1_* 属性对应时钟校正序列 1 中的一个子序列。CLK_COR_SEQ_LEN 用于设置要匹配的子序列数。如果使用 40 位或 20 位内部数据通路,时钟校正电路将匹配每个子序列的所有 10 位。如果使用 16 位或 32 位内部数据通路,则只使用每个子序列最右边的 8 位。

将 CLK_COR_SEQ_2_USE 设置为 “true”,可激活第二个备用时钟校正序列。第一个和第二个序列共享长度设置,但使用不同的子序列值进行匹配。设置 CLK_COR_SEQ_2_* 属性可定义第二个序列的子序列值。

使用 8B/10B 解码(RX8B10BEN 为高电平)时,CBCC_DATA_SOURCE_SEL 设置为 DECODED,以搜索 8B/10B 解码器输出的序列匹配而非非解码数据。这样,电路就可以查找具有正或负差异的 8 位值,并将 K 字符与普通字符区分开来。图2.3显示了当 RX8B10BEN 为高电平且 CBCC_DATA_SOURCE_SEL 设为 DECODED 时如何设置时钟校正序列字节。

当 CBCC_DATA_SOURCE_SEL 设置为 ENCODED 时,序列必须与输入的原始数据完全匹配。当 RX_DISPERR_SEQ_MATCH 设置为 FALSE 时,CLK_COR_SEQ_x_y[9] 不用于匹配。

图2.3

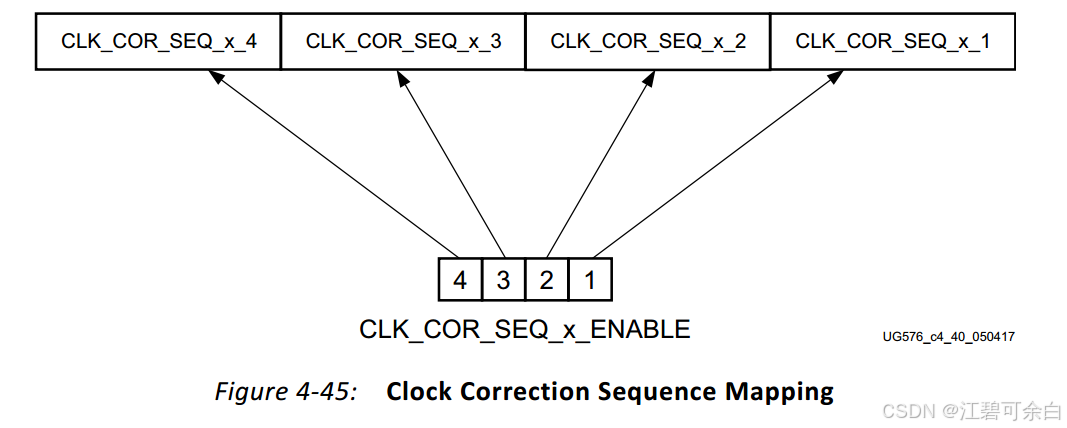

某些协议使用带有 “不关心 ”子序列的时钟校正序列。时钟校正电路可通过 CLK_COR_SEQ_1_ENABLE 和 CLK_COR_SEQ_2_ENABLE 编程来识别这些序列。当序列的使能位为低时,无论数值是多少,该字节都会被认为是匹配的。图2.4显示了时钟校正序列与时钟校正序列使能位之间的映射关系。

图2.4

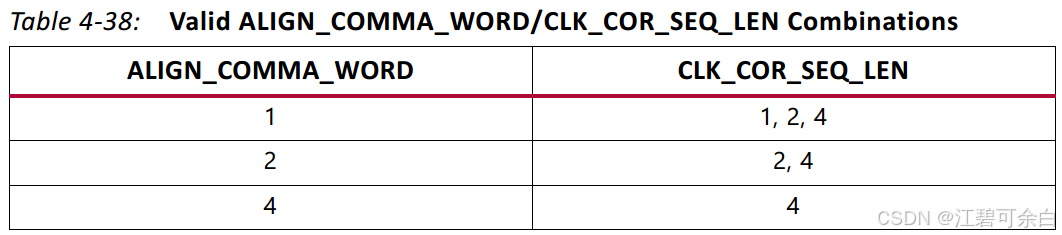

要通过弹性缓冲器保持逗号对齐,CLK_COR_SEQ_LEN 和 ALIGN_COMMA_WORD 的选择必须符合表2.4。

表2.4

(4)时钟纠正选项

CLK_COR_REPEAT_WAIT 用于控制时钟校正频率。该值设置为时钟校正事件之间所需的最小 RXUSRCLK 周期数。该属性设置为 0 时,允许随时进行时钟校正。某些协议允许随时进行时钟校正,但要求如果时钟校正电路删除序列,则至少有一个序列保留在数据流中。对于有此要求的协议,CLK_COR_KEEP_IDLE 设置为 TRUE。

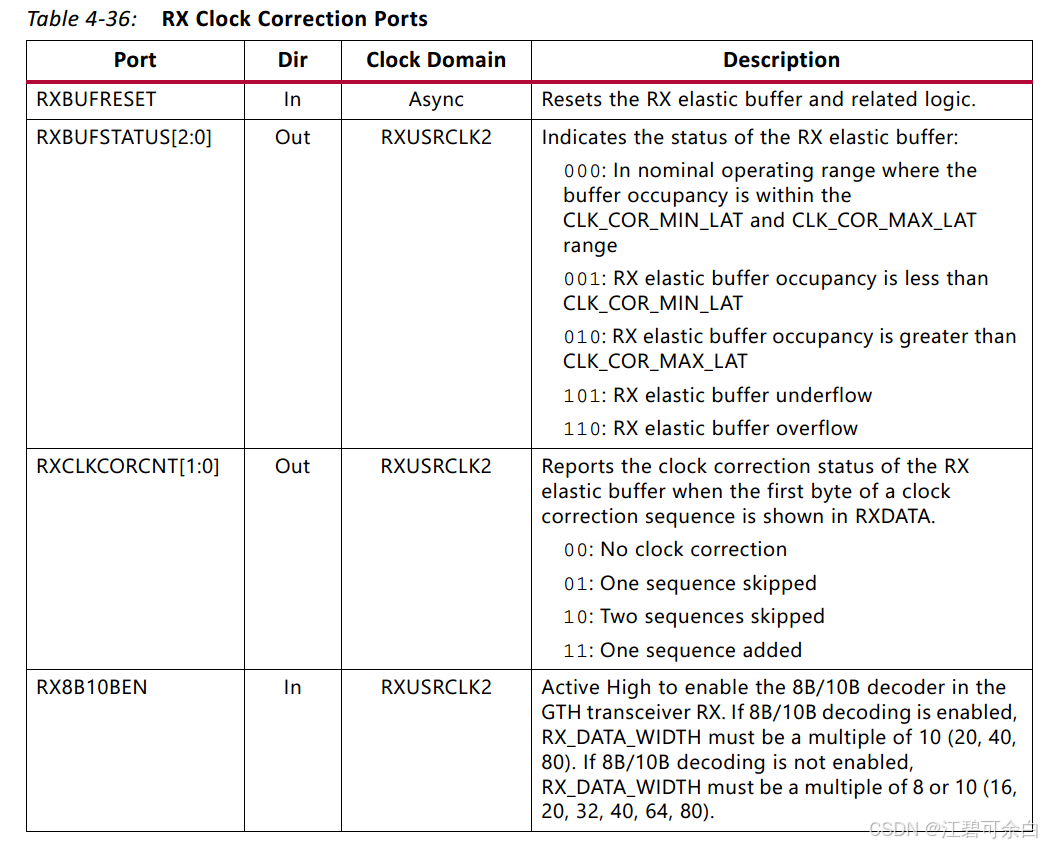

(5)监管时钟纠正

可以使用 RXCLKCORCNT 和 RXBUFSTATUS 端口监控时钟校正电路。 RXCLKCORCNT 项说明了如何解码 RXCLKCORCNT 的值以确定时钟校正电路的状态。 RXBUFSTATUS 项说明了如何解码 RXBUFSTATUS 的值,以确定 RX 弹性缓冲区的满载程度。如下表:

3 结束语

本章主要简要介绍了接收端RX的RX缓冲旁路(RX Buffer Bypass),RX弹性缓冲(RX Elastic Buffer)和RX时钟纠正(RX Clock Correction)。下一章预计在下周更新,内容为RX Channel Bonding,RX Synchronous Gearbox,RX Asynchronous Gearbox和RX Interface。

大家如果发现有问题的地方欢迎批评指证,畅所欲言地交流。如果觉得本期内容对您有用,希望获得您的点赞,收藏和关注,感谢各位。

注:过年人都懒了,没有更新。祝各位新年扶摇直上,万般喜乐,入得彀中矣。

6200

6200

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?