目录

1 内容简介

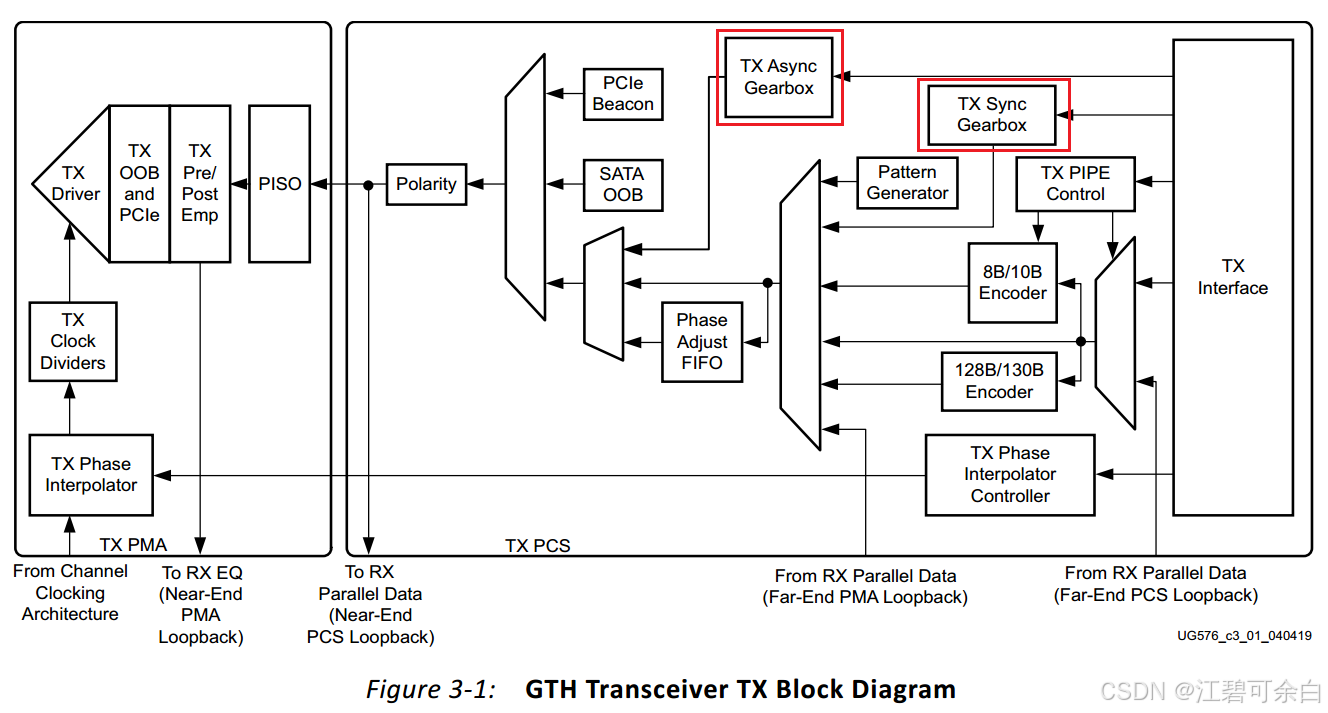

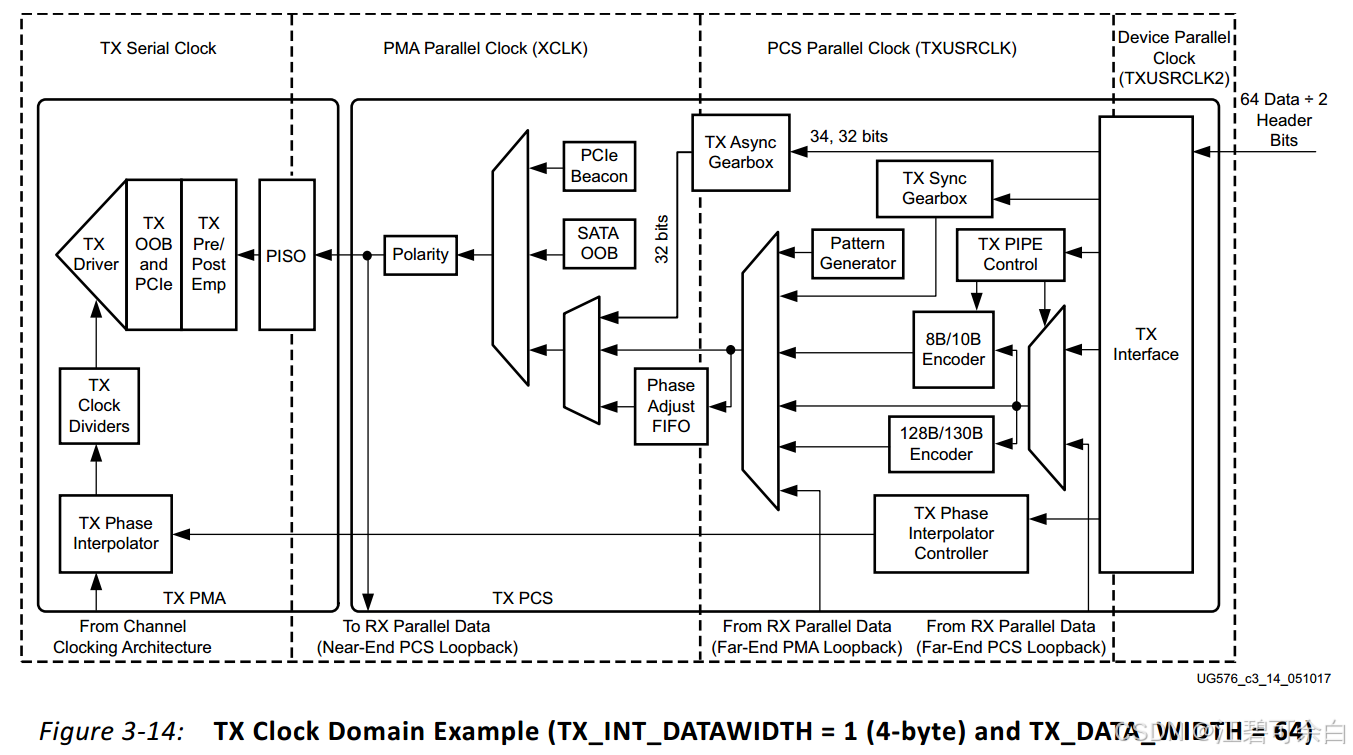

本章主要介绍GTH IP核发送端(Transmitter)的同步变速箱(TX Synchronous Gearbox)和异步变速箱(TX Asynchronous Gearbox)的功能和原理,变速箱顾名思义,数字逻辑中可以理解为一个黑盒子,输入频率和输入数据位宽经过黑盒后会发生改变,用于位宽调整和频率控制。

| Transmitter 目录 | 描述 |

| 4.TX Synchronous Gearbox | TX同步变速箱 |

| 5.TX Asynchronous Gearbox | TX异步变速箱 |

本章节涉及的功能块:

2 Transmitter

2.1 TX同步变速箱

2.1.1 功能描述

一些高速数据速率协议使用 64B/66B 编码来减少 8B/10B 编码的开销,同时保留编码方案的优势。TX 同步变速箱支持 64B/66B 和 64B/67B 包头和有效载荷组合。Interlaken 接口协议规范使用 64B/67B 编码方案。有关更多信息,请参阅 Interlaken 规范。

TX 同步变速箱支持 2 字节、4 字节和 8 字节接口。数据的加扰是在互连逻辑中完成的。除了正常的同步变速箱模式外,还支持 CAUI 接口模式。

2.1.2 端口和属性

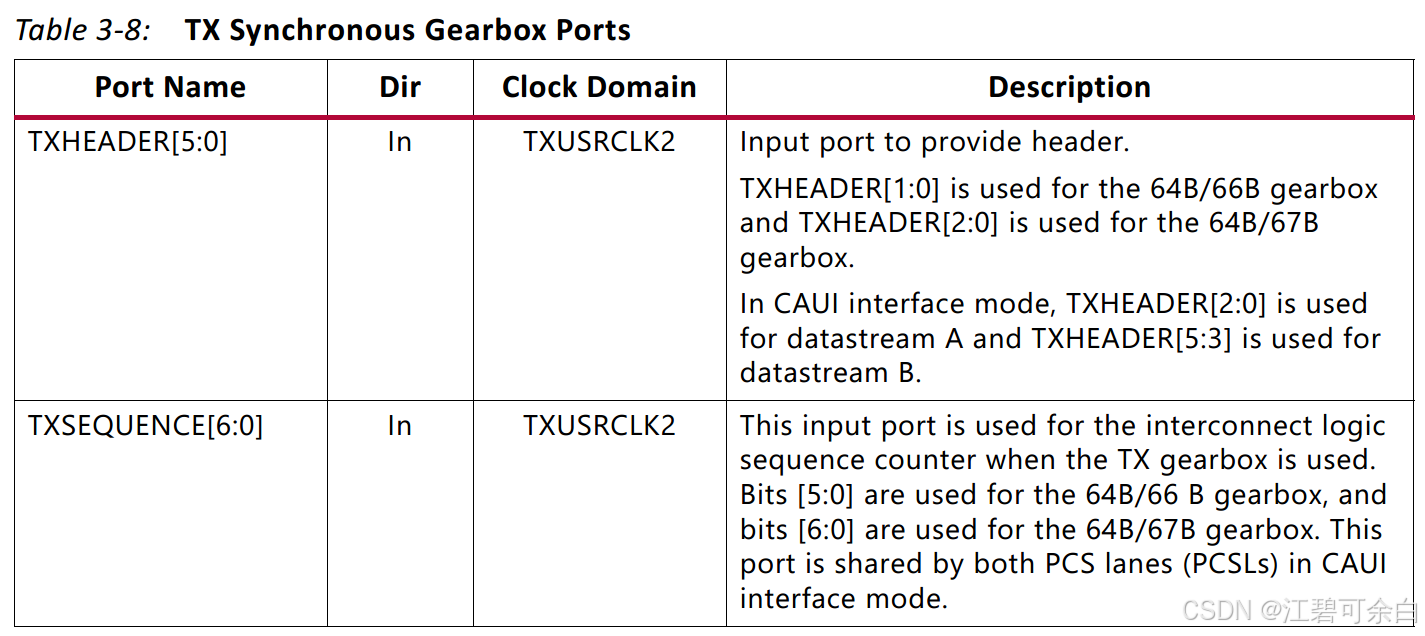

如图为TX同步变速箱端口:

2.1.3 使能TX同步变速箱

要启用 TX 同步变速箱,必须将 TXGEARBOX_EN 设置为 TRUE。

GEARBOX_MODE 属性的bit4 必须设置为 0。bit3 和 1 未使用,必须设置为 0。bit2决定是使用正常接口还是 CAUI 接口。bit0 决定是使用 64B/67B 变速箱还是 64B/66B 变速箱。GTH 收发器的 TX 变速箱和 RX 变速箱使用相同的模式。

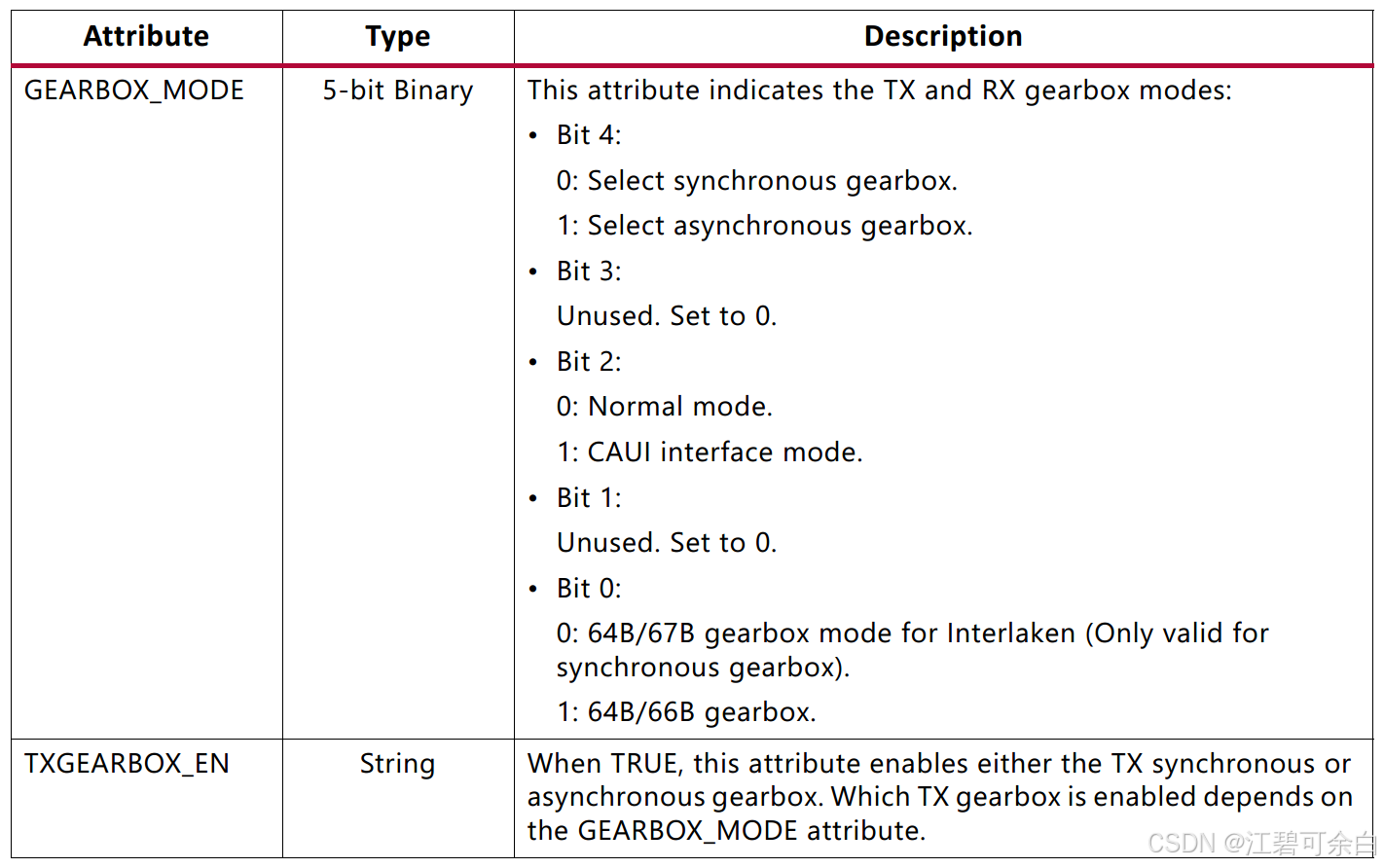

2.1.4 TX 同步变速箱的位和字节排序

如图2.1显示了在正常模式 (GEARBOX_MODE[2] = 1'b0) 下使用 4 字节逻辑接口 (TX_DATA_WIDTH = 32 (4 字节)、TX_INT_DATAWIDTH = 1 (4 字节)) 时,数据进入和退出 TX 变速箱的前四个周期的示例,用于 64B/66B 编码。输入由 2 位包头和 32 位数据组成,具体操作如下:

(1)第一个周期(Cycle0),包头(H1-H0)和 高30 位数据(D31-D2)退出 TX 变速箱

(2)第二个周期(Cycle1),来自前一个周期的 TXDATA 输入的剩余两个数据位(D1-D0)以及来自当前周期 TXDATA 输入的 30 个数据位(D32-D2)退出 TX 变速箱。

(3)第三个周期(Cycle2),TX 变速箱的输出包含来自第一个 66 bit块的两个剩余数据位(D1-D0)、第二个 66 bit块的包头(H1-H0)以及来自第二个 66 bit块的 28 个数据位(D31-D4)。

(4)第四个周期(Cycle3),来自前一个周期的 TXDATA 输入的剩余四个数据位(D3-D0)以及来自当前周期 TXDATA 输入的 28个数据位(D32-D4)退出 TX 变速箱。

图2.1

注:1. 根据 IEEE802.3ae 命名法,H1 对应于 TxB<0>,H0 对应于 TxB<1>,等等

2.1.5 使用TX同步变速箱

TX 同步变速箱需要使用必须在互连逻辑中实现的外部序列计数器。TX 变速箱支持 2 字节、4 字节和 8 字节的互连逻辑接口。

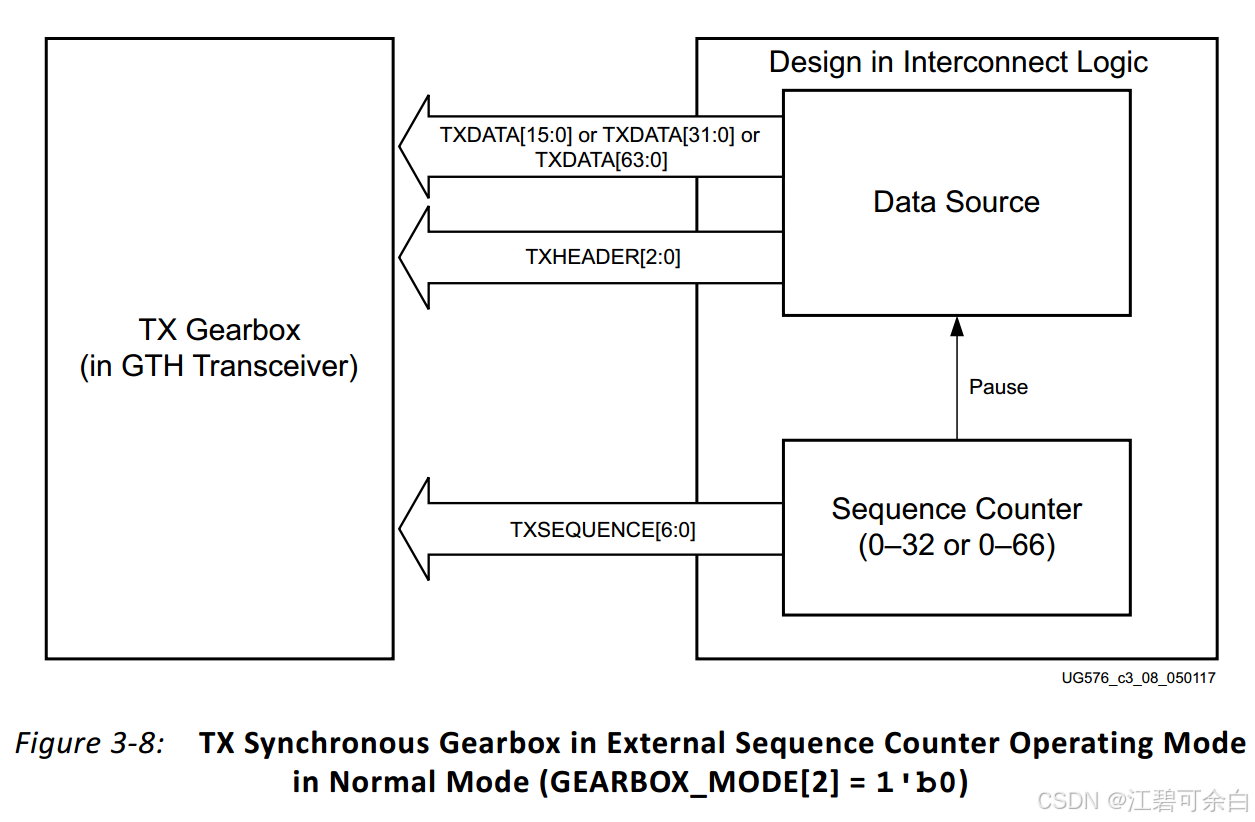

如图2.2所示,外部序列计数器操作模式在正常模式 (GEARBOX_MODE[2] = 1'b0) 下使用 TXSEQUENCE [6:0]、TXDATA[63:0] 和 TXHEADER[2:0] 输入。使用 CAUI 接口 (GEARBOX_MODE[2] = 1'b1) 时也会使用 TXHEADER[5:3]。互连逻辑中必须存在二进制计数器来驱动 TXSEQUENCE 端口。对于 64B/66B 编码,计数器从 0 递增到 32,并从 0 开始重复。对于 64B/67B 编码,计数器从 0 递增到 66,并从 0 开始重复。

使用 64B/66B 编码时,将 TXSQUENCE [6] 绑定到逻辑 0,并将未使用的 TXHEADER [2] 绑定到逻辑 0。

当使用 CAUI 接口并选择 64B/66B 编码(GEARBOX_MODE[2] = 1'b1,GEARBOX_MODE[0] = 1'b1)时,TXHEADER[5] 必须绑定到逻辑 0。

序列计数器增量范围({0 to 32},{0 to 66})对于 2 字节、4 字节和 8 字节接口是相同的。但是,当使用 TX_DATA_WIDTH 与 TX_INT_DATAWIDTH 相同的模式时(例如,4 字节互连逻辑接口(TX_DATA_WIDTH = 32)和 4 字节内部数据宽度(TX_INT_DATAWIDTH= 1)),计数器必须每两个 TXUSRCLK2 周期增加一次。

图2.2

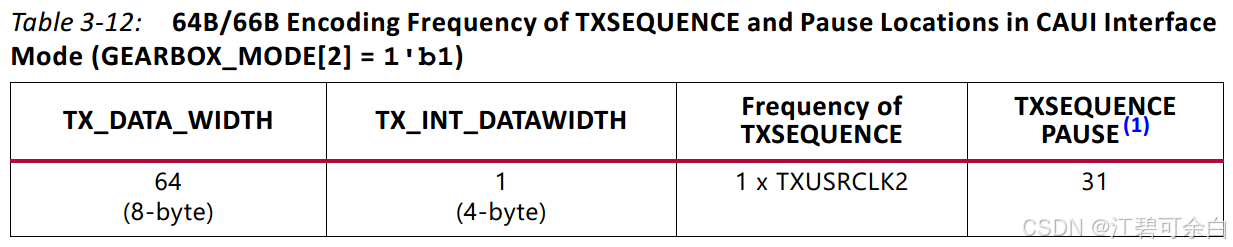

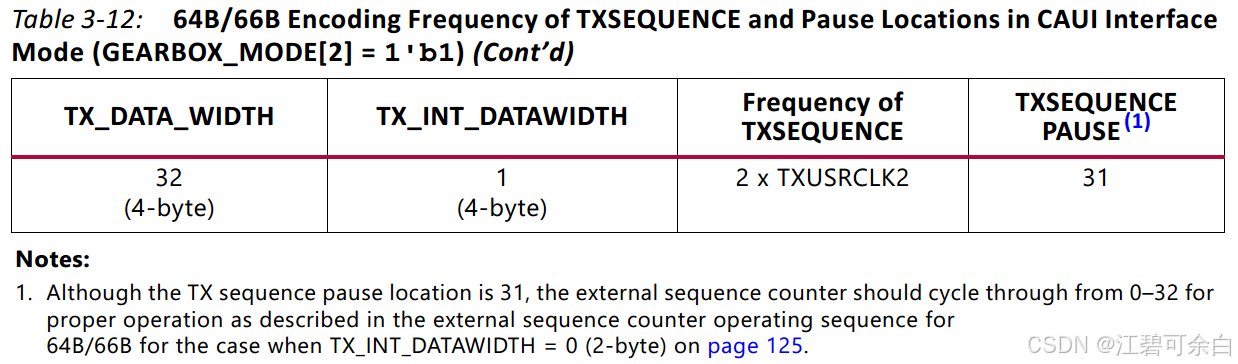

由于 64B/66B 和 64B/67B 编码方案和 TX 同步变速箱的性质,用户数据在各种序列计数器值期间被保持(暂停)。在具有相同 TX_DATA_WIDTH 和 TX_INT_DATAWIDTH 的模式下,数据暂停两个 TXUSRCLK2 周期,在 TX_DATA_WIDTH 是 TX_INT_DATAWIDTH 两倍的模式下,数据暂停一个 TXUSRCLK2 周期。有效数据传输在下一个 TXUSRCLK2 周期恢复。

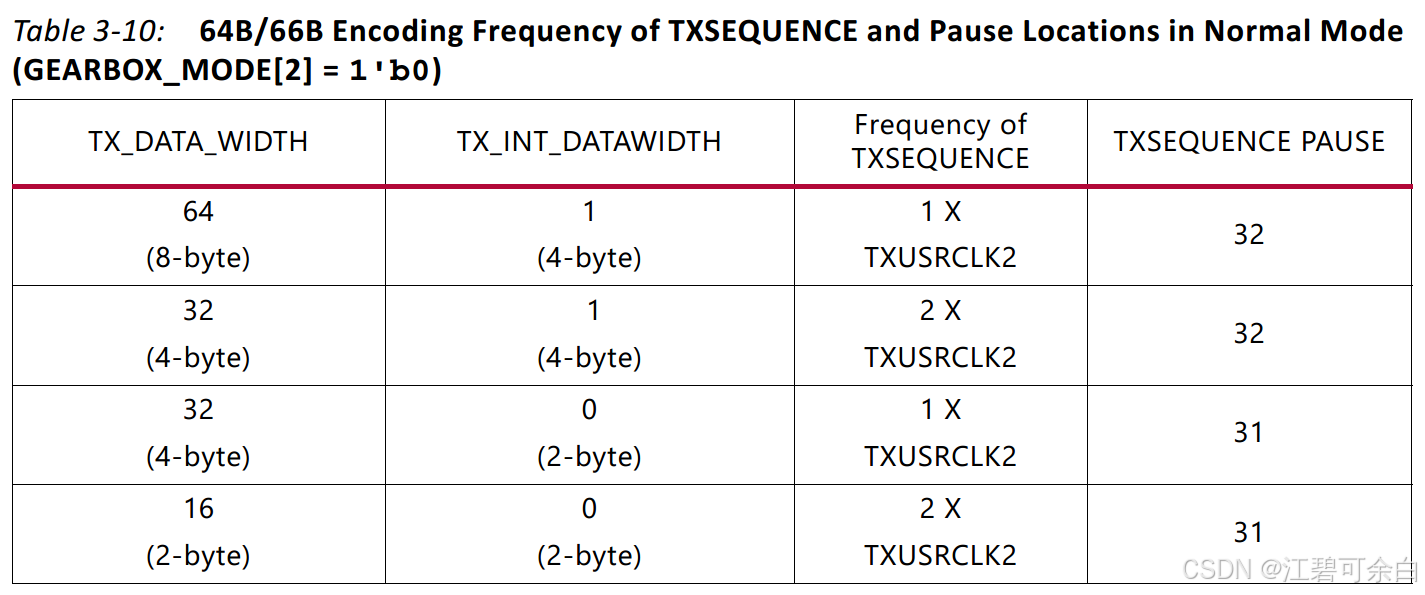

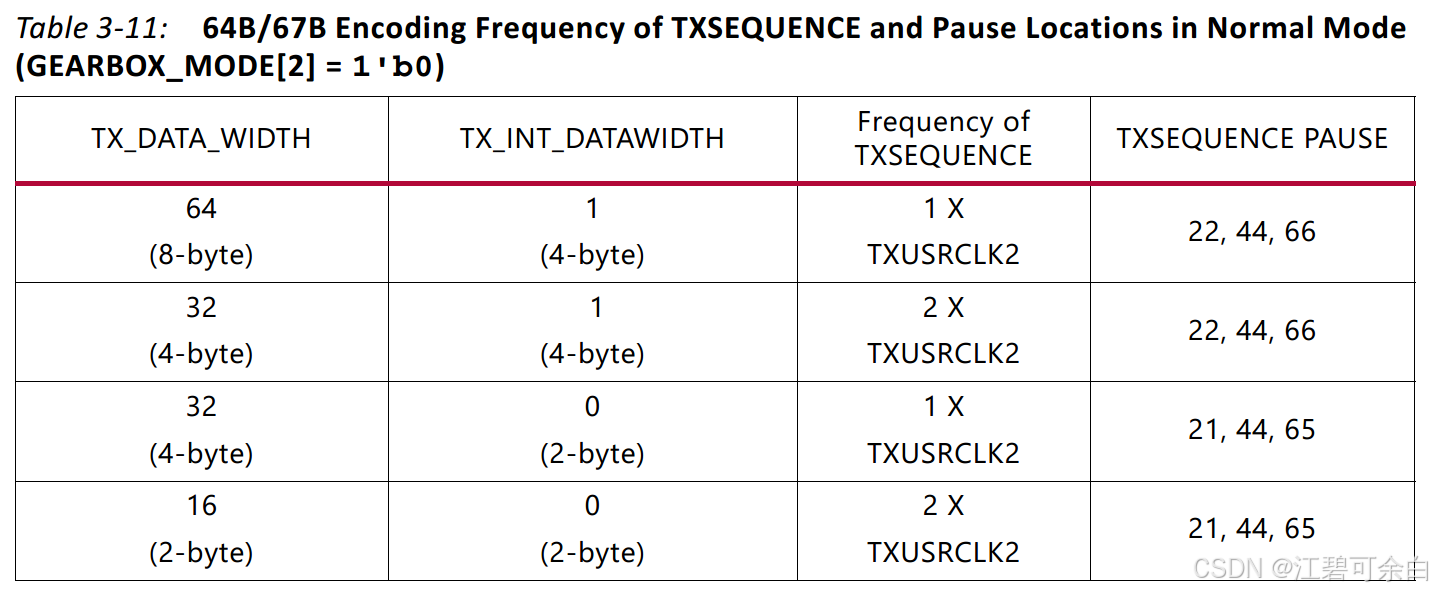

如表2.1和表2.2描述了各种模式的 TXSEQUENCE 暂停位置:

表2.1

表2.2

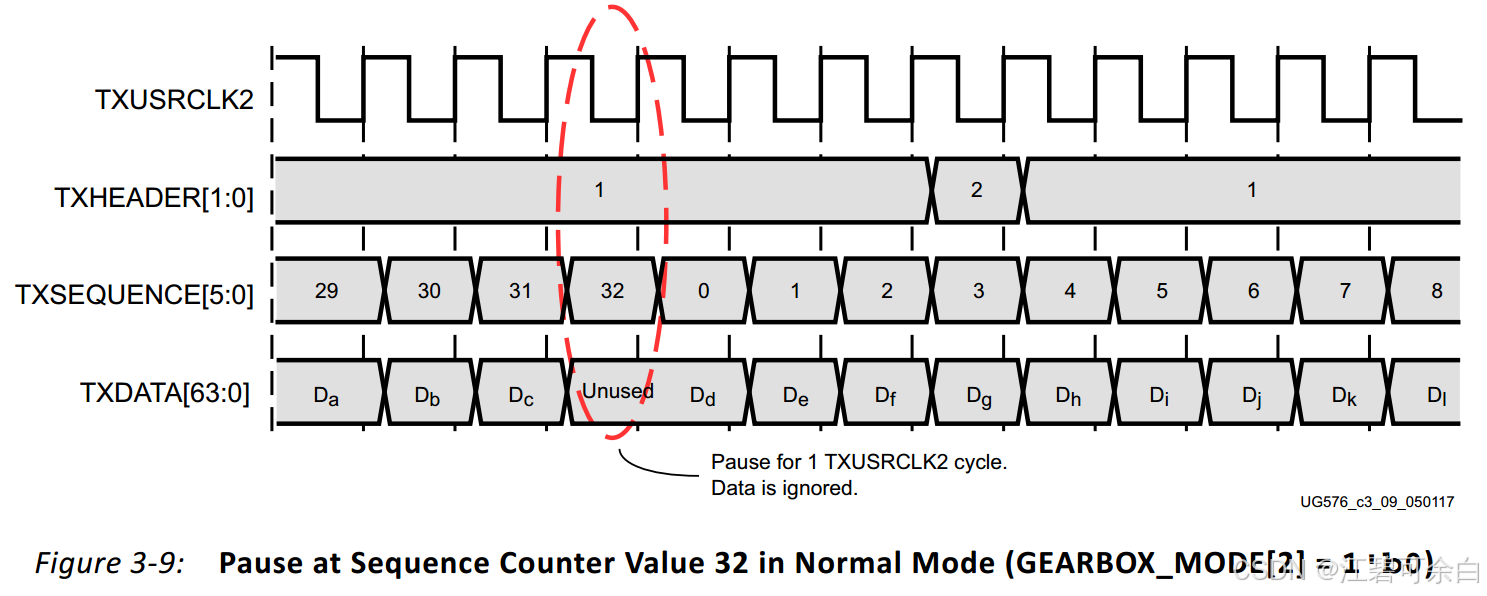

如图2.3显示了在正常模式 (GEARBOX_MODE[2] = 1'b0) 下以 64B/66B 编码,在外部序列计数器模式下使用 8 字节互连逻辑接口和 4 字节内部数据路径时,计数器值 32 处如何发生暂停。

图2.3

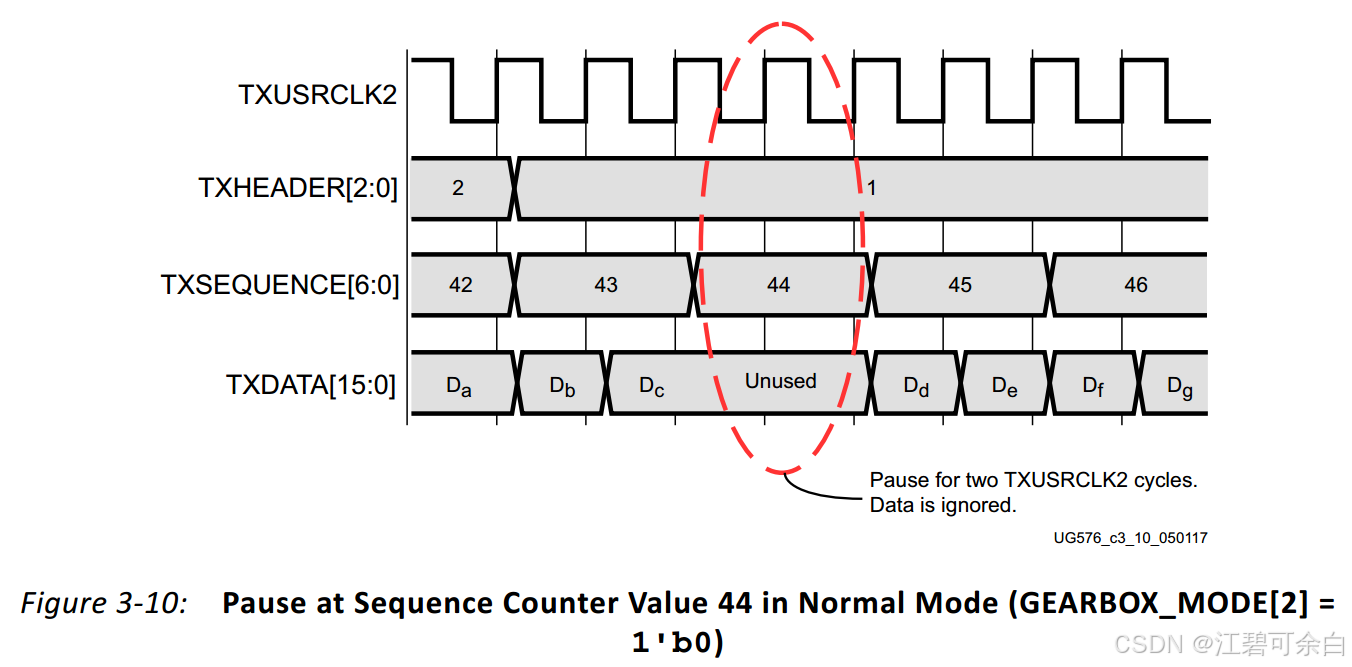

图2.4显示了在正常模式(GEARBOX_MODE[2] = 1'b0)下,在外部序列计数器模式下使用 2 字节互连逻辑接口与 2 字节内部数据通路并使用 64B/67B 编码时,计数器值 44 处如何发生暂停。

图2.4

情形1: 在正常模式(GEARBOX_MODE[2] = 1'b0)下使用 2 字节内部数据通路(TX_INT_DATAWIDTH = 0)为外部序列计数器模式传输 64/67 数据的顺序为:

1. 应用 GTTXRESET 并等待复位周期完成。

2. 复位期间,将 7'h00 应用于 TXSEQUENCE,将包头信息应用于 TXHEADER,将初始数据应用于 TXDATA。此状态可以无限期保持,直到数据传输就绪。

3. 计数为 0 时,将数据应用于 TXDATA,将包头信息应用于 TXHEADER。对于 2 字节接口 (TX_DATA_WIDTH = 16),在计数仍为 0 时将第2个 2个字节驱动到 TXDATA。

4. 数据驱动到 TXDATA 时,序列计数器递增到 1。

5. 应用 4 个字节的数据后,计数器递增到 2。将数据应用于 TXDATA,将包头信息应用于 TXHEADER。

6. 计数为 21 时,停止数据管道。

7. 计数为 22 时,将数据驱动到 TXDATA。

8. 计数为 44 时,停止数据管道。

9. 计数为 45 时,将数据驱动到 TXDATA。

10. 计数达到 65 时,停止数据管道。

11. 计数达到 66 时,在 TXDATA 上驱动数据。

情形2: 在正常模式(GEARBOX_MODE[2] = 1'b0)下使用 4字节内部数据通路(TX_INT_DATAWIDTH = 1)为外部序列计数器模式传输 64/67 数据的顺序为:

1. 应用 GTTXRESET 并等待复位周期完成。

2. 复位期间,将 7'h00 应用于 TXSEQUENCE,将包头信息应用于 TXHEADER,将初始数据应用于 TXDATA。此状态可以无限期保持,直到数据传输就绪。

3. 计数为 0 时,将数据应用于 TXDATA,将包头信息应用于 TXHEADER。对于4字节接口 (TX_DATA_WIDTH = 32),在计数仍为 0 时将第2个 4个字节驱动到 TXDATA。

4. 数据驱动到 TXDATA 时,序列计数器递增到 1。

5. 应用8个字节的数据后,计数器递增到 2。将数据应用于 TXDATA,将包头信息应用于 TXHEADER。

6. 计数为21时,停止数据管道。

7. 计数为22时,将数据驱动到 TXDATA。

8. 计数为44时,停止数据管道。

9. 计数为45时,将数据驱动到 TXDATA。

10. 计数达到66时,停止数据管道。

情形3:在正常模式(GEARBOX_MODE[2] = 1'b0)下使用 2 字节内部数据通路(TX_INT_DATAWIDTH = 0)的外部序列计数器模式传输 64/66 个数据的序列如下:

1. 应用 GTTXRESET 并等待复位周期完成。

2. 复位期间,将 6'h00 应用于 TXSEQUENCE,将适当的包头数据应用于 TXHEADER,将初始数据应用于 TXDATA。此状态可以无限期保持,直到数据传输就绪。

3. 计数为 0 时,将数据应用于 TXDATA,将包头信息应用于 TXHEADER。对于 2 字节接口 (TX_DATA_WIDTH = 16),在计数仍为 0 时将第2个 2 个字节驱动到 TXDATA。

4. 在 TXDATA 上驱动数据时,序列计数器递增到 1。

5. 应用 4 个字节的数据后,计数器递增到 2。在 TXDATA 上驱动数据,在 TXHEADER 上驱动报头信息。

6. 在计数为 31 时,停止数据管道。

7. 在计数为 32 时,在 TXDATA 上驱动数据。

情形4:在正常模式(GEARBOX_MODE[2] = 1'b0)下使用 4 字节内部数据通路(TX_INT_DATAWIDTH = 1)的外部序列计数器模式传输 64/66 个数据的序列如下:

1. 应用 GTTXRESET 并等待复位周期完成。

2. 复位期间,将 6'h00 应用于 TXSEQUENCE,将适当的包头数据应用于 TXHEADER,将初始数据应用于 TXDATA。此状态可以无限期保持,直到数据传输就绪。

3. 计数为 0 时,将数据应用于 TXDATA,将包头信息应用于 TXHEADER。对于 4 字节接口 (TX_DATA_WIDTH = 32),在计数仍为 0 时将第2个 4 个字节驱动到 TXDATA。

4. 在 TXDATA 上驱动数据时,序列计数器递增到 1。

5. 应用 8 个字节的数据后,计数器递增到 2。在 TXDATA 上驱动数据,在 TXHEADER 上驱动报头信息。

6. 在计数为 32 时,停止数据管道。

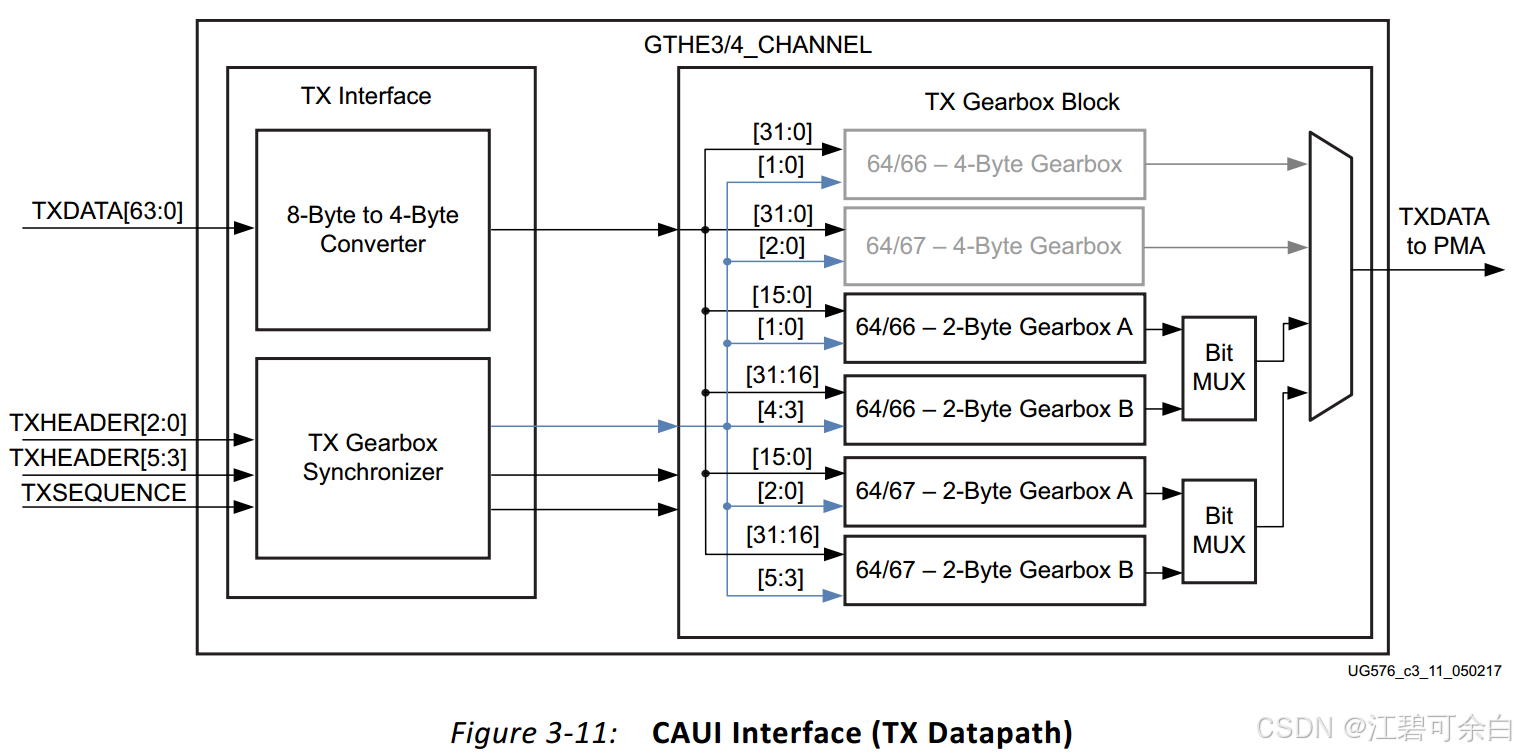

2.1.6 CAUI接口

CAUI(attachment unit interface)接口需要两个数据接口(数据流 A 和数据流 B)连接到收发器。支持 64B/66B 或 64B/67B 变速箱模式。通过将属性 GEARBOX_MODE[2] 设置为 1'b1 来启用 CAUI 接口模式。在 CAUI 接口模式下,数据宽度唯一允许的设置是 TX_INT_DATAWIDTH = 1(4 字节)和 TX_DATA_WIDTH = 64(8 字节)或 32(4 字节)。

TX 同步变速箱的顶层具有以下组件:

(1)两个 64B/66B 2 字节变速箱实例

(2)两个 64B/67B 2 字节变速箱实例

为了支持 CAUI 接口,GTH 收发器具有两个 2 字节变速箱实例。还添加了两个 Bit Mux 块实例(一个用于 64B/66B,一个用于 64B/67B 模式)来合并两个数据流。输入 TXHEADER[2:0] 用于数据流 A 的包头位。输入端口 TXHEADER[5:3] 用于数据流 B 的包头位。

图2.5

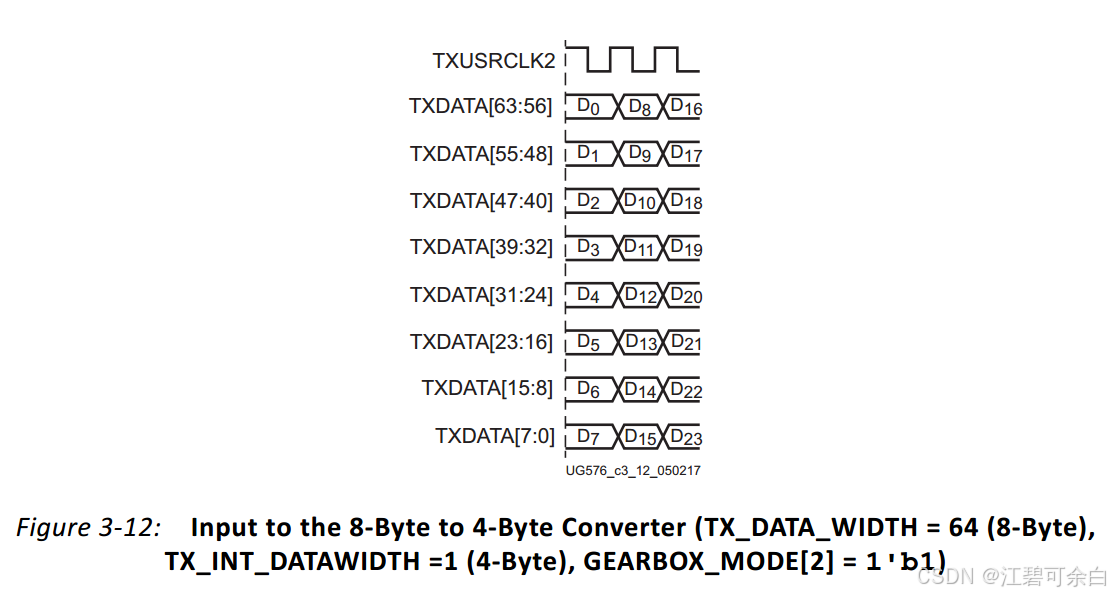

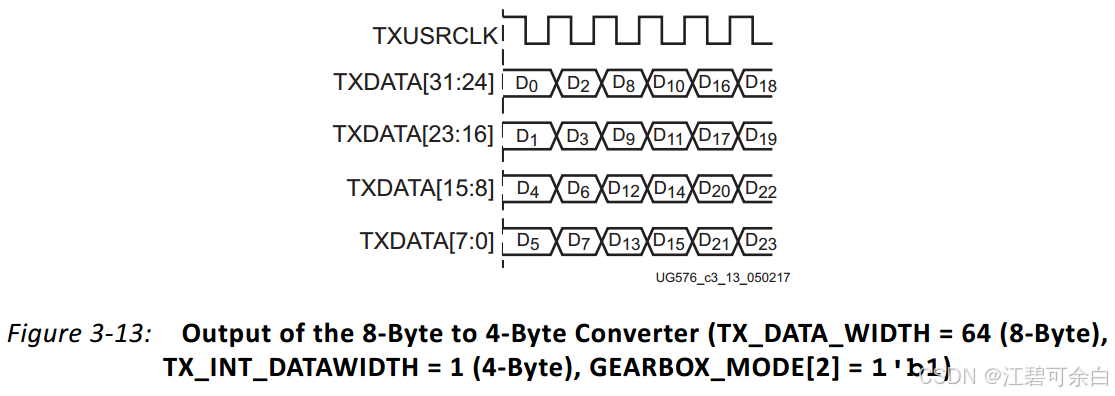

当处于 CAUI 接口模式且 PCSL 数据宽度为 32 位(TX_DATA_WIDTH = 64(8 字节))时,8 字节到 4 字节转换器将数据分成两个流,使得数据流 A 和数据流 B 到达相应的变速箱,如图2.6和图2.7所示:

图2.6

图2.7

Bit Mux 块将两个比特流(两个 16bit输入)交织,形成一个数据位宽为两倍的合并比特流。Bit Mux 功能如 IEEE Std 802.3ba-2010 条款 83.5.2 中所述。

尽管在 CAUI 接口模式下使用 TX_INT_DATAWIDTH = 1(4 字节),但使用两个 2 字节变速箱来实现该功能,如图2.5所示。这些 2 字节变速箱的功能与使用 TX 同步变速箱中针对 TX_INT_DATAWIDTH = 0(2 字节)的情况所述的功能相同。表2.3和表2.4描述了各种模式的 TXSEQUENCE 暂停位置。

表2.3

表2.4

2.1.7 总结归纳

(1)TX 同步变速箱可以支持 64B/66B 和 64B/67B 包头和有效载荷组合,本质上是为了完成不同频率和位宽的数据转换。

(2)序列计数器的计数范围:64B/66B 编码,计数器0-32;64B/67B 编码,计数器-0-66。计数范围由变速器前后的数据位宽来决定,范围的计算方法为:

范围:变速前后的位宽的最小公倍数 / 变速前的位宽

示例:64/66B的最小公倍数为32*33*2 = 2112,则范围为2112 / 64 = 33

64/67B的最小公倍数为64*67 = 4288,则范围为4288 / 64 = 67

以上其实也是不同位宽转换的时候转换周期的计算方法

(3)Unused即数据每传输一段时间,需要停止传输,其实是为了前后的带宽匹配

2.2 TX异步变速箱

2.2.1 功能描述

一些高速数据速率协议使用 64B/66B 编码来减少 8B/10B 编码的开销,同时保留编码方案的优势。TX 异步变速箱支持 64B/66B 包头和有效载荷组合。TX 异步变速箱不支持 64B/67B。

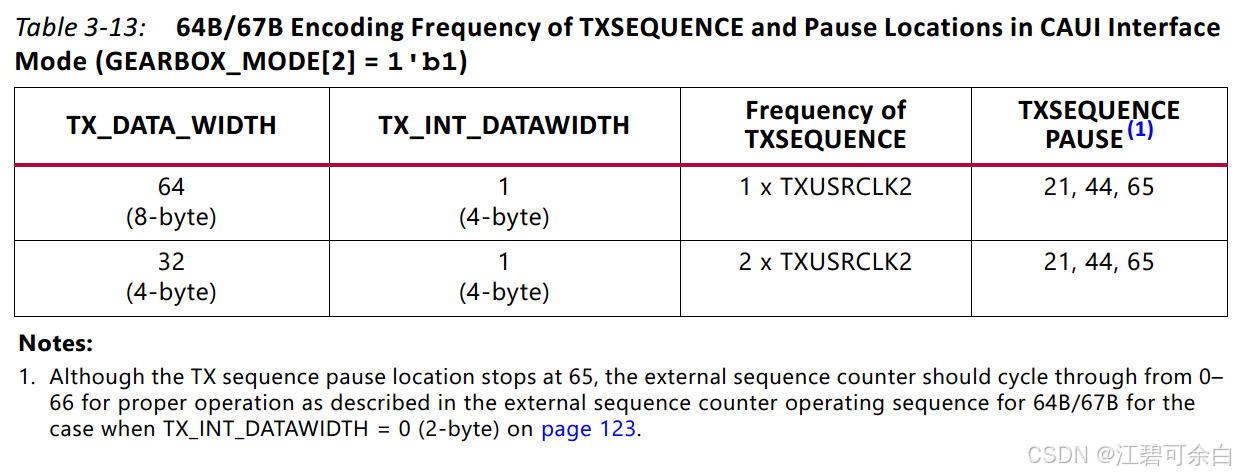

TX 异步变速箱支持 4 字节和 8 字节 TX 数据接口来连接逻辑,并且需要使用 4 字节内部数据路径。数据的加扰在互连逻辑中完成。除了正常的异步变速箱模式外,还支持 CAUI 接口模式。仅在使用 8 字节 TX 数据接口来连接逻辑时才支持 CAUI 接口。表2.5显示了异步变速箱的有效数据宽度组合。

虽然 TX 同步变速箱要求各种序列计数器值期间暂停数据传输,但 TX 异步变速箱允许在每个 TXUSRCLK2 周期连续应用数据。使用 TX 异步变速箱时不支持 TX 缓冲区旁路,因为它桥接了两个具有不同频率和相位的时钟域。TX 异步变速箱也与 TX 缓冲区并行。图2.8显示了 TX 异步变速箱的位置。TX 异步变速箱在每个 TX XCLK 周期始终输出 32 位数据。每个 TXUSRCLK 周期交替有 34 位(2 位标头和 32 位有效载荷)和 32 位(32 位有效载荷)数据进入 TX 异步变速箱。

图2.8

在正常模式下,通过 TX 异步变速箱的数据路径延迟在内部测量,报告的延迟可以通过 DRP 读取只读寄存器来访问。TX 异步变速箱与 TX 可编程分频器一起使用。必须将 TXOUTCLKSEL 设置为 3'b101,并且必须选择适当的分频值来为 TXUSRCLK 和 TXUSRCLK2 创建所需的时钟频率。

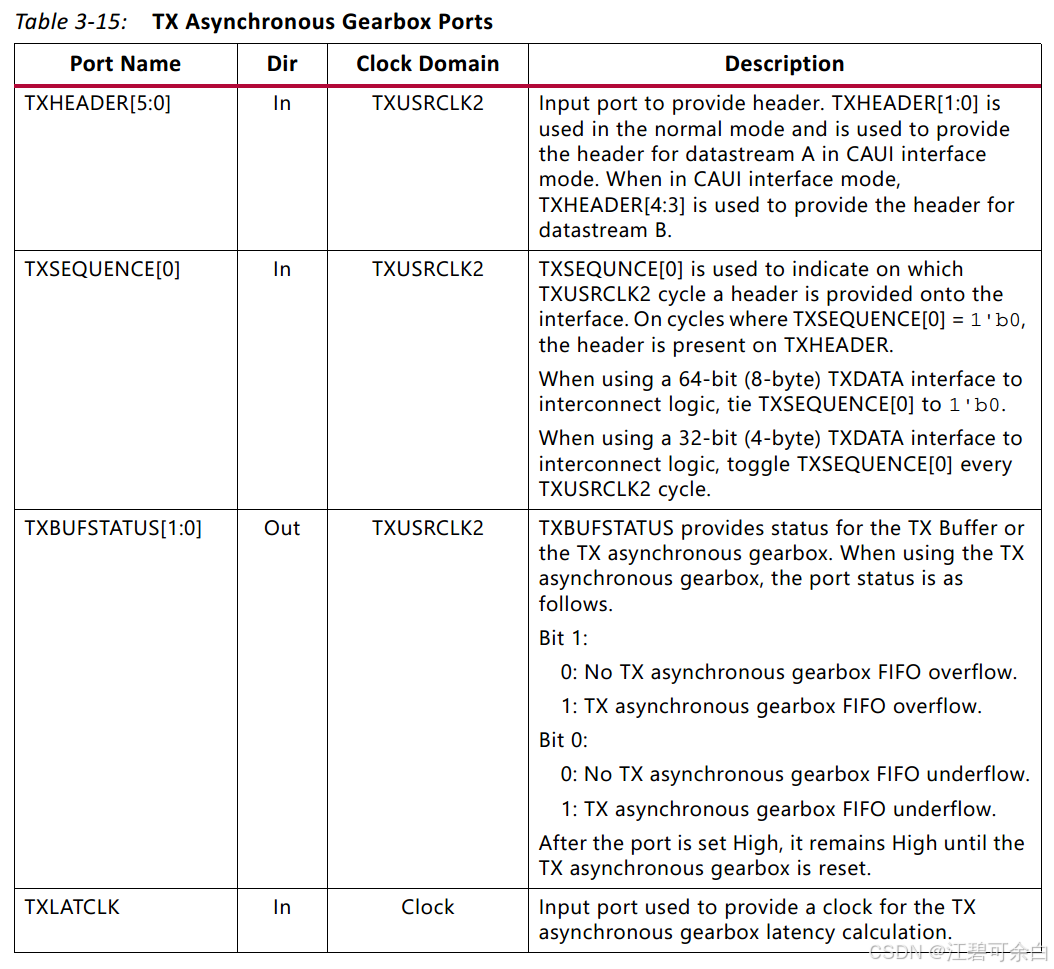

2.2.2 端口和属性

2.2.3 使能TX异步变速箱

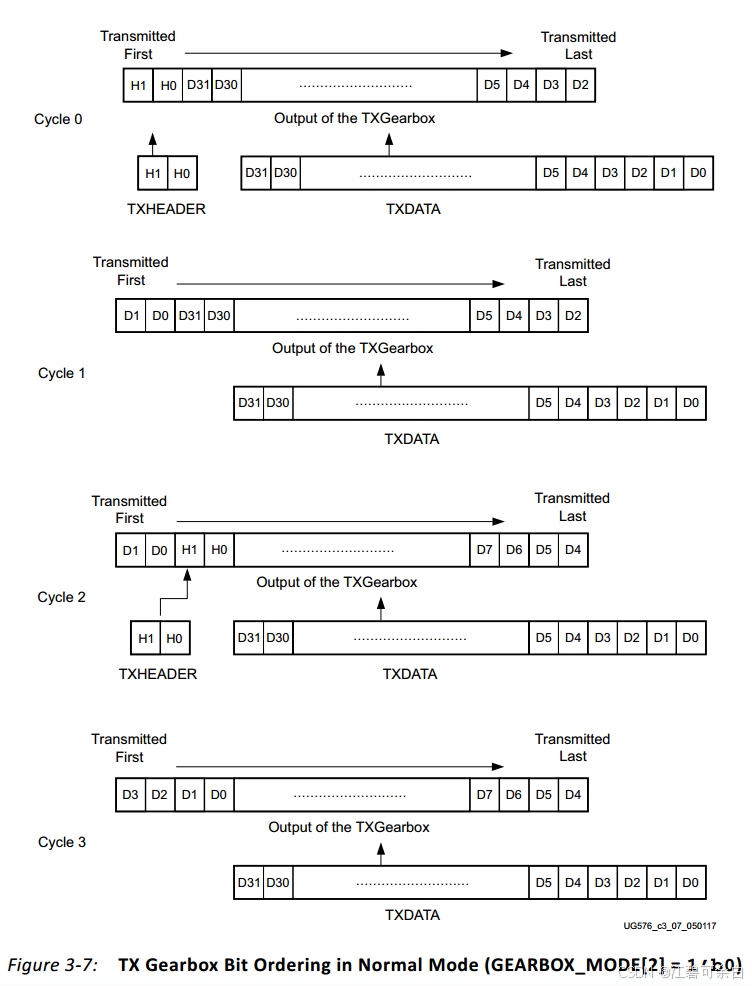

要启用 TX 异步变速箱,必须将 TXGEARBOX_EN 设置为 TRUE。

必须将 GEARBOX_MODE[4] 设置为 1'b1 以选择异步变速箱。

GEARBOX_MODE[1] 和 GEARBOX_MODE[3] 未使用,必须设置为 1'b0。

GEARBOX_MODE[2] 确定是否使用正常接口或 CAUI 接口。由于 TX 异步变速箱仅支持 64B/66B,因此必须将 GEARBOX_MODE[0] 设置为 1'b1。

2.2.4 TX 异步变速箱的位和字节排序

TX 异步变速箱使用与 TX 同步变速箱相同的位排序。

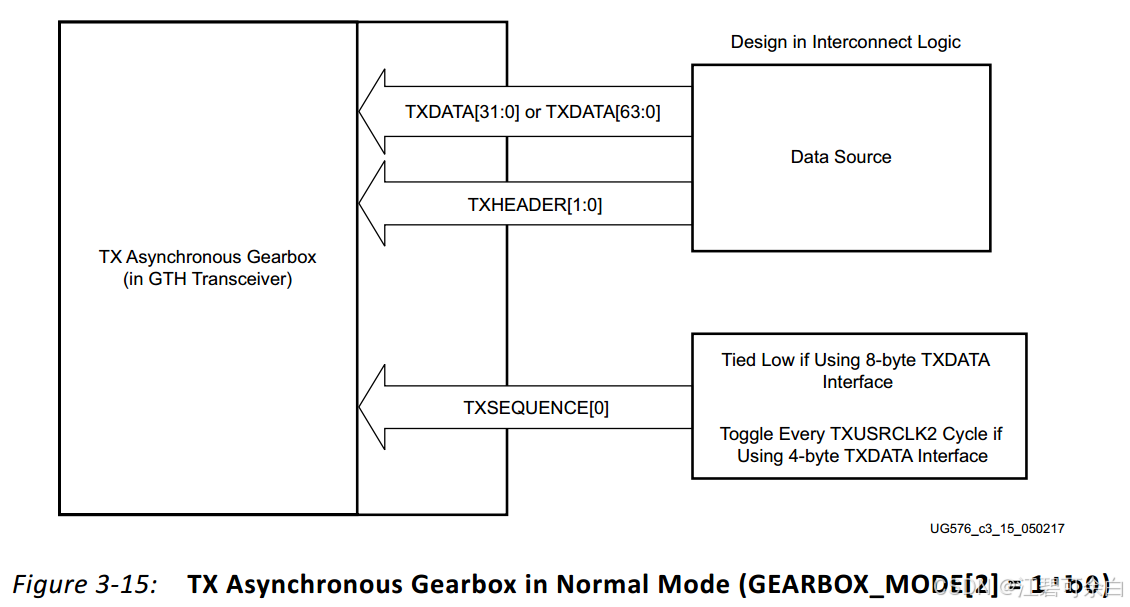

2.2.5 使用TX异步变速箱

如图2.9所示,TX 异步变速箱在正常模式(GEARBOX_MODE[2] = 1'b0)下使用 TXSEQUENCE[0]、TXDATA[63:0] 和 TXHEADER[1:0] 输入。

图2.9

使用 8 字节 TXDATA 接口 (TX_DATA_WIDTH = 64) 时,每个 TXUSRCLK2 周期将 2 位包头和 64 位有效载荷放置到 TXHEADER 和 TXDATA 上。使用 64 位 (8 字节) TXDATA 接口时,TXSEQUENCE[0] 处于低电平,因为每个 TXUSRCLK2 周期都会提供 2 位包头。

使用 4 字节 TXDATA 接口 (TX_DATA_WIDTH = 32) 时,每隔一个周期将 2 位包头放置到 TXHEADER[1:0] 上,并且每个 TXUSRCLK2 将 64 位有效载荷的一半放置在 TXDATA[31:0] 上。在使用 TXHEADER[1:0] 的相同 TXUSRCLK2 周期上,TXSEQUENCE[0] 必须处于低电平。

2.2.6 读数据路径延迟

通过 TX 异步变速箱 FIFO 的数据路径延迟是使用 TXLATCLK 进行统计计算的,TXLATCLK 与 TX_XCLK 异步。TX_SAMPLE_PERIOD 确定进行延迟计算的平均TXLATCLK 周期数。TXGBOX_FIFO_LATENCY 中的测量延迟值每个采样周期更新一次,该采样周期在 TX_SAMPLE_PERIOD 中定义。CAUI 模式下不支持延迟测量。

这些设置用于读取延迟:

(1)在正常模式下启用 TX 异步变速箱。

(2)设置 TX_SAMPLE_PERIOD:更高的平均周期可提供更准确的延迟值。

(3)读取 TXGBOX_FIFO_LATENCY:该值以 1/8 UI 为单位。

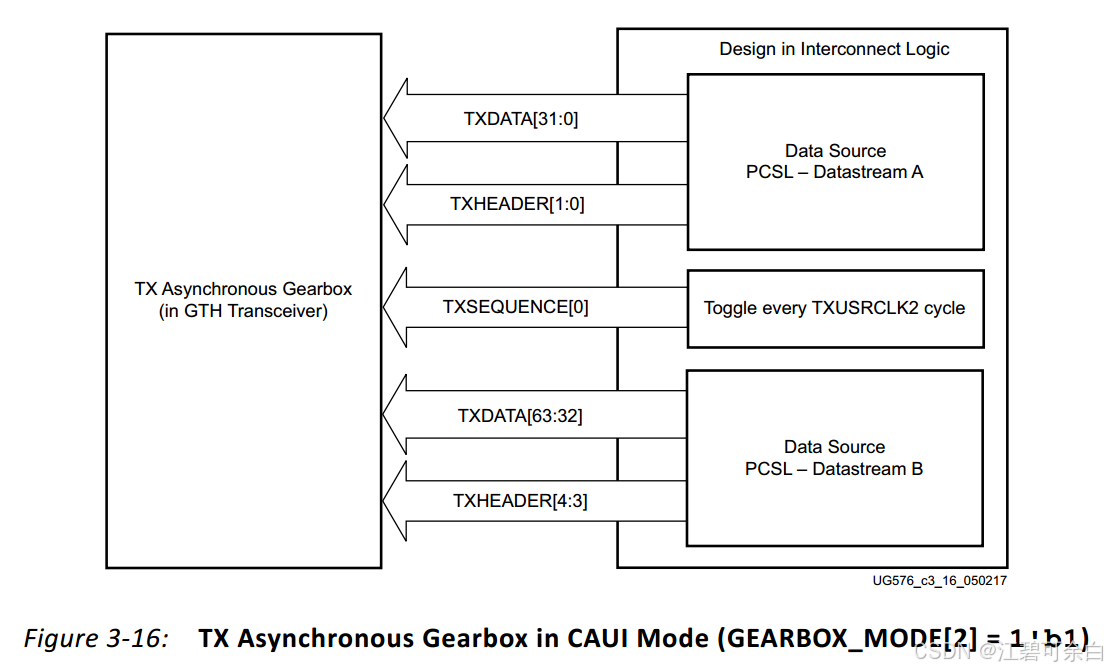

2.2.7 CAUI接口

CAUI 接口需要两个数据接口(数据流 A 和数据流 B)连接到收发器。通过将 GEARBOX_MODE[2] 设置为 1'b1,可以启用 CAUI 接口模式。在 CAUI 接口模式下,如果选择了 TX 异步变速箱,则数据宽度唯一允许的设置是 TX_INT_DATAWIDTH = 1(4 字节)和 TX_DATA_WIDTH = 64(8 字节)。

如图2.10所示,在 CAUI 模式(GEARBOX_MODE[2] = 1'b1)下,TX 异步变速箱使用 TXSEQUENCE[0]、TXDATA[63:0] 和 TXHEADER[4:0] 输入。当 TX_DATA_WIDTH = 32(4 字节)时,每个数据流的 CAUI 接口用法与正常模式下所述相同。

图2.10

3 遗留代办

关于TX同步变速箱和异步变速箱的内容学习完后,其实有两个疑惑不解的地方:

(1)同步和异步变速箱的应用场景分别是什么,那种情况下需要使用异步而不是使用同步?

(2)CAUI接口的用途是什么?为什么需要CAUI接口,相比普通接口的优势在哪里?

手册中对于以上部分并没有提及,暂时也没有用到该部分的地方,只能留待后续有机会问X家的FAE了,或者读者有知道的也欢迎指导(●'◡'●)

4 结束语

本章主要简要介绍了发送端TX同步和异步变速箱,下一期预计会在下周天更新,更新内容为GT的TX Buffer和TX Buffer Bypass。

大家如果发现有问题的地方欢迎批评指证,畅所欲言地交流。如果觉得本期内容对您有用,希望获得您的点赞,收藏和关注,感谢各位。

这周不确定是否有时间更新MIPI接口的专栏,暂定会使用Xilinx的IP完成MIPI协议的解码,手撸会放在使用Xilinx IP完成数据接收后,先熟悉一下Xilinx家的MIPI解码框架,然后再自己搭解码部分。

2714

2714

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?