一、时序约束是什么

时序约束:用来描述设计人员对时序的要求,比如时钟频率,输入输出的延时等。

比如,对时钟频率的约束最简单的理解就是,设计者需要告诉EDA工具设计中所使用的时钟频率是多少;然后工具才能按照所要求的时钟频率去优化布局布线,使设计能够在要求的时钟频率下正常工作。

二、为什么需要做时序约束

通俗的说就是因为代码写出来的时候,各功能块资源、寄存器资源、布线资源等资源是随机分布的,而布线不同路径导致延时时间不同,这样的话就会导致竞争关系的出现,因此,为了避免这种情况,必须对FPGA资源布局布线进行时序约束以满足设计要求。

三、如何创建时序约束

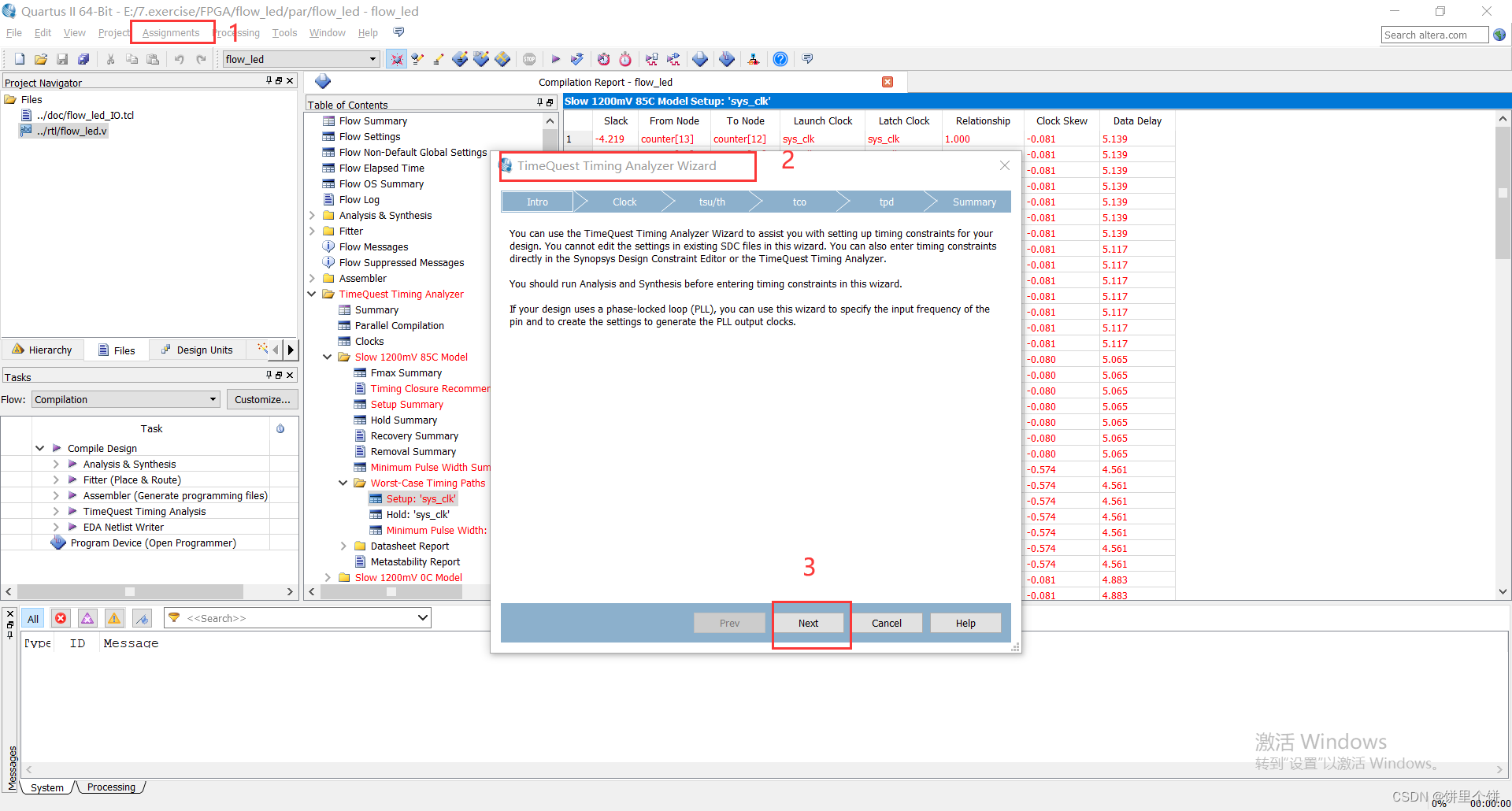

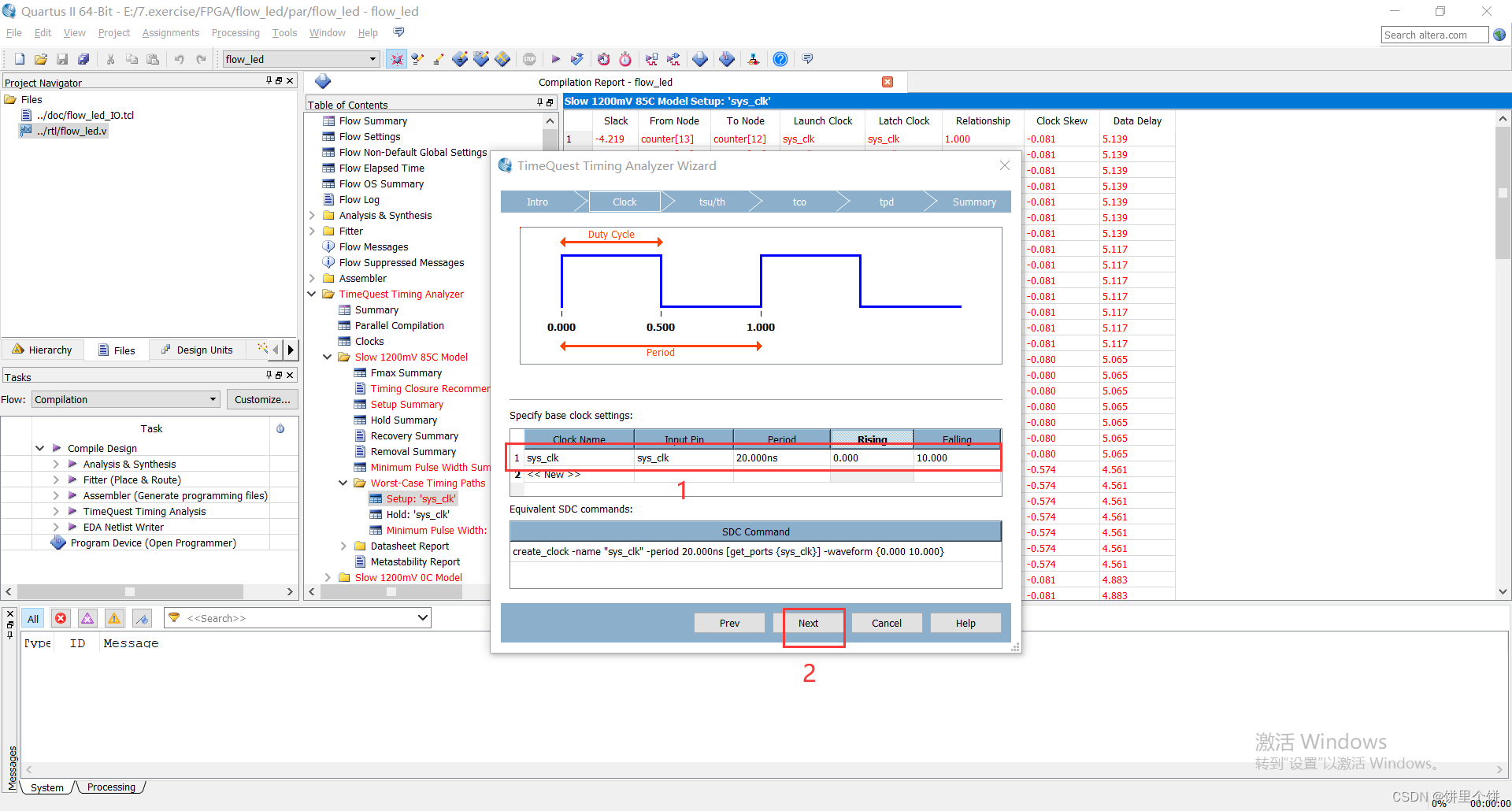

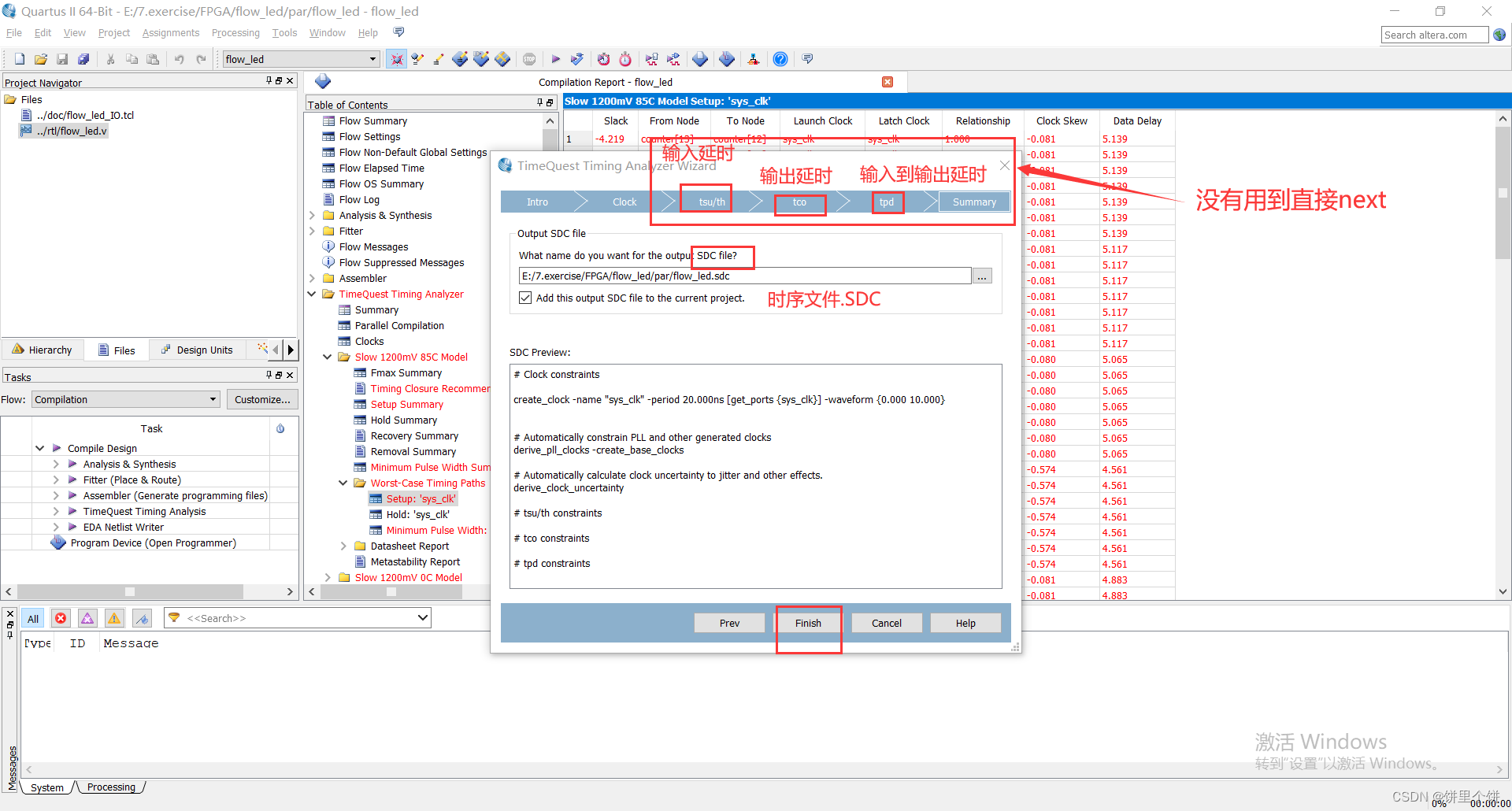

1.时序向导

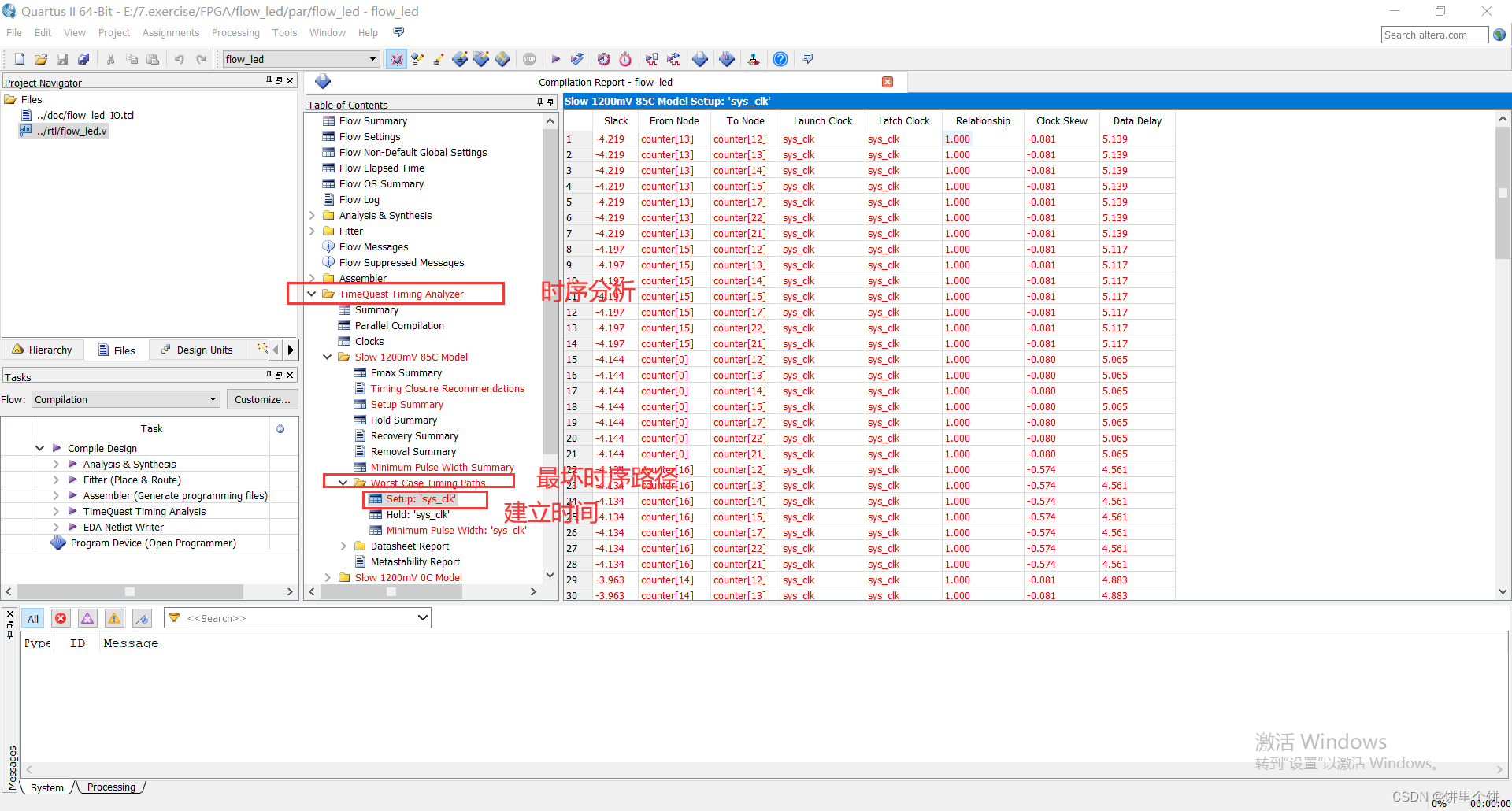

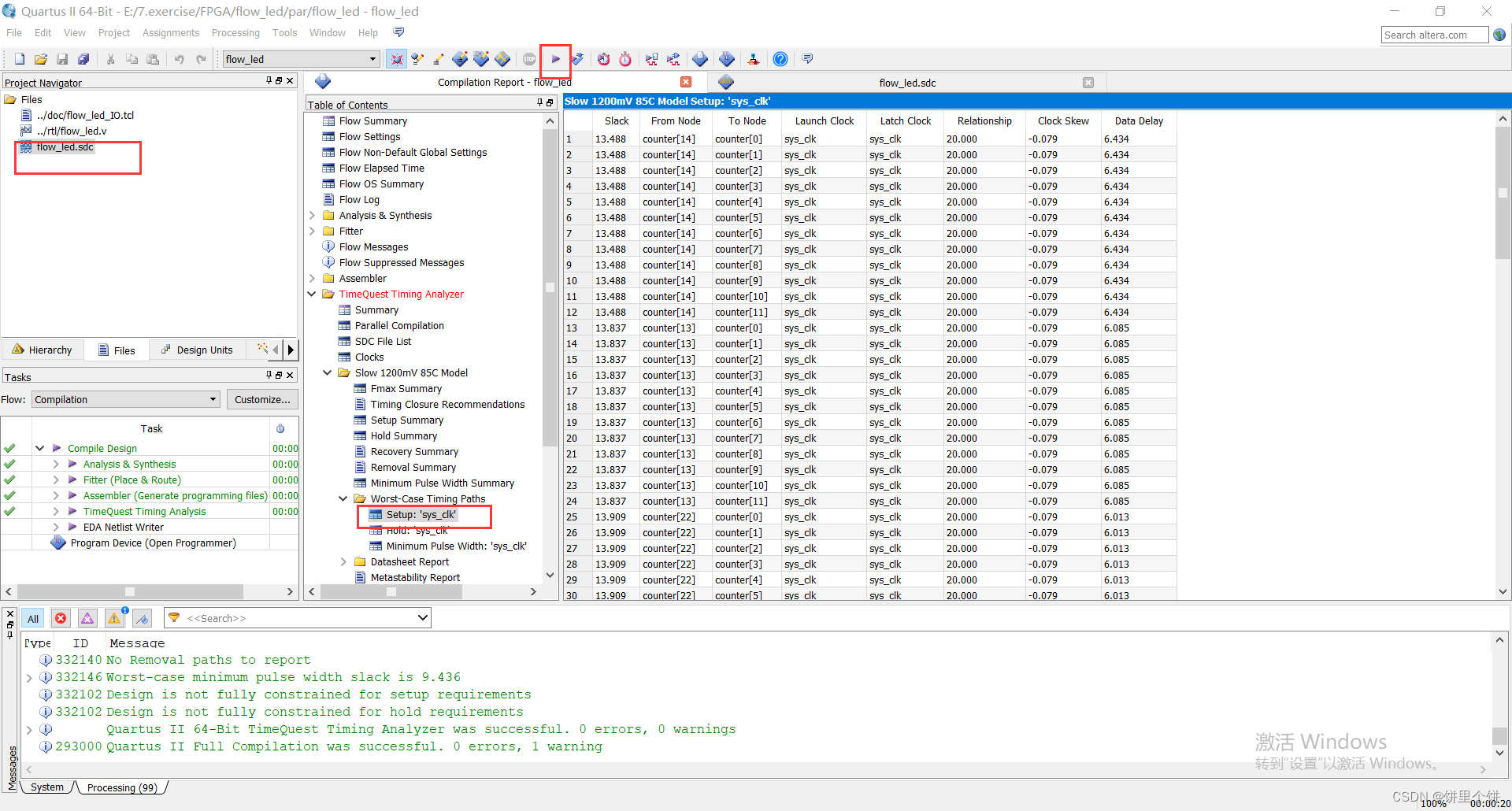

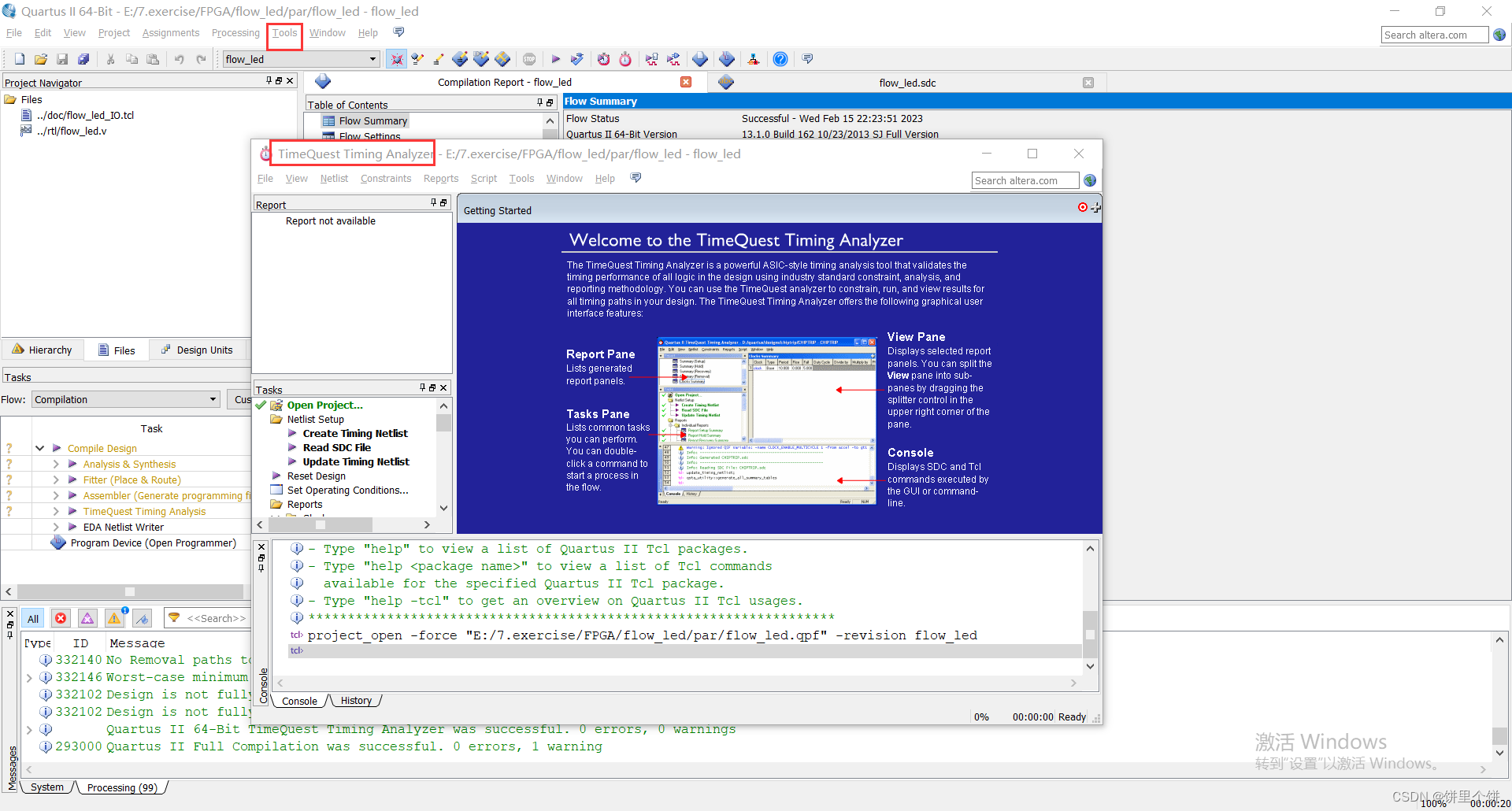

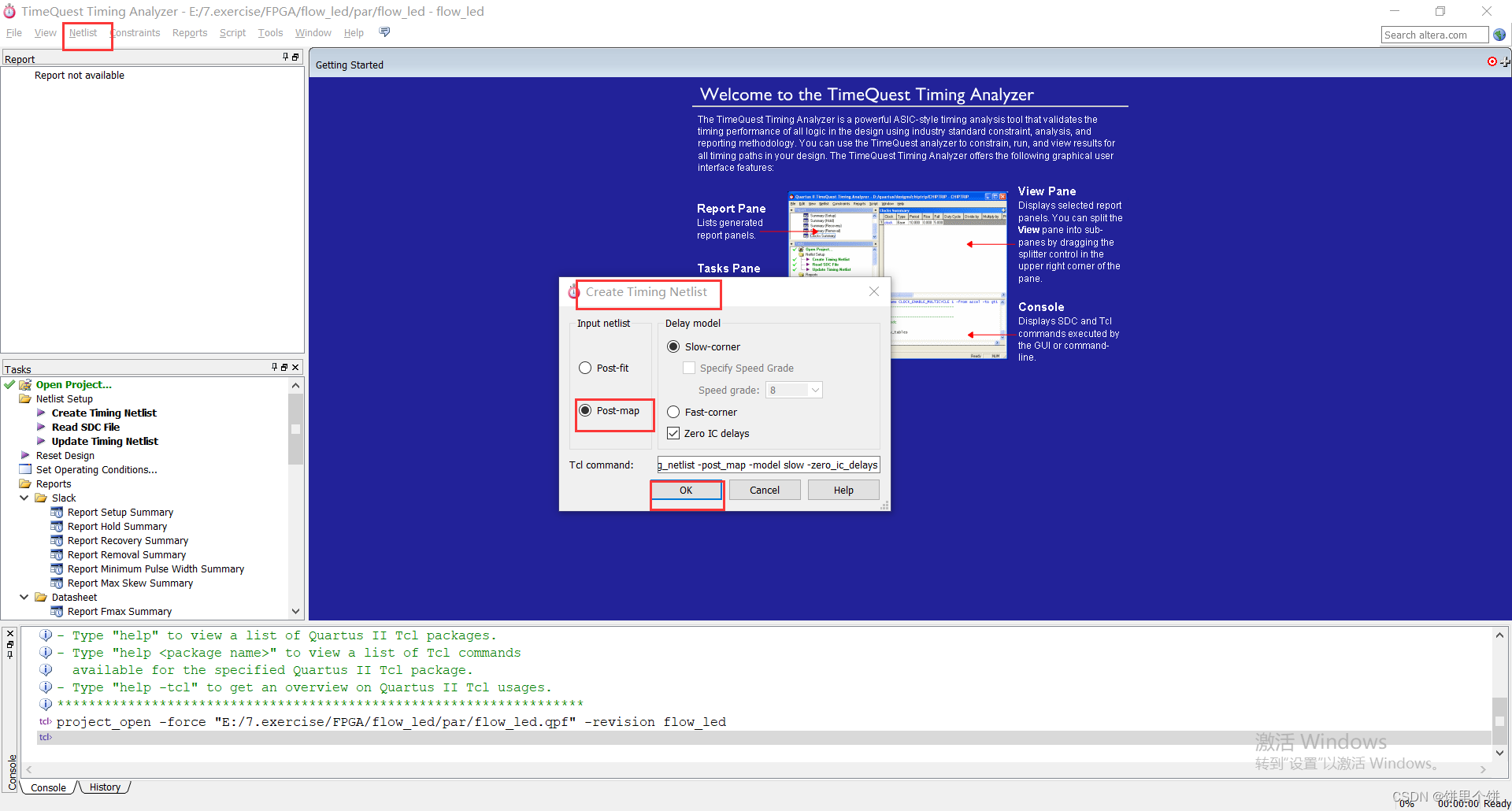

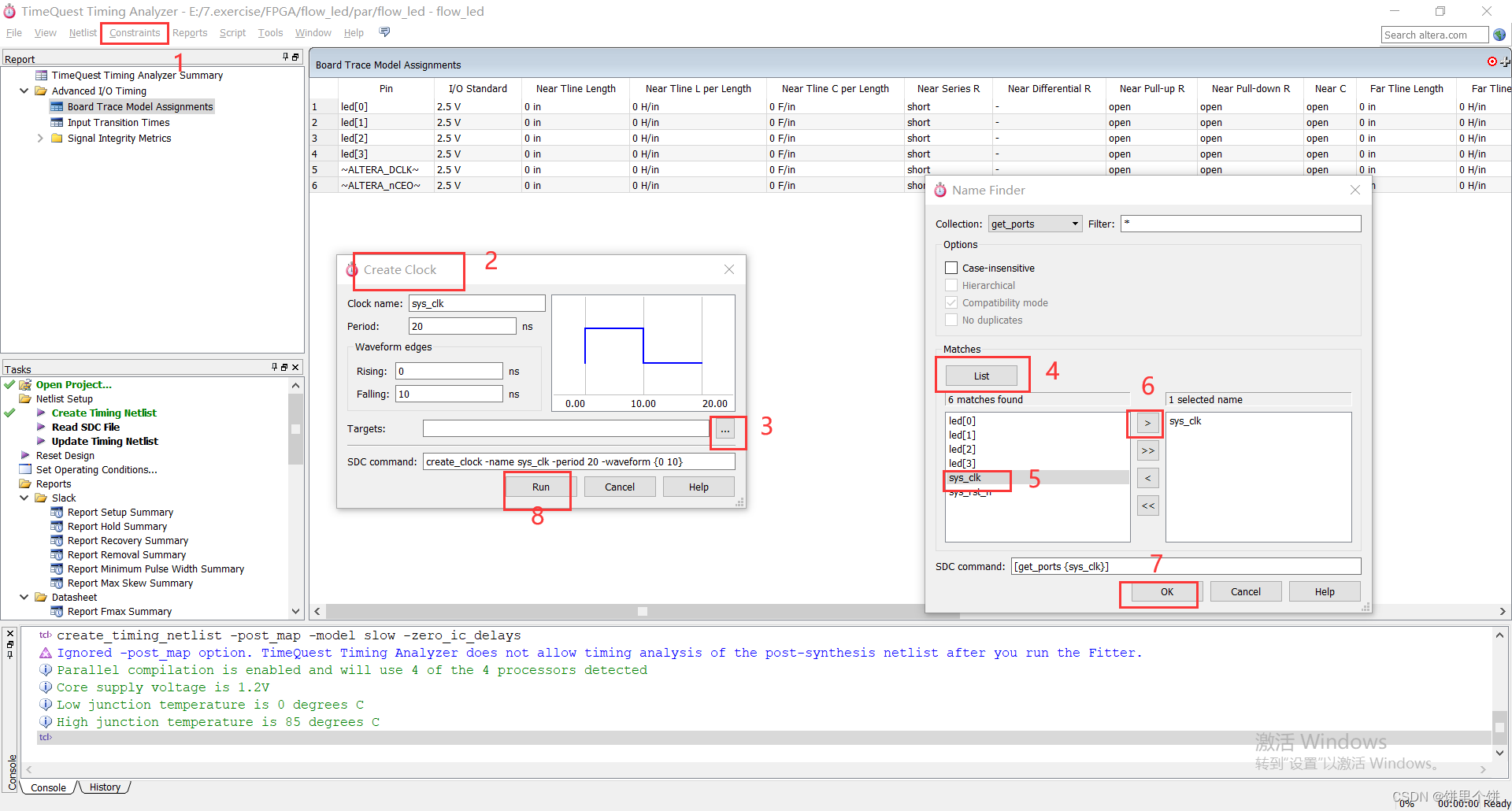

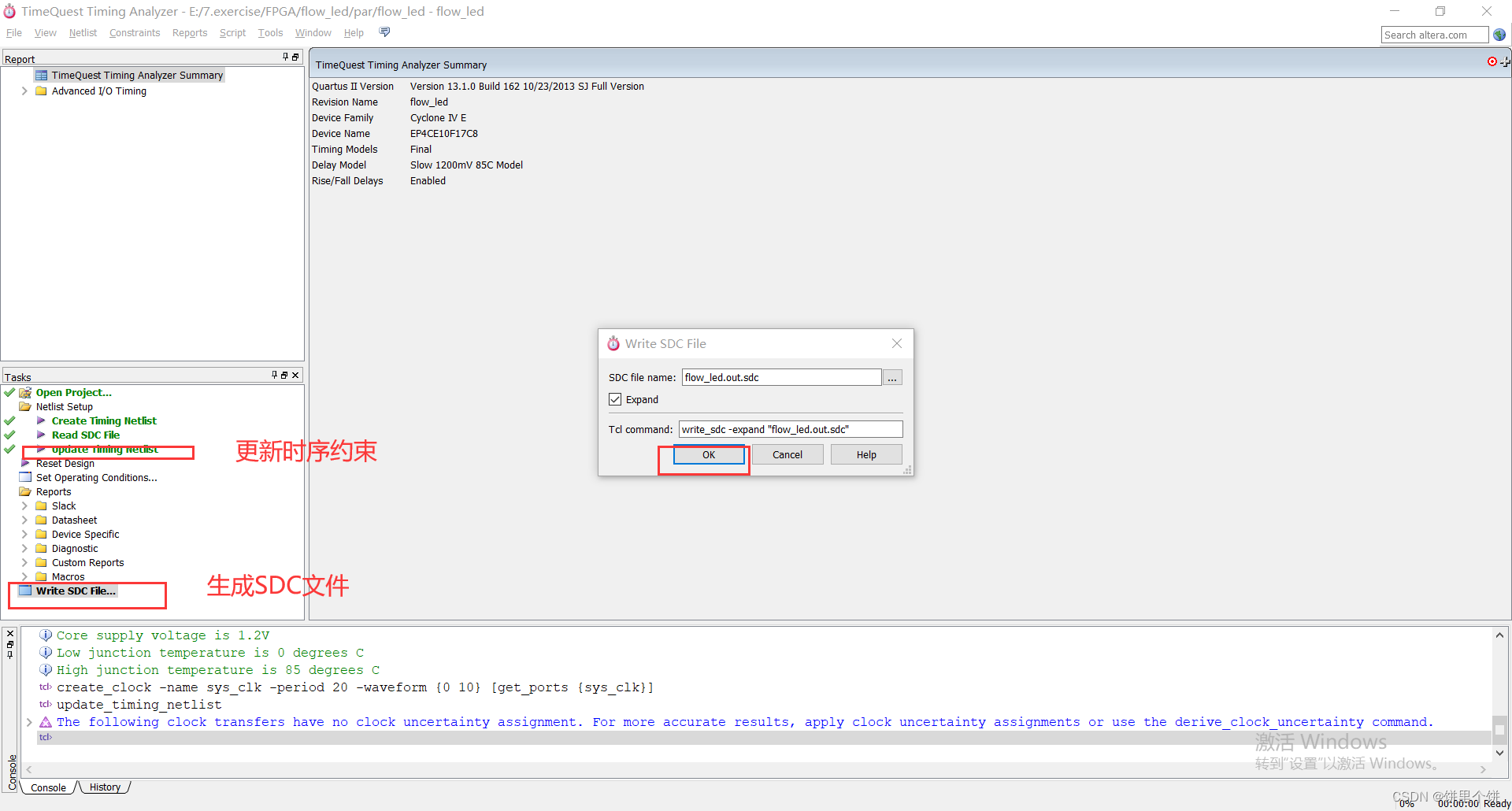

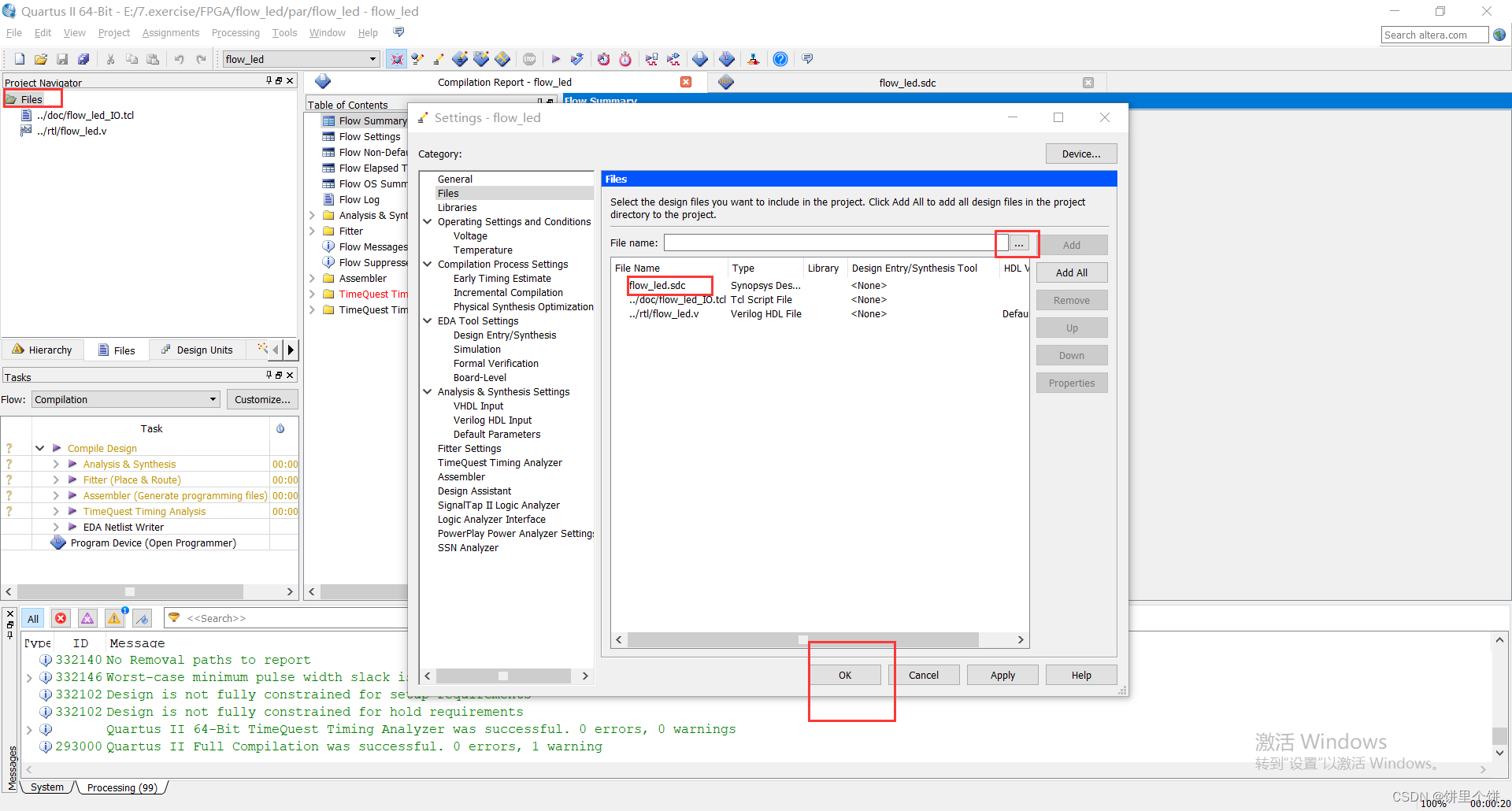

2.时序分析器

提示:先对工程进行分析与综合再进行时序约束

1990

1990

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?