二、AXI-LITE

1.AXI-LITE简介

AXI-LITE顾名思义即简化版的AXI协议,是对完整的AXI协议裁剪后的AXI协议;

特点:

- 突发长度永远是1,即只能单次读写,无法连续读写,常用于配置寄存器。

- 由于删减了逻辑,其资源也消耗较少。

- 地址映射,相较于AXI-STREAM,AXI-LITE的每个数据读写都需要对应的地址。

2.AXI-LITE系统框图

AXI-LITE的系统框图如下:

首先,AXI-LITE的读写通道分离,即AXI是一个全双工总线,在同一时刻可以同时进行读写操作;

其次,写通道又分为写地址通道,写数据通道,写响应通道;读通道又分为读地址通道,读数据通道。

所以一个AXI-Lite系统总共有五个通道,分别是:写地址通道,写数据通道,写响应通道,读地址通道,读数据通道。且这些通道内部传输数据都按照握手协议进行。

由于AXI-Lite是地址映射单次读写的,所以一个Waddr地址对应一个Wdata数据,Wdata存放于由Waddr指向的寄存器中;一个Raddr地址对应一个Rdata数据,读出从机中由Raddr指向的寄存器中的数据。

3.握手协议

由于AXI-Lite的总线大量使用了握手协议,故在此先对握手协议进行简单的介绍:

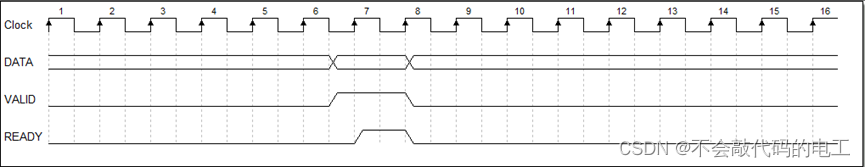

握手协议的信号一般为DATA、READY、VALID;

·**DATA:**由主机发出的,需要传输的数据;

·**VALID:**由主机发出的,标志DATA有效的信号(高电平表示有效,低电平表示无效)

·**READY:**由从机发出的,标志从机准备接收的信号(高电平表示准备接收,低电平表示不具备接受条件)

其时序如下:

当VALID与READY均有效时,数据完成传输。

·为什么需要用握手协议?

为了解决亚稳态的问题,数据在跨时钟域传输时,往往会出现亚稳态,为了避免亚稳态被采样,常常采用握手协议来传输数据;AXI中的握手协议可以保证每个通道的数据传输时,大大减小出现亚稳态的概率;且数据传输在VALID与READY信号同时有效时立即发生。

4.AXI-LITE信号表

| 通道 | 信号 | 方向 | 位宽 | 描述 | |

| AXI总线系统 | 系统信号 | AXI_ACLK | System | 1 | 系统时钟 |

| AXI_ARESENTN | System | 1 | 系统复位信号 | ||

| 写通道 | 写地址通道 | AXI_AWADDR | M->S | 由寄存器数量决定 | 写地址信号,指示当前所写寄存器的地址 |

| AXI_AWVALID | M->S | 1 | 写地址的有效信号(握手) | ||

| AXI_AWREADY | S->M | 1 | 写地址从机准备信号(握手) | ||

| 写数据通道 | AXI_WDATA | M->S | 32/24/16/8 | 写数据信号 | |

| AXI_WVALID | M->S | 1 | 写数据有效信号(握手) | ||

| AXI_WREADY | S->M | 1 | 写数据从机准备信号(握手) | ||

| AXI_WSTRB | M->S | 4 | 指示当前WDATA的位宽: 4’b0001:8位位宽 4’b0011:16位位宽 4’b0111:24位位宽 4’b1111:32位位宽 | ||

| 写响应通道 | AXI_BRESP | S->M | 2 | 写响应信号,在AXI-Lite中一般为2’b00 | |

| AXI_BVALID | S->M | 1 | 写响应数据有效信号(握手) | ||

| AXI_BREADY | M->S | 1 | 写响应数据主机接收信号(握手) | ||

| 读通道 | 读地址通道 | AXI_ARADDR | M->S | 由寄存器数量决定 | 读地址信号,指示当前所读寄存器的地址 |

| AXI_ARVALID | M->S | 1 | 读地址有效信号(握手) | ||

| AXI_ARREADY | S->M | 1 | 读地址从机准备信号(握手) | ||

| 读数据通道 | AXI_RDATA | S->M | 32/24/16/8 | 读数据信号 | |

| AXI_RVALID | S->M | 1 | 读数据有效信号(握手) | ||

| AXI_RREADY | M->S | 1 | 读数据从机准备信号(握手) | ||

| AXI_RRESP | S->M | 4 | 读响应信号,在AXI_Litezhong 通常为2’b00 | ||

| 其他 | 其他 | AXI_ARPORT | M->S | 1 | 保护信号,AXI_Lite中通常不使用 |

乍一看AXI_Lite的信号还是很多的,但实际上大多通道都是按照握手协议来定义信号的,所以不难理解。

5.AXI传输机制

AXI中每个通道的传输都有三种可能的情况:

1.VALID信号先有效,READY信号后有效

此时,当READY信号拉高时,立即完成传输

2.READY信号先有效,VALID信号后有效

此时当VALID信号拉高时,立即完成传输

3.READY与VALID信号同时有效

此时数据立马完成传输

不论是哪种传输机制,我们都需要搞清楚VALID与READY的约束关系,否则会出现死锁现象

VALID与READY的死锁:

发生在VALID等待从机的READY信号,同时READY也在等待主机的VALID信号;在这种情况下,VALID信号持续为0,等待READY信号的拉高;而READY信号也持续为0等待VALID信号的拉高;两个信号则同时处于低电平状态,则总线出现死锁;

解决:

对于这种现象,我们规定,VALID信号不能等待READY信号,即数据准备好则拉高,而READY信号可以等待VALID信号,即VALID信号拉高之后再拉高。

6.AXI读写时序

AXI发生一次写操作的具体过程:

- 首先主机将地址与数据分别放到写地址通道与写数据通道上,并将相应的VALID信号拉高,并等待从机发出的响应信号;

- 从机检测到写地址的VALID信号与写数据的VALID信号同时为高时,将数据写入到相应的寄存器中,并拉高READY信号,发出响应;

- 主机检测到READY信号与响应信号后,拉低VALID信号,从机将READY信号拉低。

读操作过程:

- 主机将读地址放到读地址通道上,并拉高VALID信号,等待从机的READY信号;

- 从机检测到读地址的VALID信号后,对读地址进行采样,并拉高REAY信号;

- 从机将读数据放到读数据总线上,并拉高VALID信号,主机检测到VALID后,将读数据采样,并拉高READY信号;主机拉低VALID信号 ,从机拉低READY信号。

读操作时序:

写操作时序:

三、AXI-STREAM

1.AXI-Stream简介

AXI-Stream(以下简称AXIS)是AMBA协议的AXI协议三个版本中最简单的一个协议;是AXI4中定义的面向数据流的协议,常用于对数据流的处理,如:摄像头、高速AD、Xilinx的AXI-DMA模块

在进行SOC设计中需要高速数据传输处理的场合,常常使用AXIS协议;

AXIS与AXI-FULL的区别:取消了Address Write/Address Read通道;取消了反馈响应信号Bresp和Rresp;半双工,仅能读或者写;不允许乱序;无最大突发传输长度;包括TID信号指示源,TDEST指示目的地;包括一个用于插入和溢出空字节的TKEEP信号。

2. AXI-Stream端口信号(Master)

以AXIS主机接口的信号为例,AXIS的信号表如下:

| 信号 | 方向 | 描述 |

| ACLK | input | 系统时钟信号 |

| ARESTN | input | 系统复位信号 |

| TVALID | output | 数据有效信号,握手协议 |

| TREADY | input | 准备接收信号,握手协议 |

| TDATA | output | 数据线,数据传输 |

| TSTRB | output | 流格式 |

| TKEEP | output | 主机数据有效信号,高电平则字节有效,低电平则数据有效,为空字节 |

| TLAST | output | 表示最后一个字节,下一个clk数据将无效 |

| TID | output | 源地址,多机通信 |

| TDEST | output | 目的地址,多机通信 |

| TUSER | output | 用户自定义,多机通信 |

AXIS的所有信号都在ACLK的上升沿被采样;

TVALID: TVALID是数据有效信号,若TVALID为高电平,标志着TDATA数据线上的数据是有效的,能够被取走,TVALID信号与TREADY信号是一组握手信号;

TREADY:TREAY是指从机是否准备好接收数据,若TREADY为高电平,则标志着从机此时已经准备好接收数据,TREADY信号与TVALID信号是一组握手信号;

TDATA:数据通道,位宽可以是8 、16、32;当TVALID与TREADY均为高电平(有效)时,TDATA数据被传递;

TLAST:数据流结束信号,当TLAST为高电平时,说明此时传输的数据为数据流的最后一个数据;在Xilinx的AXI-DMA中,TLAST信号可以控制整个数据流传输的结束(当传输过程中TLAST为高,则结束一次DMA传输);

我们可以发现,本质上AXIS协议也就是握手协议,只不过增加了一个TLAST信号,和一些其他的附带指示其他信息的信号;如TID、TDEST、TUSER等都是用于多级通讯的,在单一数据流方向的系统中,我们只需要关注上述几个重要的信号即可。

3.AXI-Stream数据字节类型和流格式

·数据字节(Data Byte):包含在源和目标之间传输的有效信息的数据字节。

·占位字节(Position byte):表示流内部数据字节的相对位置的字节。这是一个不包含在源和目标之间传输的任何相关数据值的占位符。

·空字节(Null byte):不包含任何数据信息的字节或关于流内数据字节的相对位置的任何信息。

字节流:

在每次握手之后,可以传输任何数量的数据字节,NULL字节 没有含义,可以插入或删除。

| Word1 | Word2 | Word3 | Word4 |

| NULL | 0A | NULL | b1 |

| NULL | NULL | 06 | b4 |

| 01 | a1 | 18 | d2 |

| 02 | NULL | 1a | 4f |

连续对齐流:

即数据本身就是对齐的,可以直接写入内存

| Word1 | Word2 | Word3 | Word4 |

| 01 | 0A | b4 | b1 |

| 02 | 0A | 06 | b4 |

| 01 | a1 | 18 | d2 |

| 02 | 06 | 1a | 4f |

连续不对齐流:

数据包只有18B,但是对齐需要20B/24B,这个时候就需要引入占位字节;

| Word1 | Word2 | Word3 | Word4 |

| 01 | 0A | b4 | Position |

| 02 | 0A | 06 | Position |

| 01 | a1 | 18 | d2 |

| 02 | 06 | 1a | 4f |

稀疏流:

允许数据流的中间也有占位符;

| Word1 | Word2 | Word3 | Word4 |

| 01 | 0A | Position | b1 |

| Position | 0A | 06 | Position |

| 01 | Position | 18 | d2 |

| 02 | 06 | Position | 4f |

不同字节类型指示:

| TKEEP | TSTRB | Data Type |

| HIGH | HIGH | 数据 |

| HIGH | LOW | 占位符 |

| LOW | LOW | 空字节 |

| LOW | HIGH | 保留(无定义) |

可自定义省略的信号:

TID、TDEST、TUSER:自定义,多传输系统中使用

TLAST:常为1或0

TKEEP和TSTRB:全部为1或0

TREADY:时刻准备接收,数据反压问题

4.数据反压

数据流源源不断地涌入,但从机处理数据能力有限,导致输入数据量大于输出数据量。

·发送端:当保留TREADY信号时,从机若处理不了数据时,可以将数据缓存。若去掉TRADY信号,则处理不了的数据只能溢出。

·接收端:若去除TREADY信号,则说明接收端的处理数据速度大于发送端,数据可以持续输入。

8139

8139

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?