转自:https://blog.csdn.net/weixin_30481087/article/details/97656924

首先给出一篇很好的文章:

Zynq构建SoC系统深度学习笔记-05-PL读写DDR3

http://www.eefocus.com/antaur/blog/17-08/423773_0818c.html

这个博主的一系列文章写的很好,本文是在阅读了他的博客后,才下定决心查阅相关文档进一步去研究这个问题

下面给出自己的理解:

一、SoC地址空间分配(查看UG585)

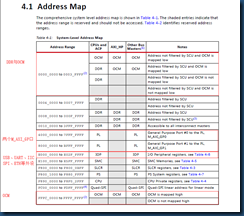

在UG585的第4章第1节给出了ZYNQ的地址分配,如下图所示:

从上图可以看到:总的地址空间为4G(32bits地址总线)

1、从0地址开始的1G为DDR与256KB的OCM空间,注意OCM的分配较为复杂,

后续会介绍

2、从0x4000_0000开始的1G为M_GP0的空间

3、从0x8000_0000开始的1G为M_GP1的空间

4、从E000_0000开始的为USB、SPI、IIC、ETH这些外设的空间

5、然后从FFFC_0000开始的256KB中分配给OCM(OCM分配方式有两种,后面会说到)。

6、剩余的较少用,以此类推

二、ZYNQ中主机、从机、连接

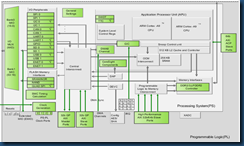

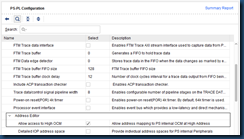

在vivado中打开processing system IP可以看到:

1、外设有两组:IO Peripheral为一组,flash memory为一组。同一组的共用一个地址空间。

2、接口有四种:M_GP,S_GP,S_HP,S_ACP

3、内部互联有:Central Interconnect、Programmable Logic to Memory Interconnect、

OCM Interconnect

4、HP接口有四个,但是从Programmable Logic to Memory Interconnect出来到DDR Controller的接口只有两个。查阅文档可以知道HP0和HP2共用1个,HP1和HP3共用1个

5、只有PS/PL接口通过内部的互联有通路到的外设或者存储,都可以通过这个接口访问

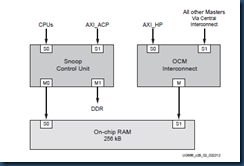

比如OCM接口可以有四种访问方式:

a:M_GP->Central Interconnect-> OCM Interconnect->OCM

b: HP->Programmable Logic to Memory Interconnect->OCM Interconnect->OCM

c: ACP->SCU->OCM Interconnect->OCM

d: CPU->SCU->OCM Interconnect->OCM

三、Vivado中的address editor地址分配

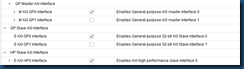

1、建立实例工程:确定主机、从机与连接

添加dma和自定义master IP核:红色圈出的为主机、黑色圈出的为PL中的从设备

使能OCM

总共有3个主设备,分别为:dma、my_master、ps

总共有5个从设备,分别为:DDR、IOP、QSPI、OCM、AXI_GPIO

AXI_BRAM_CONTROLLER

确定接口:

两个主机都连接到S_GP口

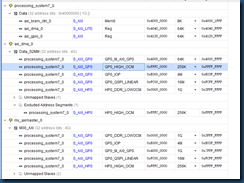

2、进行地址分配地址分配

如下图所示:进行地址分配时会以主机分组,因此有3组,根据主机是否有对应的连接到从机,从而决定从机是否在这个组里

地址分配时需要注意的事项

1、当prossing system作为主机时,也就是CPU使用M_GP作为主机时,地址分配界面是不会出现DDR、IOP、OCM的。这是因为在zynq中M_GP没有相应的内部连接到这些设备。M_GP是连接到PL的设备的。工程使用M_GP0,因此这些设备的地址是从0x4000_0000开始。

2、使能S_GP口,可以看到DDR、IOP、QSPI、OCM可以相应的主机访问被定义地址

3、多个主机可以连接到同一个从设备,访问同一地址空间,使用interconnect进行交换

4、一个主机可以访问多个从设备,从设备的地址不能一样

5、同一主机对同一从设备的访问不能通过不同的接口,比如dma同时使用GP和HP访问DDR,会产生冲突

6、系统中作为从设备的任意两个它们的地址都不能一样,不管其主机是否相同。一个从设备只有 一个地址,是根据zynq地址空间直接统一编址的。比如,不管使用DDR被什么主机使用什么接口访问,其地址都是0x0000_0000-0x3FFF_FFFF。

7、如果主机不需要访问某个从设备,可以使用Exclude Segment功能,如下图所示,详细请看UG994的chapter 3.

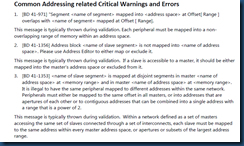

8、常见的地址分配错误

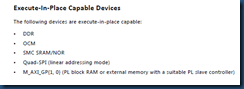

四、可以直接运行程序的存储设备

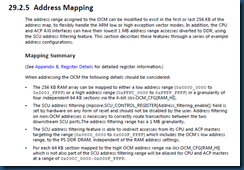

五、关于OCM的地址分配

详细请看UG585的OCM这一章

通过不同的设置来修改OCM的地址分配

六、参考资料

1、UG585-Zynq-7000 All Programmable SoC

Technical Reference Manual

2、UG994-Vivado Design Suite User Guide

Designing IP Subsystems Using IP Integrator

3、http://www.eefocus.com/antaur/blog/17-08/423773_0818c.html

转载于:https://www.cnblogs.com/Ariza123/p/9086026.html

5812

5812

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?