文章目录

- 一.FIFO介绍

- 二.代码实现

- 三.总结

一.FIFO介绍

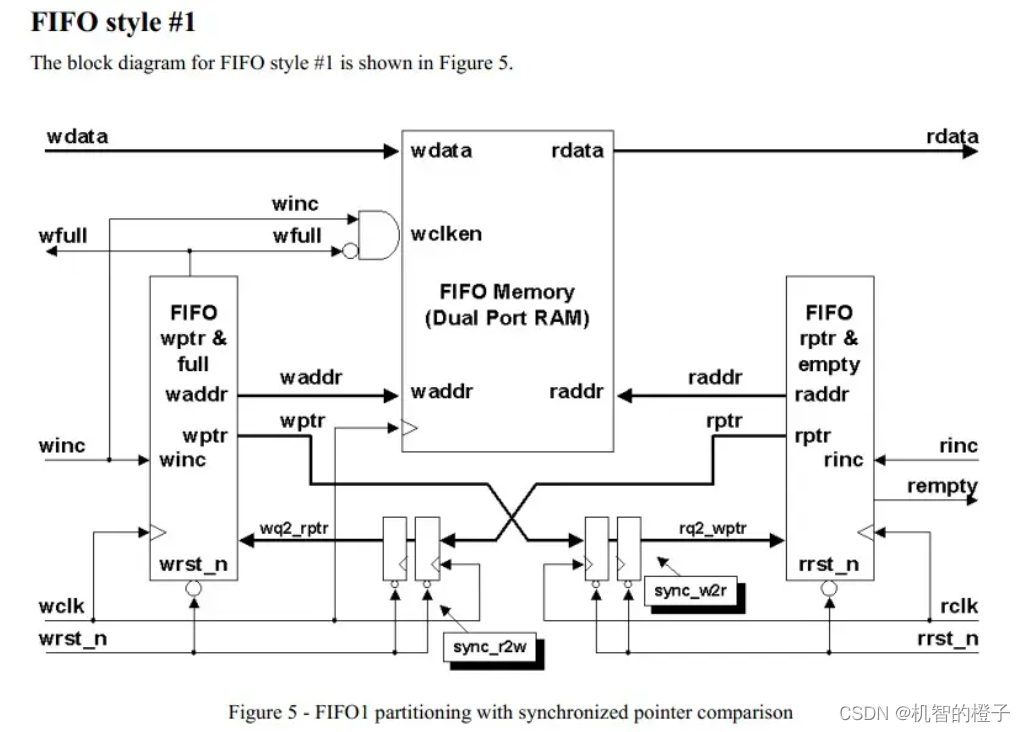

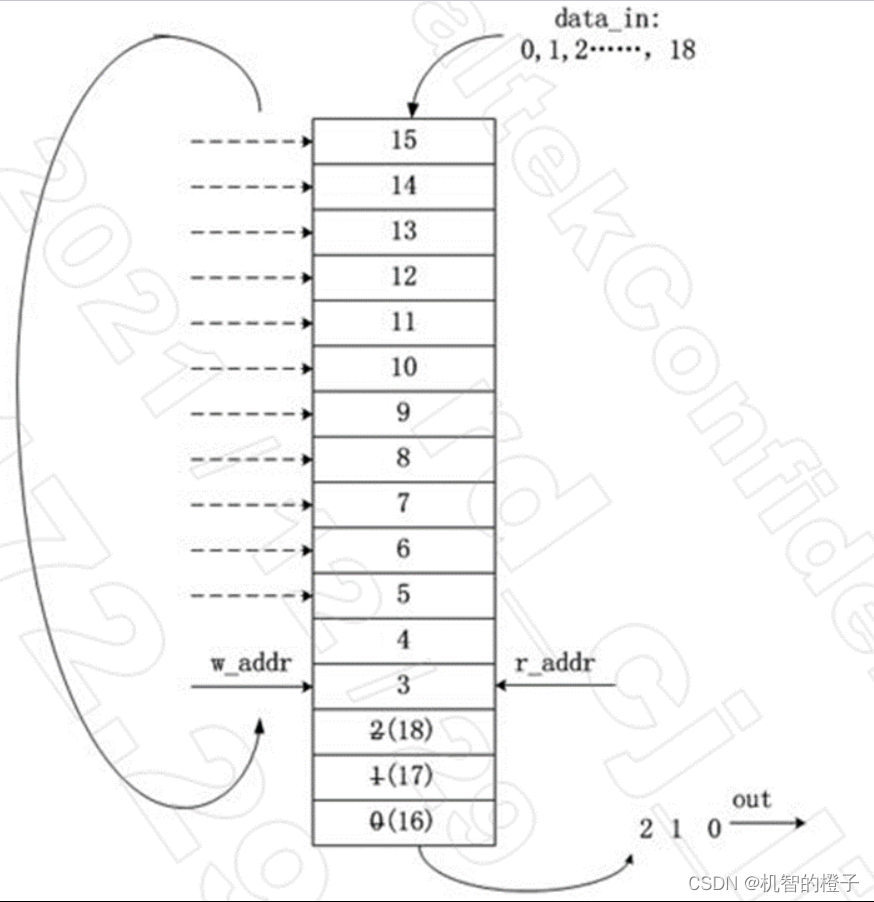

FIFO( First Input First Output)指先进先出。其结构图如下:

异步FIFO读写操作是在两个不同的时钟域下完成的,FIFO需要比较读写地址指针的数值才能给出空满指示信号,这就涉及到了信号的跨时钟域处理。对于单比特信号,通常采用一位同步器进行同步,也就是打两拍操作,但对于多比特数据,如果也进行打两拍操作,由于数据各比特变化时间不一致,就会产生错误的情况,为了解决这个问题,我们通常使用格雷码进行异步FIFO读写地址的同步。

格雷码是什么?

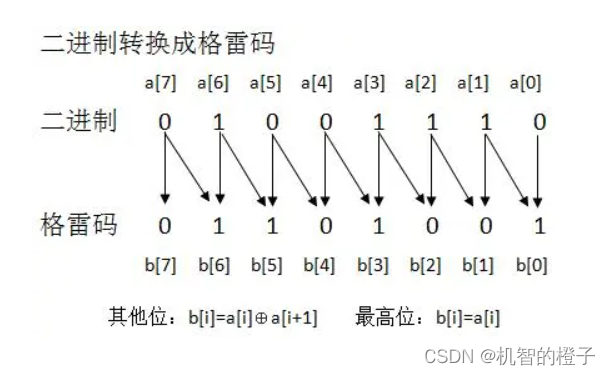

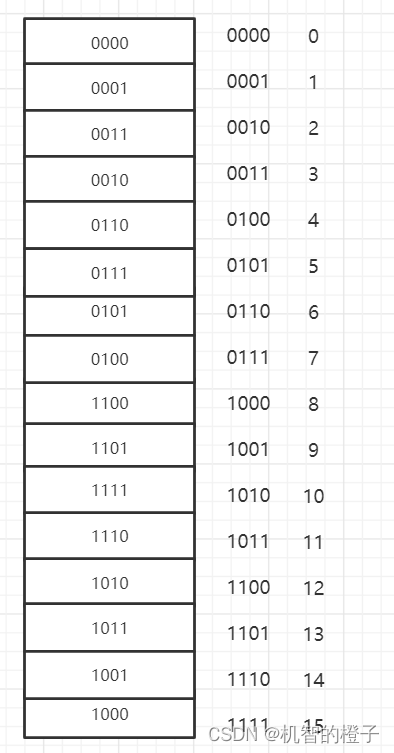

在一组数的编码中,若任意两个相邻的代码只有一位二进制数不同,则称这种编码为格雷码(Gray Code),另外由于最大数与最小数之间也仅一位数不同,即“首尾相连”,因此又称循环码或反射码。在数字系统中,常要求代码按一定顺序变化。例如,按自然数递增计数,若采用8421码,则数0111变到1000时四位均要变化,而在实际电路中,4位的变化不可能绝对同时发生,则计数中可能出现短暂的其它代码(1100、1111等)。在特定情况下可能导致电路状态错误或输入错误。使用格雷码可以避免这种错误。格雷码有多种编码形式。在这里我们使用的是典型格雷码。编码方式是:对于二进制数的最高位不变,然后最高位和次高位依次异或得到格雷码后面位的值,具体操作如下图:

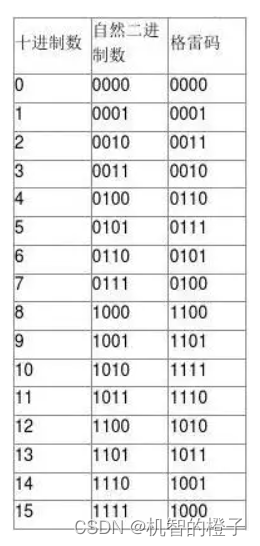

四位二进制数和格雷码对应表如下:

二.代码实现

端口信号:

对于异步FIFO来说,由于读写两侧的时钟频率不同,所以相关指示信号有两份,分别基于不同的时钟域。

rst_n ,//异步复位 低电平有效

//写侧信号

wrclk ,//写时钟

wrreq ,//写请求

wrdin ,//写数据输入

wrfull ,//写满标志

wrempty ,//写空标志

wrusedw ,//写时钟域下的可读数据量

//读侧信号

rdclk ,//读时钟

rdreq ,//读请求

rddout ,//读数据输出

rdfull ,//读满标志

rdempty ,//读空标志

rdusedw //读时钟域下的可读数据量

二进制数和格雷码之间的转换:

function [ADDR_W:0] BIN_GRAY(input op_code,input [ADDR_W:0] data);

integer i;

begin

if(~op_code)begin //二进制转格雷码

BIN_GRAY = (data >>1) ^ data;

end

else if(op_code)begin //格雷码转二进制

BIN_GRAY[ADDR_W] = data[ADDR_W];

for(i = ADDR_W-1;i >= 0; i = i - 1)begin

BIN_GRAY[i] = BIN_GRAY[i+1] ^ data[i];

end

end

end

endfunction

判空标志信号:

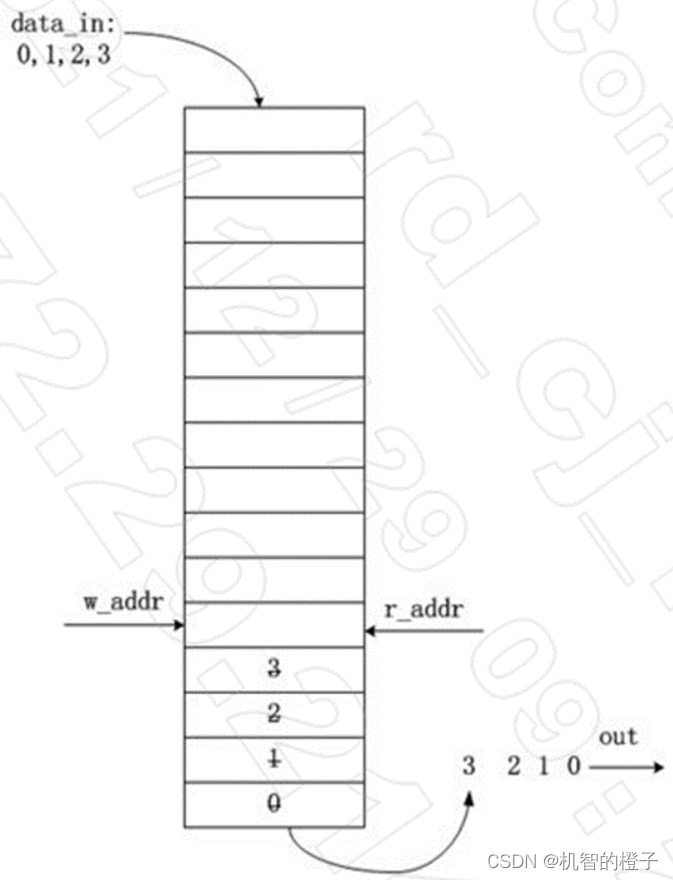

FIFO拥有两个地址指针,读指针指定当前读地址,写指针指定当前写地址,当读指针追上写指针使得两指针相同时,意味着FIFO为空。

判满标志信号:

当写指针写完一轮再次遇到读指针时,则意味着FIFO写满了。

那么我们可以说读写地址相同,FIFO为满吗?当然不行,上面说了,我们将读写指针相同时用来判断FIFO空信号。那么我们怎么解决这个问题呢?还记得前面我们使用的格雷码吗?格雷码除最高位外,具有镜像对称的特点,我们可以利用该特性来判断FIFO是否为满状态。对于深度为n的FIFO,我们为其地址的格雷码增加一位最高位。现在我们以一个深度为8的FIFO为例:

深度为8,则地址位宽为3,我们增加一位变为4。如果以格雷码作为判断FIFO空的条件,依然是读写指针的对应格雷码相同。但对于满信号,由于格雷码具有除了最高位,其余位呈镜像对称的特点,我们可以根据两格雷码数除了最高位和次高位不同,而其余位的值完全相同来判断fifo是否被写满,例如0100和1000,此时不管是写指针的格雷码为0100还是1000,读写指针之间均相隔8,达到了fifo的最大深度。

assign wr_full = wr_pointer_g == {~wr_rdptr_sync_r1[ADDR_W -:2],wr_rdptr_sync_r1[ADDR_W-2:0]};//写侧满标志 写侧接收到读指针格雷码 判断满条件最高位和次高位不相同

assign rd_full = rd_pointer_g == {~rd_wrptr_sync_r1[ADDR_W -:2],rd_wrptr_sync_r1[ADDR_W-2:0]};//读侧满标志 读侧接收到写指针格雷码 判断满条件最高位和次高位不相同

完整代码:

略

三.总结

异步FIFO的关键就在于使用格雷码跨时钟传输地址指针以及FIFO空满信号的判断,对于单比特数据可以采取两级寄存器进行同步,而对于多比特数据除了可以使用格雷码+一位同步器的方式进行同步外,还可以使用FIFO桥接的方式。

本文介绍了异步FIFO的工作原理,重点讲解了使用格雷码解决跨时钟域问题,以及如何判断FIFO的空满状态。通过二进制与格雷码的转换,以及详细阐述读写地址的同步机制,揭示了FPGA异步FIFO设计的关键点。

本文介绍了异步FIFO的工作原理,重点讲解了使用格雷码解决跨时钟域问题,以及如何判断FIFO的空满状态。通过二进制与格雷码的转换,以及详细阐述读写地址的同步机制,揭示了FPGA异步FIFO设计的关键点。

1516

1516

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?