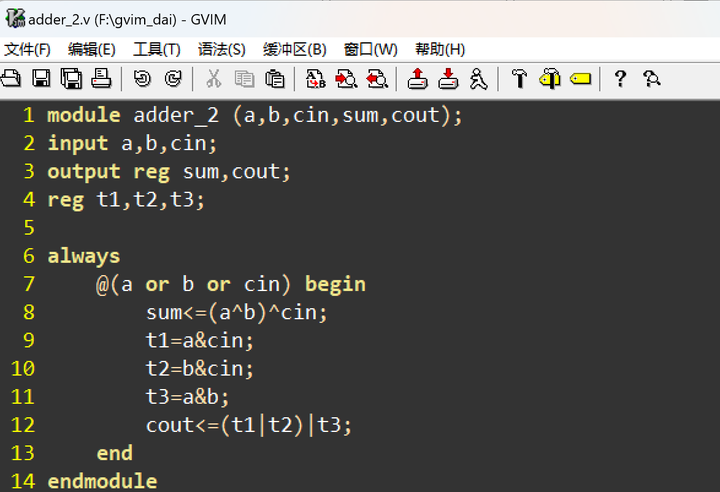

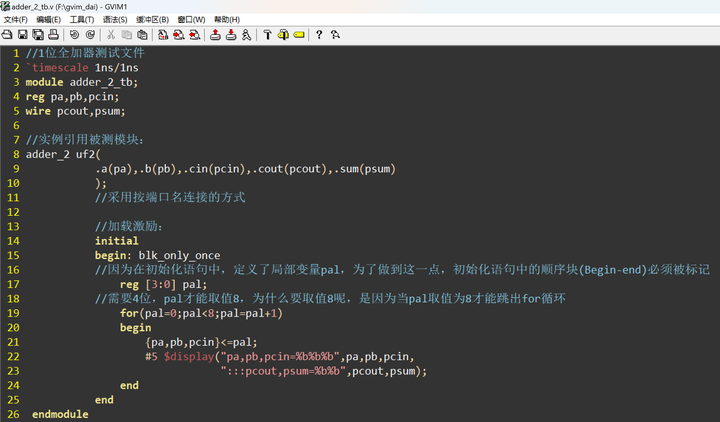

1.我是用第三方编辑器Gvim编写两个v.文件,一个是源设计文件"adder_2.v",一个是激励文件testbench文件"adder_2_tb.v"。代码如下:

图1 1位全加器设计文件代码

图2 1位全加器激励文件代码(testbench文件)

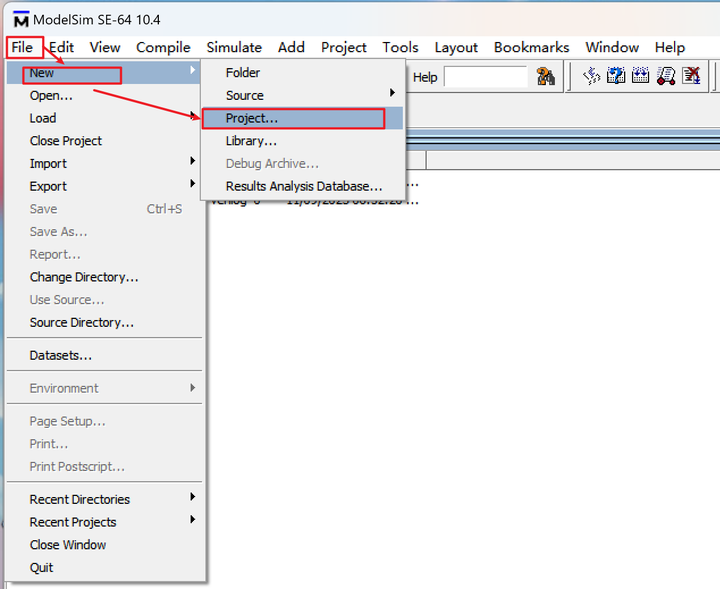

2.双击打开Modelsim软件,【File】--【New】--【Project】,新建工程,如下:

图3 启动Modelsim,新建工程

图4 新建工程

新建工程并保存:“Project Name”敲入project名称:adder_2,点击【Browse…】,选择你想保存工程的位置。点击【OK】。

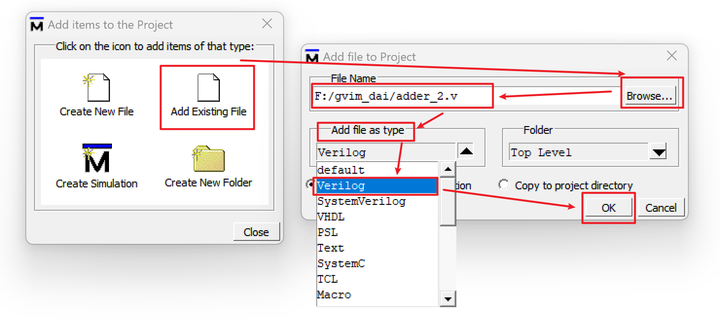

3.添加项目到新建的工程中。新建工程点击【OK】--【YES】后,会弹出下图左侧窗口,点击【Add Existing File】,会弹出下图右侧窗口,点击【Browse…】,选择最初编写的设计文件“adder_2.v”的保存路径,注意:【Add file as type】处要改选成"Verilog",点击【OK】。接下来用同样的方法,把激励文件“adder_2_tb.v”添加到工程中。然后点击【Close】,把下图左侧窗口关闭即可。

图5 添加项目到新建工程中

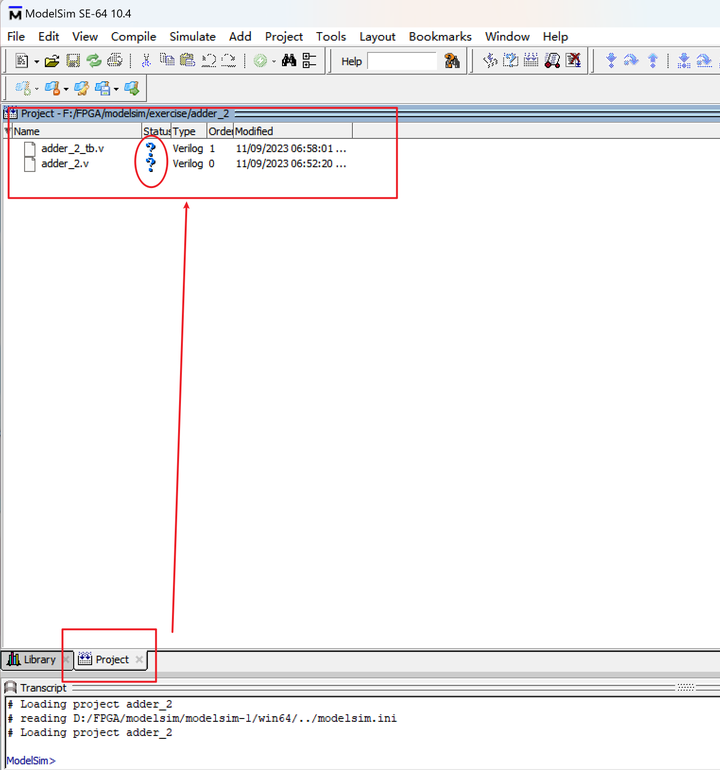

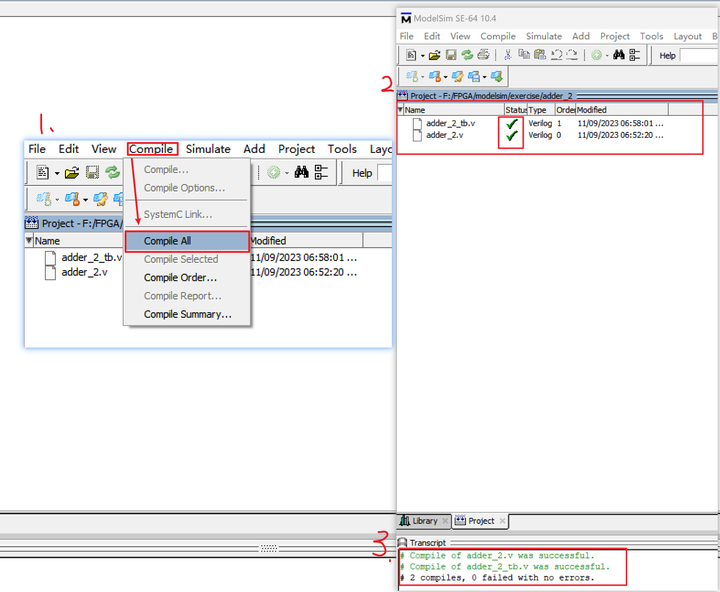

4.编译工程。

编译前:在“Project”选项卡栏,可以看到两个文件状态都是“?”。

编译:点击【Compile】--【Compile All】。

编译后:在“Project”选项卡栏,可以看到两个文件状态都是“√”,“Transcript”窗口语句显示两个文件都无错误。如此表示已编译成功,接下来可以进行仿真。

注意:如果没有编译成功,可以点击“Transcript”窗口Error红色语句,弹出的窗口会提示代码出错的位置,进行修改即可。

图6 编译前状态

图7 编译代码(编译成功)

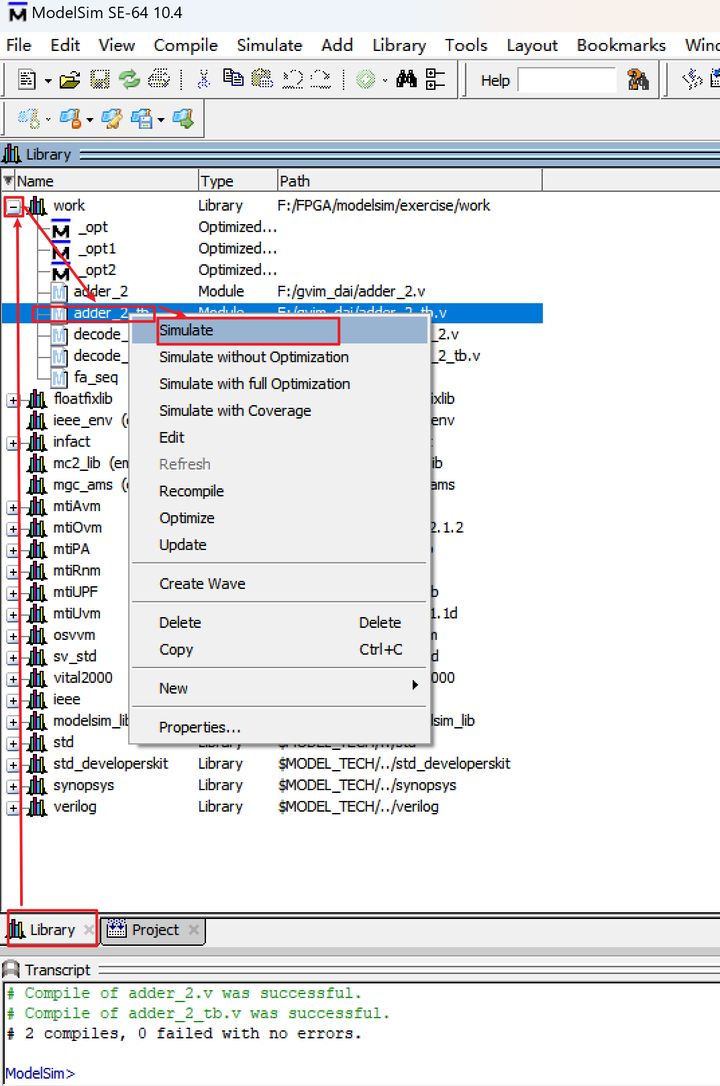

5.仿真。点击进入“Library”选项卡栏,再点击【work】库前面的加号,在展开的文件中找到的adder_2_tb测试文件,这就是我们要仿真的文件。右键点击testbench文件,选择【Simulate】。跳转到另一个界面。

图8 仿真

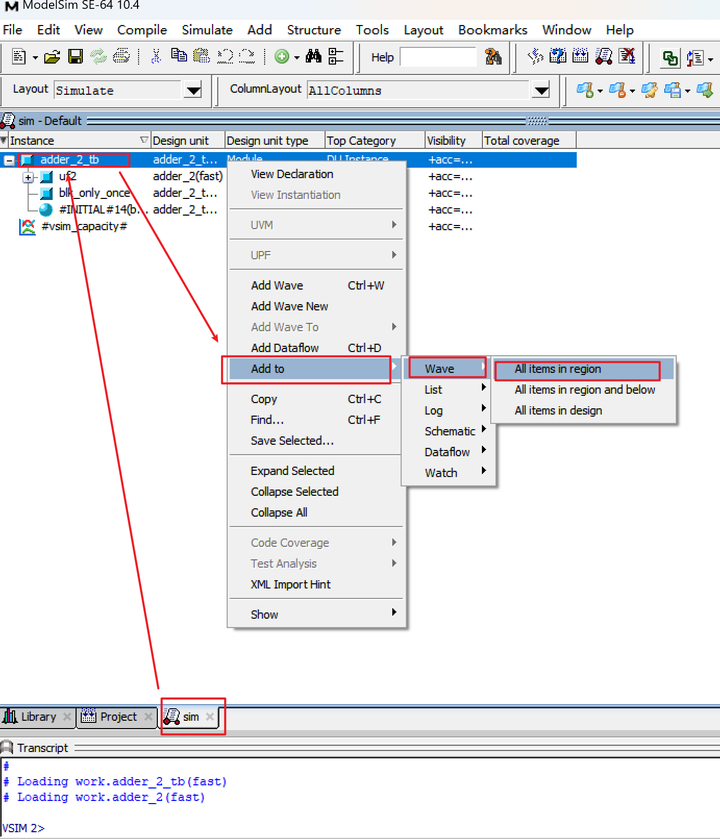

在“sim”界面,右键点击【adder_2_tb】文件处,依次选择【Add to】--【Wave】--【All items in region】。设置仿真时间,这里我设成200ns。

仿真:在最下面的命令行窗口输入”run”,或者选中【Simulate】--【Run】--【Run-All】。

图9 仿真

图10 开始仿真

6.仿真结果

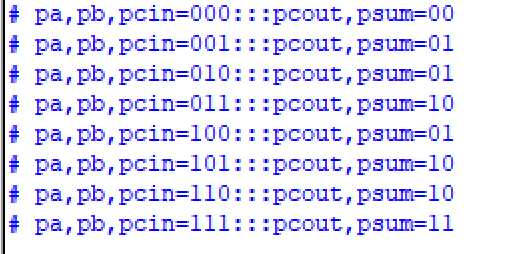

“Transcript”窗口显示

图11 仿真结果

仿真波形分析

图12 仿真波形

tips:

1)“Wave”界面中,在波形处右键【Zoom full】或者点击“放大镜”图标可以观看整个波形,想放大某一部分时鼠标点击某一处,按住ctrl转动鼠标滑轮可以放大和缩小;

2)“Wave”界面中,选中信号右键点击【Radix】可以选择进制;

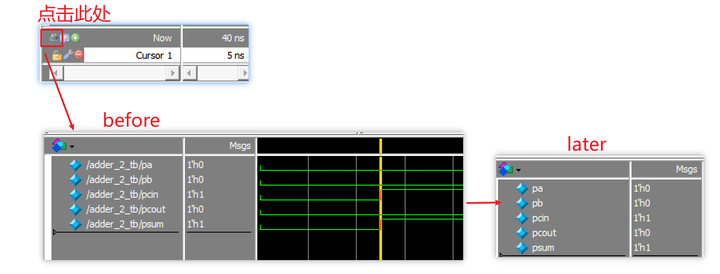

3)“Wave”界面中,点击左下角小方框所示处,则不会显示信号的路径名称,方便观察。

图13 隐藏路径名称

至此,实现使用Modelsim仿真成功1位全加器。耶✌

5821

5821

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?