一、FPGA主要六部分组成:可编程输入输出单元(IO)、可编程逻辑单元(CLB)、完整的时钟管理、嵌入式块状RAM、布线资源、内嵌的底层功能单元和内嵌专用硬件模块。

二、可编程逻辑单元(Configurable Logic Block, CLB)

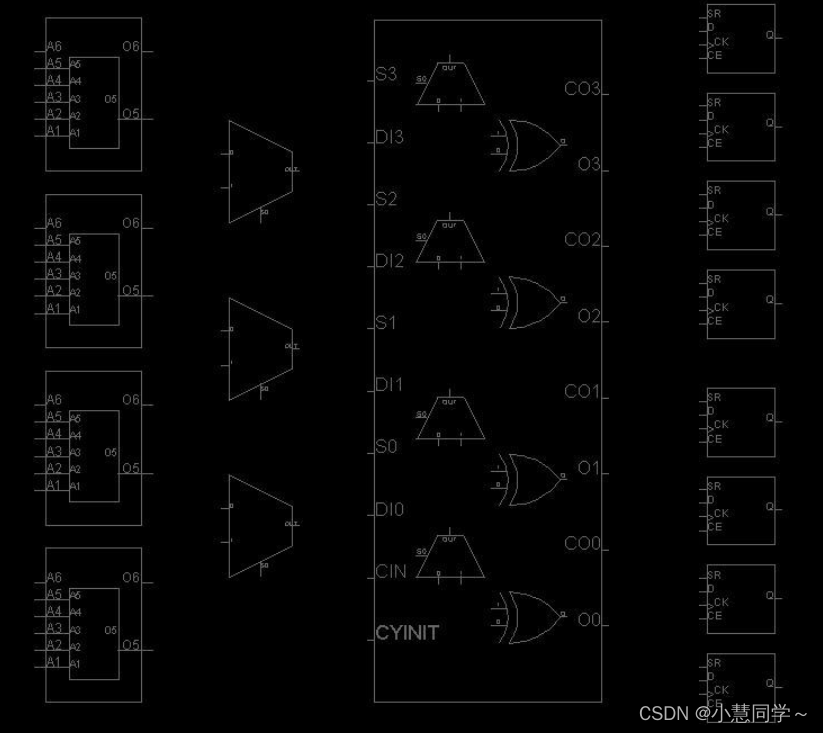

1.既可以实现组合逻辑,也可以实现时序逻辑。由2块SLICE组成。SLICE分为SLICEL和SLICEM两种。两者内部都包括4 个 6 输入查找表(Look-Up-Table,LUT6)、3 个数据选择器(MUX)、1 个进位链(Carry Chain)和 8 个触发器(Flip-Flop);

SLICEL

(1)SLICEL和SLICEM的区别主要就在LUT6上。SLICEL和SLICEM的LUT6 都具有6个地址输入线(A1-A6),2个输出口(O5-O6),但是SLICEM的LUT6更复杂,还多了写地址输入线(WA1-WA8),写数据端(DI1 DI2),写使能端(WE),而SLICEL的LUT6没有。这导致SLICEL的LUT只具有存储数据的能力,只能作为ROM使用,而SLICEM的LUT还具备了数据写入的功能,可以作为DRAM或移位寄存器使用。

LUT6作为 ROM 使用,配置为 64x1(占用 1 个 LUT6,64 深度,1 宽度)、128x1(占用 2 个 LUT6)和 256*1(占用 4 个 LUT6)的 ROM。

3. SLICEL和 SLICEM的区别在于LUT6上,

4.xilinx7 的时钟

3735

3735

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?