1. 理论

1.1 由来

AXI是ARM AMBA中的一部分

1.2 存储器映射

主机对从机进行读写操作时,指定一个目标地址,这个地址对应系统存储空间的地址,表示对该空间进行读写操作也就是说,通过对系统存储空间的读写操作来控制对从机的读写操作,相当于把从机映射到主机的存储空间!!

1.3 三种类型

1. AXI4 FULL用于高性能存储器映射需求

- AXI4 LITE->对寄存器进行配置和读写

简化版的AXI4接口,对于简单的,低吞吐率(low-throughput)的存储器映射通信,比如读写控制寄存器和状态寄存器

- AXI4 Stream(ST)->传输视频数据

用于高速的数据流通信

1.4 比较

AXI4 FULL和AXI4 LITE都是存储器映射类型的接口,都跟地址相关,需要指定地址1.5 AXI的优势

1. 生产力只需学习一个协议适用不同的需求

- 灵活性

FULL:指定一个地址可以支持最大256个数据的突发传输

LITE:不支持突发传输,但是占用的资源比较少,操作比较简单

ST:突发传输的长度没有限制

- 适应性强

很多IP都有AXI4的接口

1.6 AXI接口简介

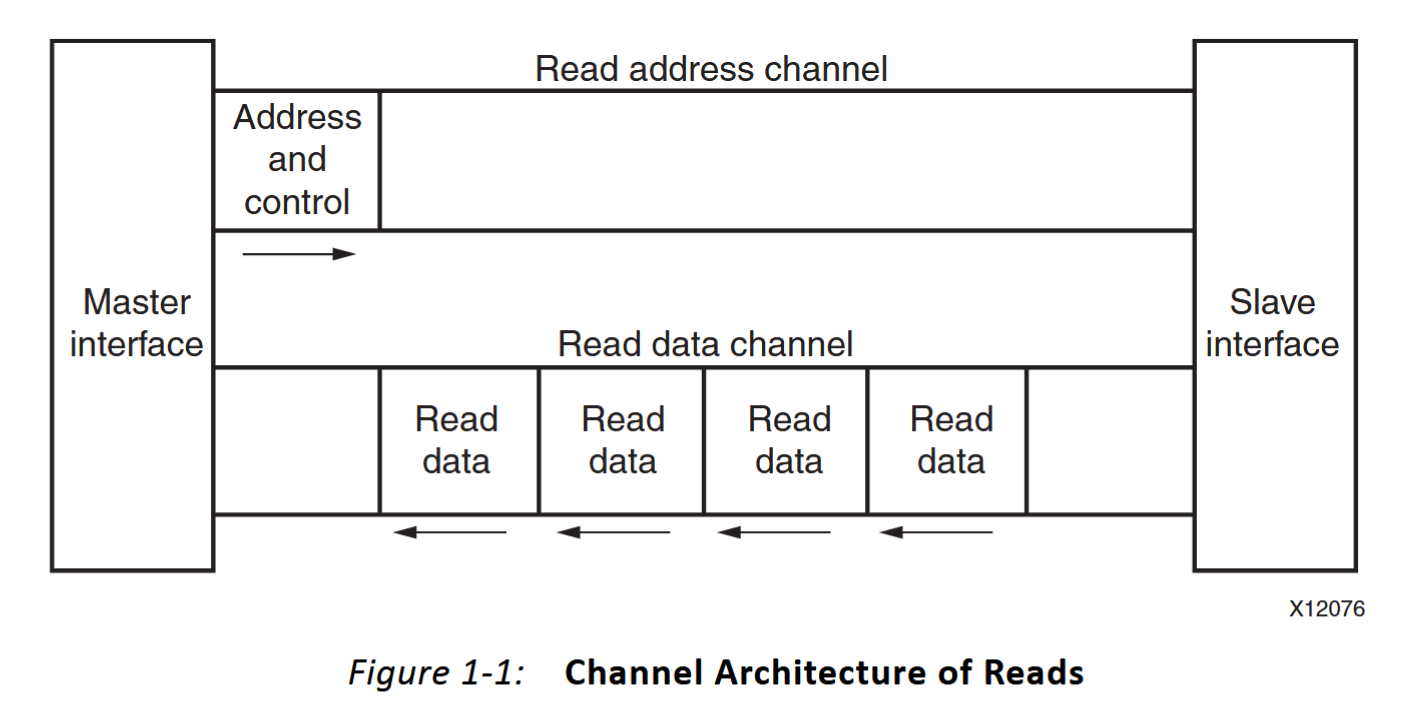

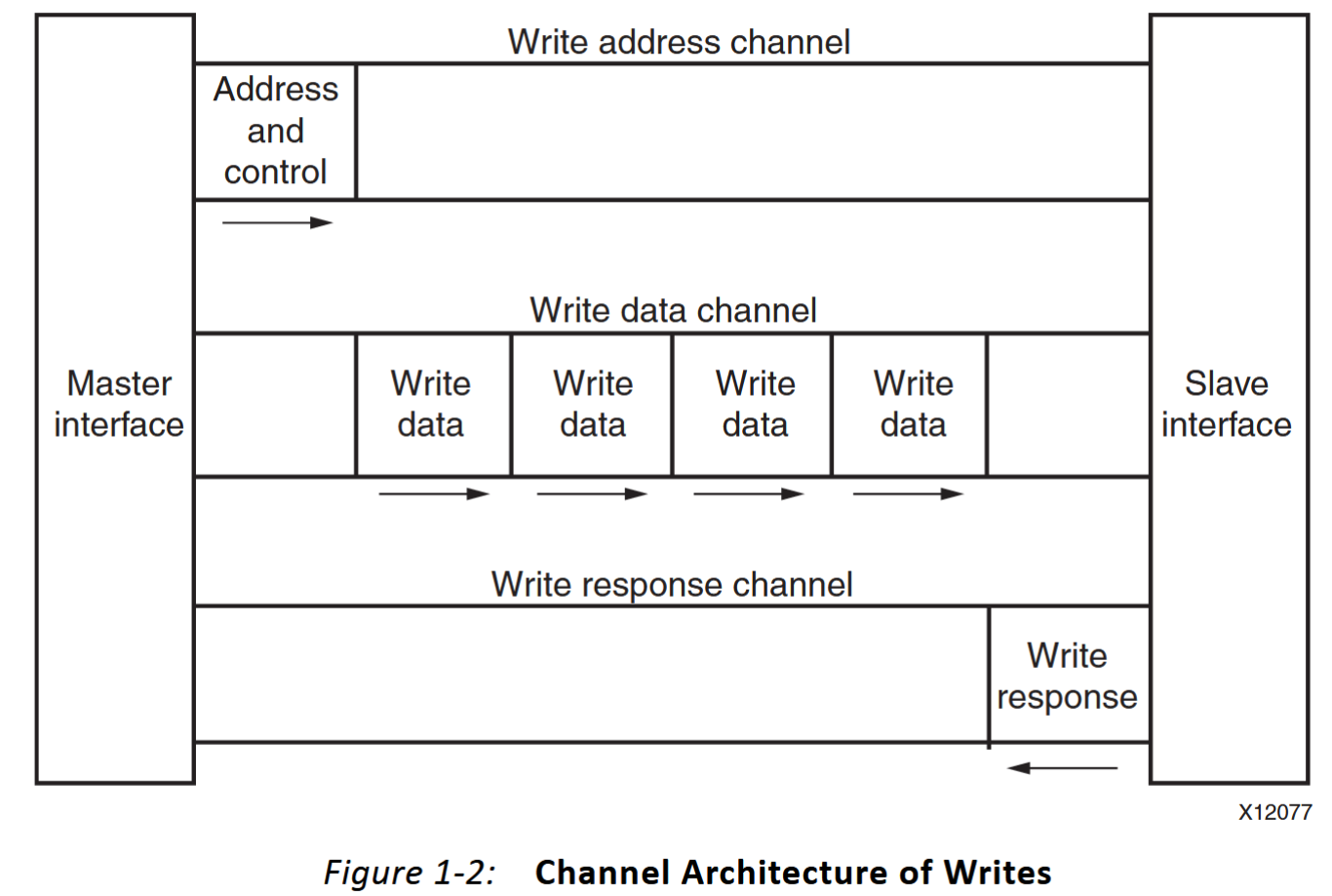

AXI4 full和AXI4 lite拥有五个不同的/独立的通道主机对从机的读操作:读地址 读数据

主机对从机的写操作:写地址 写数据 写响应通道

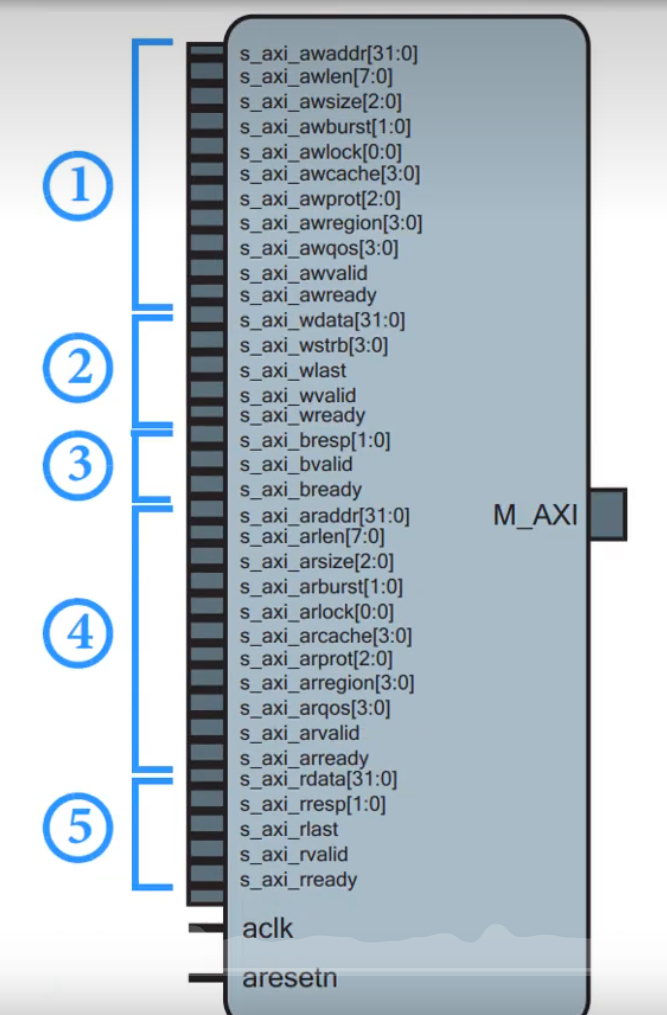

AXI从机接口展开

1.7 读写操作示意图

读操作的简单示意图

写操作的简单

MM:

Provides separate data and address connections for reads and writes, which allows simultaneous, bidirectional data transfer.

AXI FULL Requires a single address and then bursts up to 256 words of data.

ST:

The AXI4-Stream channel models the write data channel of AXI4.只有单一通道

Each AXI4-Stream acts as a single unidirectional channel with a handshaking data flow.

1.8 AXI DMA

AXI DMA实现ST和存储器映射的转换AXI Interconnect IP只能连接MM,不能连接Stream流!!!

AXI Stream Interconnect IP可以连接Stream流

IP with AXI4-Stream interfaces are generally connected to one another, to DMA IP, or to the AXI4-Stream Interconnect IP.

也就是说ST不能直接连接在AXI Interconnect IP上,需要进行DMA转换后连接AXI Interconnect IP

1.9 AXI通道定义

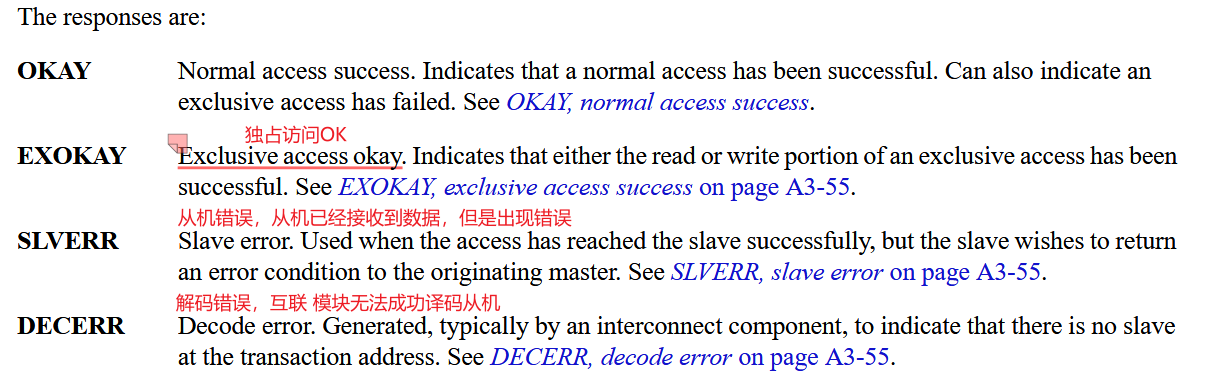

每个独立的通道都包含一组信息信号,VALID和READY提供双向握手机制The information source uses the VALID signal to show when valid address, data, or control information is available on the channel.

The destination uses the READY signal to show when **it can accept the information. **

Both the read data channel and the write data channel also include a LAST signal(source 发起)to indicate the transfer of the final data item in a transaction.

- There are separate write and read request channels.

The appropriate request channel(控制通道,或者说地址通道) carries all the required address and control information for a transaction.

- Read data channel

The read data channel carries both the read data and the read response information** from the Subordinate to the Manager** and includes:

• The data signal, RDATA which can be 8, 16, 32, 64, 128, 256, 512, or 1024 bits wide. The width is indicated using the DATA_WIDTH property.

• A read response signal indicating the completion status of the read transaction.

从读写响应的角度来看,读响应被包含在了读数据通道里面,而不是像写通道一样存在于独立的通道(五个通道之一)

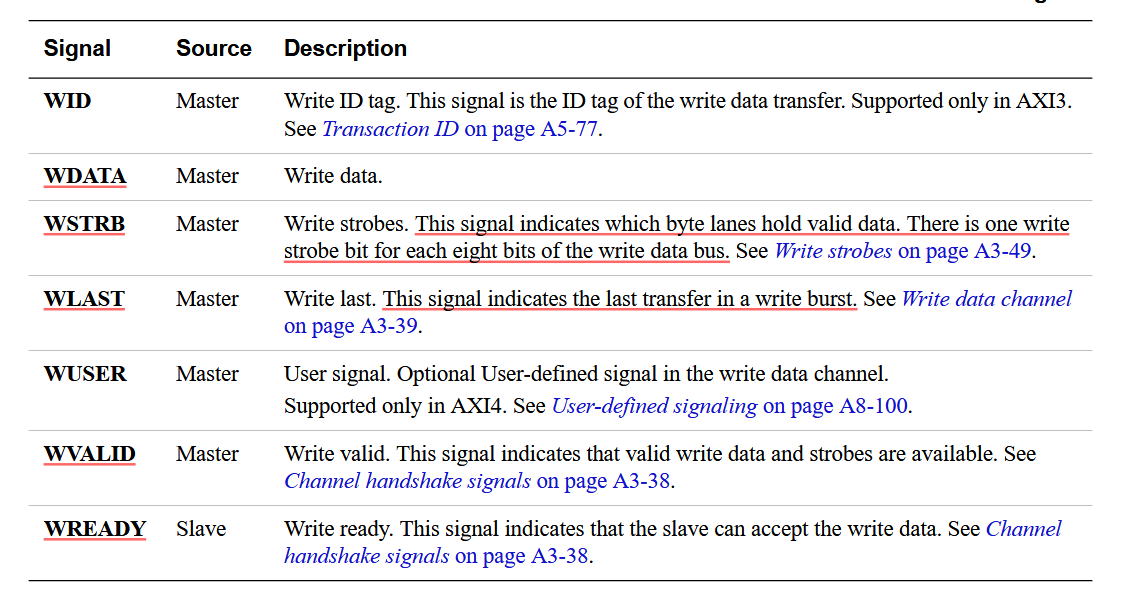

- Write data channel

The write data channel carries the write data from the Manager to the Subordinate and includes:

• The data signal, WDATA which can be 8, 16, 32, 64, 128, 256, 512, or 1024 bits wide. The width is indicated using the DATA_WIDTH property.

• A byte lane strobe signal for every eight data bits, indicating the bytes of the data that are valid.

WSTRB 一位控制每个字节的是否有效

Write data channel information is always treated as buffered, so that the Manager can perform write transactions without Subordinate acknowledgment of previous write transactions.

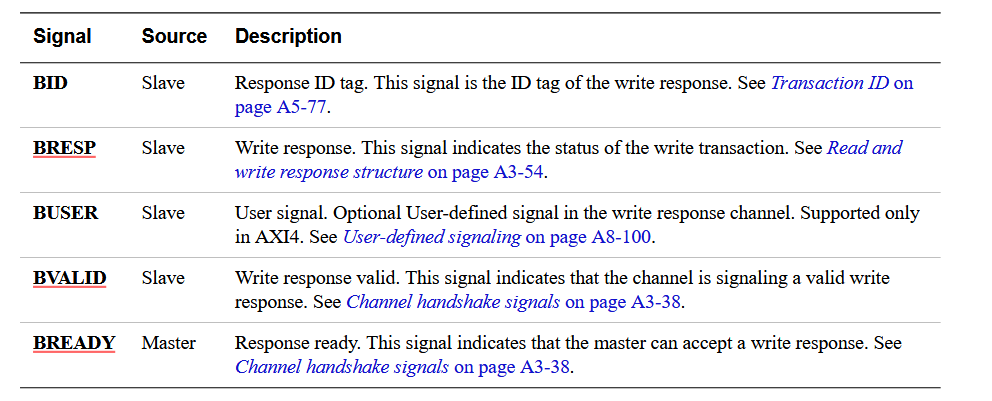

- Write response channel

A Subordinate uses the write response channel to respond to write transactions. All write transactions require completion signaling on the write response channel.

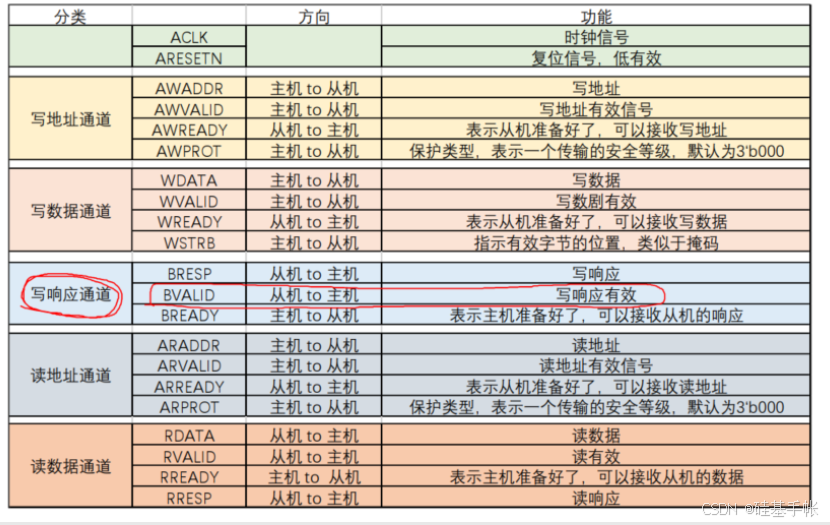

1.10 五个通道的信号

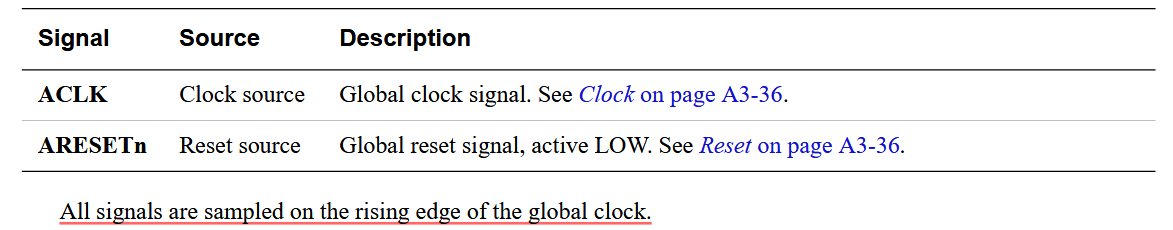

- 全局信号

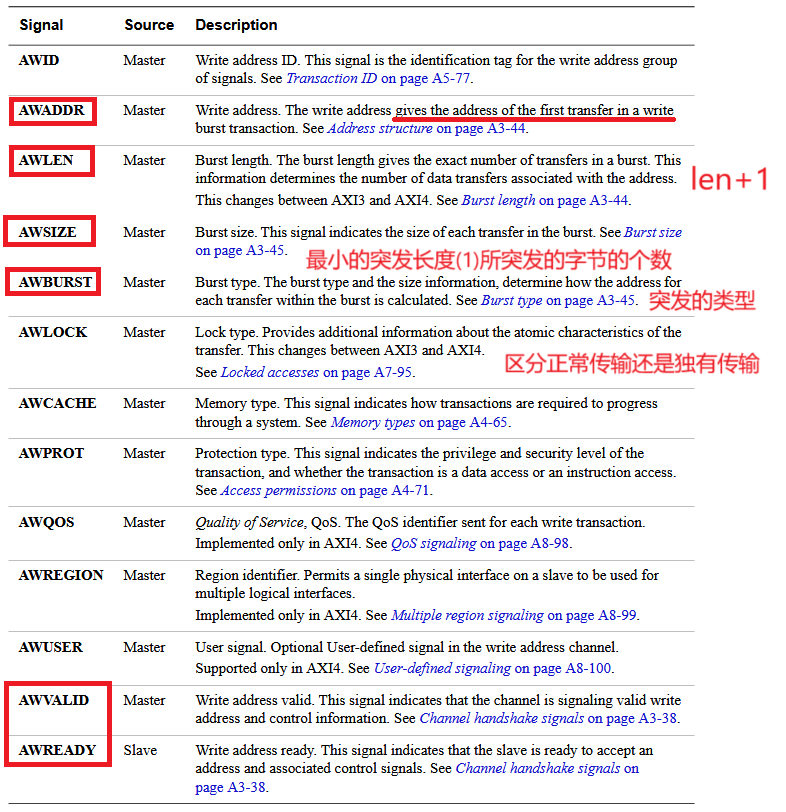

- 写地址通道信号

- 写数据通道

- 写响应通道

读地址通道(参考读写地址通道)

读数据通道(参考写数据通道)

详细内容看IHI0022的第二章

1.11 AXI4信号接口(IHI0022的第三章)

VALID和READY信号谁先拉高都行

主控端只有在驱动有效地址和控制信息时才能置位 AWVALID 信号。一旦置位,AWVALID 必须保持置位状态,直到从控端置位 AWREADY 信号后的上升沿时钟边沿。

数据在VALID拉高后不能变化,直到READY信号被采样后数据才能变化

1.12 信号的先后问题

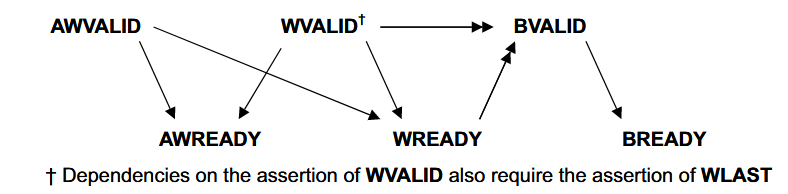

The AXI protocol requires the following relationships to be maintained:• a write response must always follow the last write transfer in the write transaction of which it is a part 写响应必须在写传输的后面

• read data must always follow the address to which the data relates 读数据在读地址后面

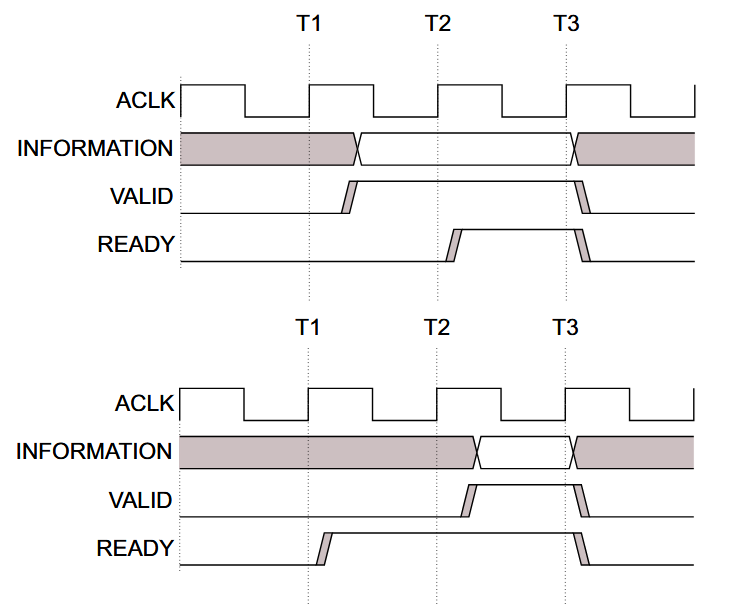

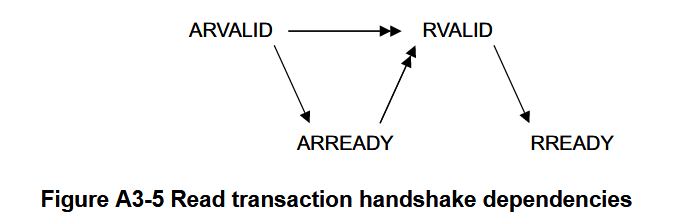

• channel handshakes must conform to the dependencies defined in Dependencies between channel handshake signals.

• 单箭头指向可以先于或后于箭头起点信号被置位的信号

• 双箭头指向必须在箭头起点信号置位后才能被置位的信号。

写的时候的响应 度的时候的数据 都比较靠后出现 可以理解为关键信号靠后出现

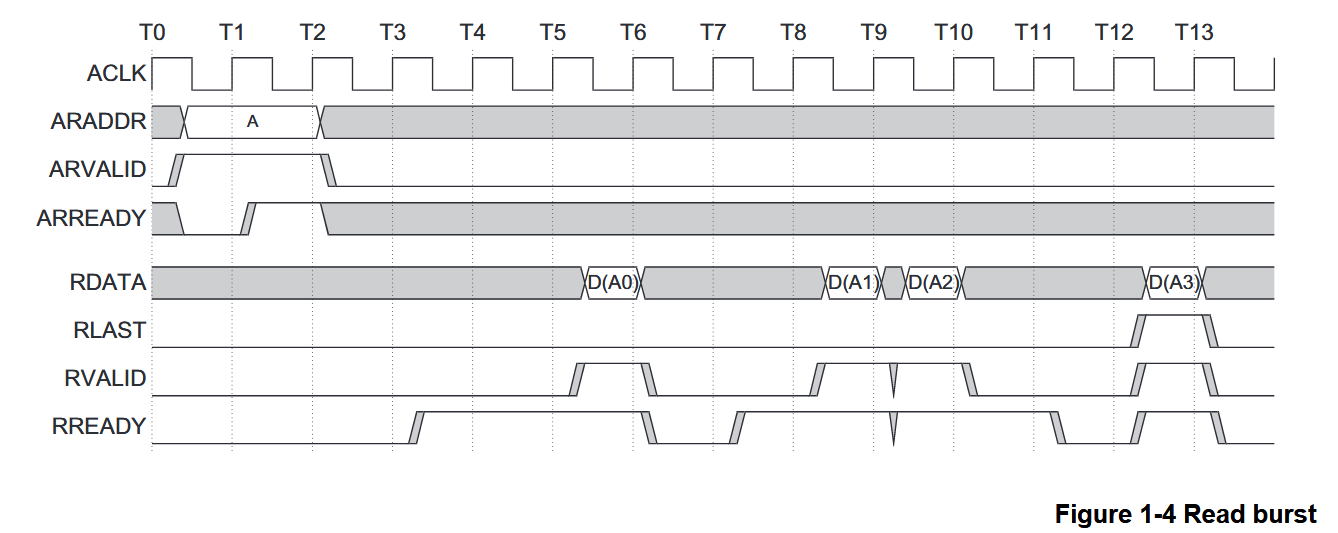

突发读

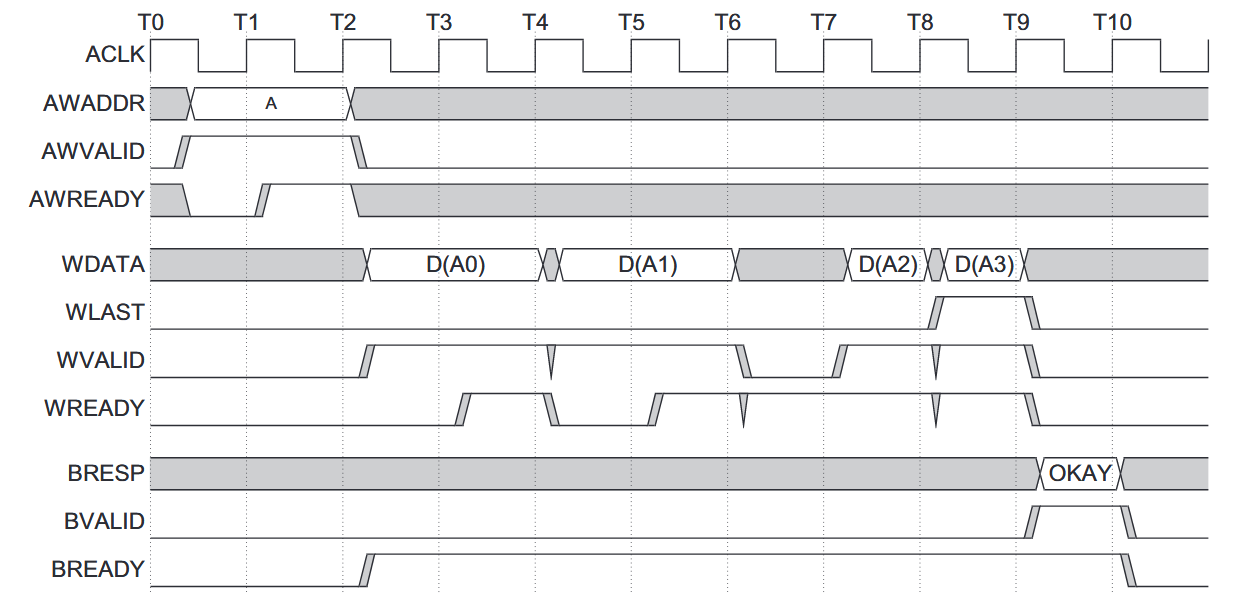

突发写

1.13 AXI4-Lite接口

AXI-GPIO AXI-Timer AXI-Uart不需要AXI4的完整功能,配置一些简单寄存器的读写的时候用Lite

AXI4-Lite supports a data bus width of 32-bit or 64-bit.

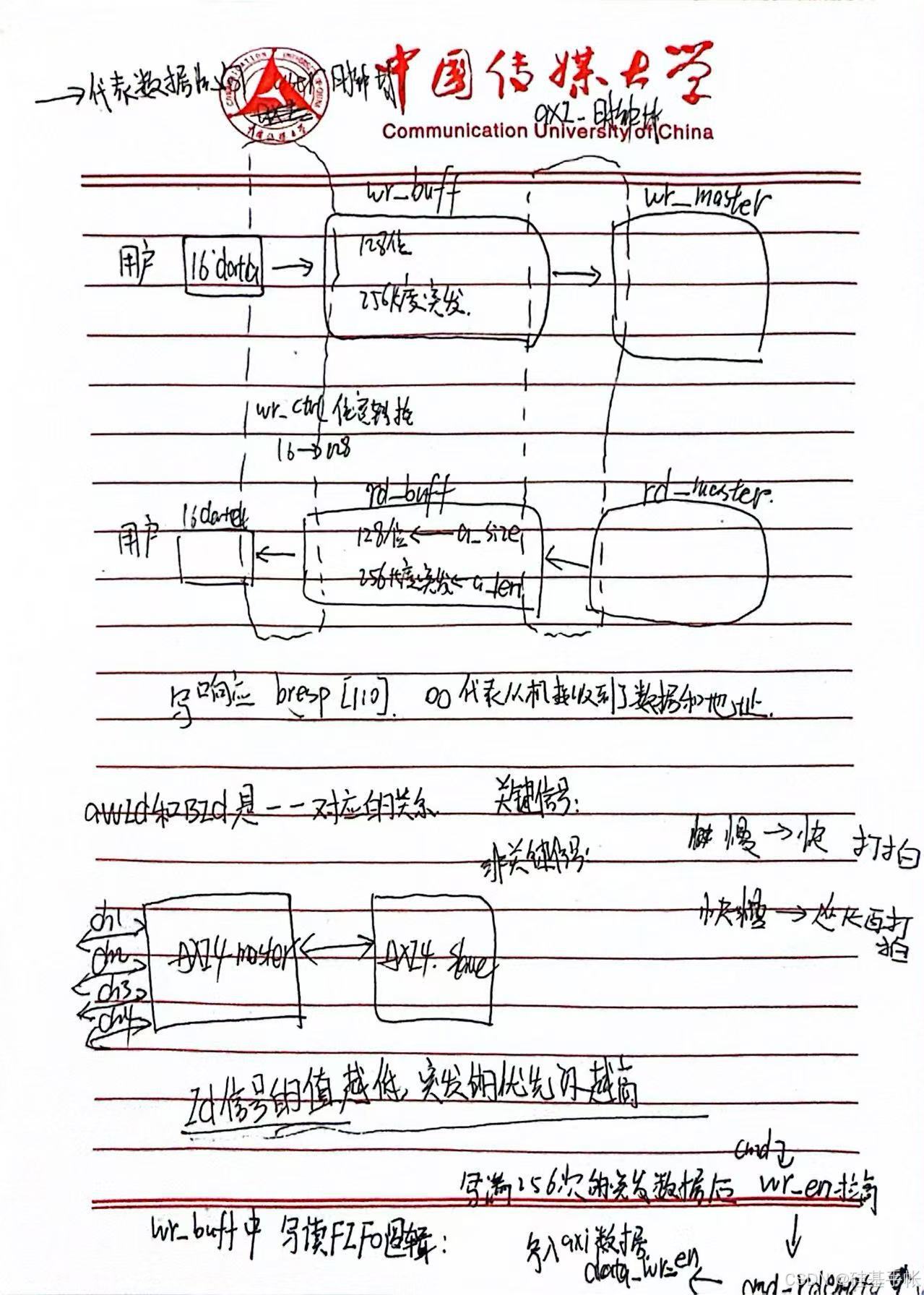

2. 手撕AXI DMA

2.1 整体流程

2.2 端口分类

2.3 写通道

```verilog module axi_wr_channel #( parameter USER_WR_DATA_WIDTH = 16 , parameter AXI_DATA_WIDTH = 128 , parameter AXI_ADDR_WIDTH = 32 )( input user_wr_clk , //用户端写时钟 input axi_clk , // AXI4端时钟 input reset ,input ddr_init_done ,

/*-------------用户写端口信号------------------------*/

input user_wr_mode , //模式0和模式1

input user_wr_en ,

input user_wr_last ,

input [USER_WR_DATA_WIDTH-1:0] user_wr_data ,

input [AXI_ADDR_WIDTH-1:0] user_wr_addr ,

input [12:0] user_wr_length ,

input [AXI_ADDR_WIDTH-1:0] user_wr_base_addr , //一定要被4096整除

input [AXI_ADDR_WIDTH-1:0] user_wr_end_addr , //一定要被4096整除

/*-------------AXI写通道端口信号---------------------*/

output m_axi_awvalid ,

input m_axi_awready ,

output [AXI_ADDR_WIDTH-1:0] m_axi_awaddr ,

output [3:0] m_axi_awid ,

output [7:0] m_axi_awlen ,

output [1:0] m_axi_awburst ,

output [2:0] m_axi_awsize ,

output [2:0] m_axi_awprot ,

output [3:0] m_axi_awqos ,

output m_axi_awlock ,

output [3:0] m_axi_awcache ,

output m_axi_wvalid ,

input m_axi_wready ,

output [AXI_DATA_WIDTH-1:0] m_axi_wdata ,

output [AXI_DATA_WIDTH/8-1:0] m_axi_wstrb ,

output m_axi_wlast ,

input [3:0] m_axi_bid ,

input [1:0] m_axi_bresp ,

input m_axi_bvalid ,

output m_axi_bready ,

/*-------------FIFO错误信号--------------------------*/

output wr_cmd_fifo_err ,

output wr_data_fifo_err

);

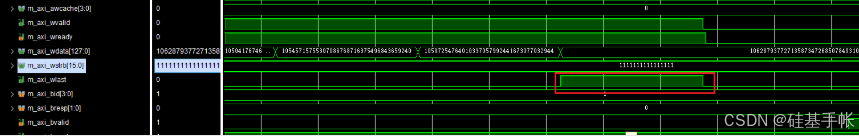

重要信号

写地址通道

m_axi_awvalid

m_axi_awready

m_axi_awaddr

m_axi_awid和bid一一对应 方便通道串并转换

在这里插入图片描述

m_axi_awlen突发的长度

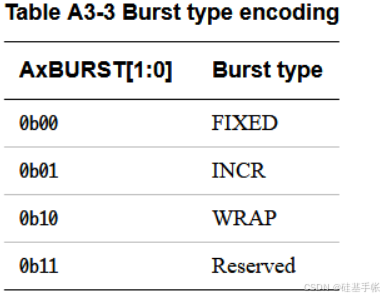

m_axi_awburst

m_axi_awsize一次突发的数据位宽

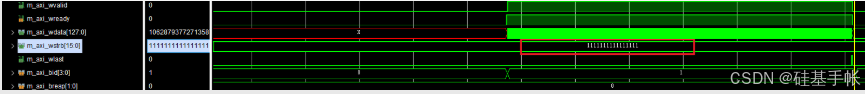

写数据通道

m_axi_wvalid

m_axi_wready

m_axi_wdata

m_axi_wstrb字节掩码,比如说Ax_SIZE = 4,突发的数据位宽就是2^4个字节,也就是突发2^4*8=2^7=128位宽

掩码就是如果想要数据全有效那么就让[15:0]m_axi_wstrb = 16'b1111_1111_111_1111;

m_axi_wlast写最后一次数据

没那么重要的信号

m_axi_awprot

m_axi_awqos

m_axi_awlock

m_axi_awcache

<font style="color:rgb(0,0,0);">上面的信号,方向为主机到从机,一般用于 ZYNQ PS 和 PL 交互的时候,PL 端操作 PS 的内存。</font>

8089

8089

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?