Verilog advanced tutorial

转换函数

| 调用系统任务 | 任务描述 |

|---|---|

| int_val = $rtoi( real_val ) ; | 实数 real_val 转换为整数 int_val 例如 3.14 -> 3 |

| real_val = $itor( int_val ) ; | 整数 int_vla 转换为实数 real_val 例如 3 -> 3.0 |

| vec_val = $realtobits( real_val ) ; | 实数转换为多位宽的寄存器向量 寄存器内按照 IEEE-754 标准存储双精度浮点型数据 |

| real_val = $bitstoreal( vec_val ) ; | 多位宽的寄存器向量转换为实数 |

real 型变量的产生或转换过程,都应该遵循 IEEE Std 754-1985 [B1] 标准。

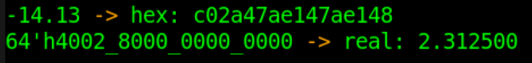

利用 $realtobits 与 $bitstoreal 对数据进行转换:

- 实例

//real, bits*

reg [63:0] num_bits ;

initial begin

num_bits = 64'h4002_8000_0000_0000 ;

$display("-14.13 -> hex: %h", $realtobits(-13.14));

$display("64'h4002_8000_0000_0000 -> real: %f", $bitstoreal(num_bits));

end

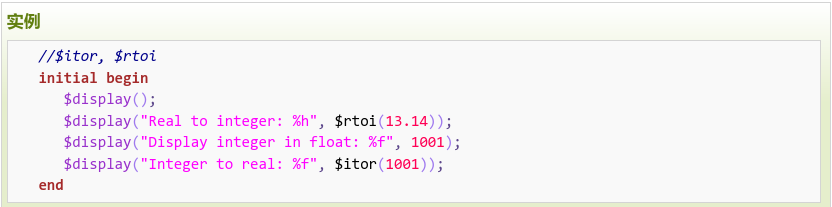

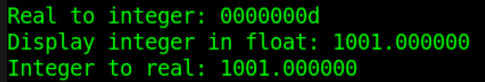

利用 $itor 与 $rtoi 对数据进行格式转换:

由以下仿真 log 可知,$rtoi 做实数(13.14)向整数(4’hd)的转换时,只截了取整数部分。$itor 做整数 (1001) 向实数(1001.000000)的转换时,似乎没有什么变化。

其实,$rtoi 与 $itor 的功能是改变变量的存储方式。

例如 14 以整数型变量储存时,表示方法为 32’h1110,而如果以实数型变量存储,则表示方法为 64h402c_0000_0000_0000。

Display system tasks

| System tasks | Description |

|---|---|

| $display | To display strings, variables, and expressions immediately in the active region.立即在活动区域中显示字符串、变量和表达式。 |

| $monitor |

本文介绍了Verilog中的高级概念,包括实数到整数和整数到实数的转换函数($rtoi和$itor),以及利用$realtobits和$bitstoreal进行数据格式转换。同时详细讲解了显示系统任务如$display、$monitor等的使用及其功能区别。

本文介绍了Verilog中的高级概念,包括实数到整数和整数到实数的转换函数($rtoi和$itor),以及利用$realtobits和$bitstoreal进行数据格式转换。同时详细讲解了显示系统任务如$display、$monitor等的使用及其功能区别。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

2786

2786

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?