Xilinx的7系列FPGA的功能相当强大,本文介绍一下它的部分IO逻辑资源。

ILOGIC

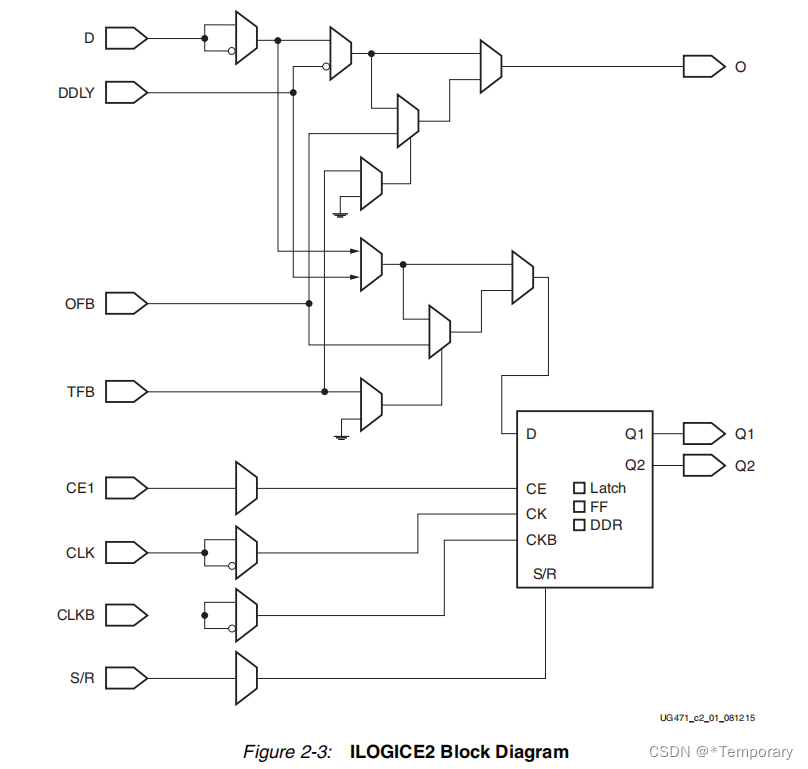

对于A7的器件,输入IO逻辑有ILOGIC2和ILOGIC3两种,唯一区别就是ILOGIC3拥有零保持延时单元,这东西我也没用过,所以就不展开讲了,下面是ILOGIC的输入框图:

ILOGIC支持一下几个操作:

- 边沿触发的D触发器;

- IDDR模式(这个后面重点讲);

- 敏感电平锁存器;

- 异步电路/逻辑组合;

Input DDR Overview (IDDR)

调用方法:时钟原语IDDR。

支持模式:

-

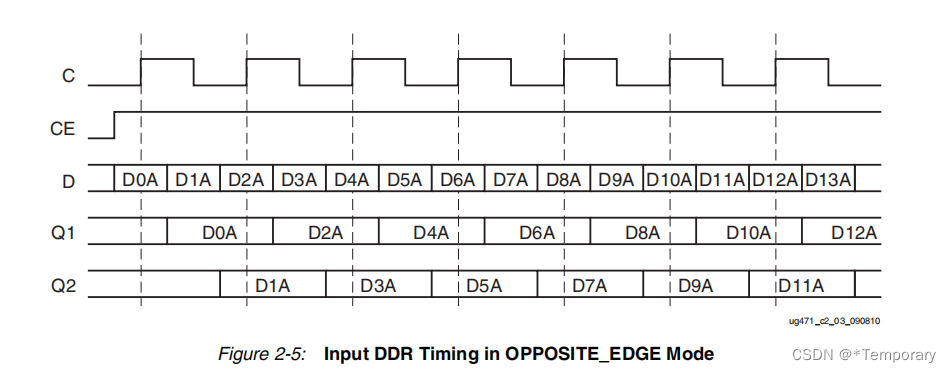

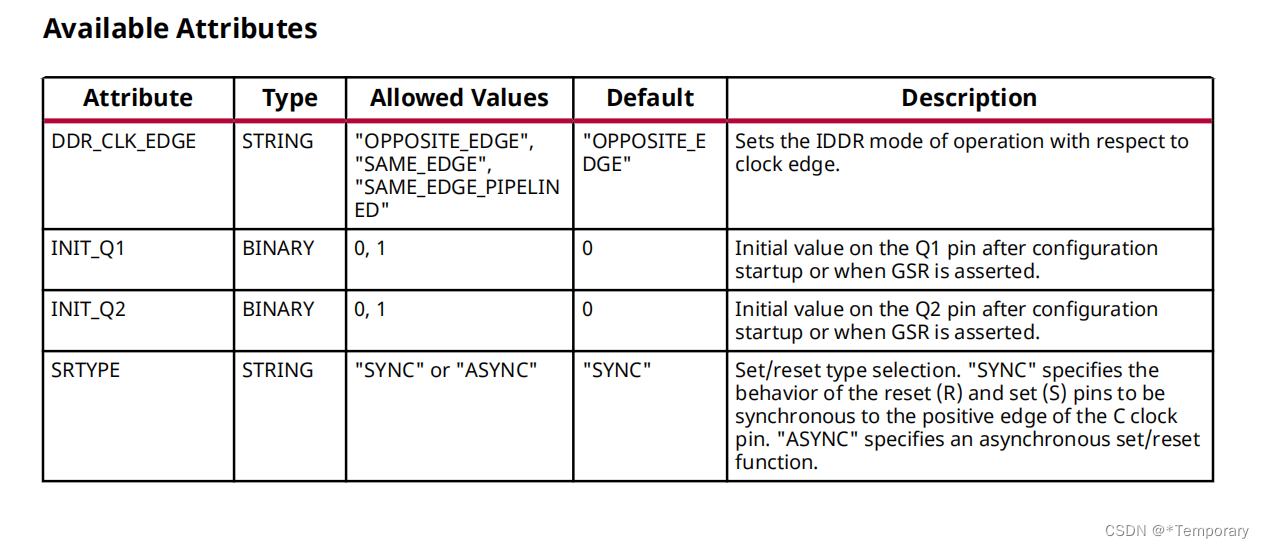

OPPOSITE_EDGE mode

这个模式就是传统的输入DDR的解决方案,数据输入在时钟上升沿输出给Q1、在时钟下降沿输出给Q2,以此再到到FPGA的内部逻辑块。(注:数据输出是有延迟的,所以才呈现为下图的样子。)

-

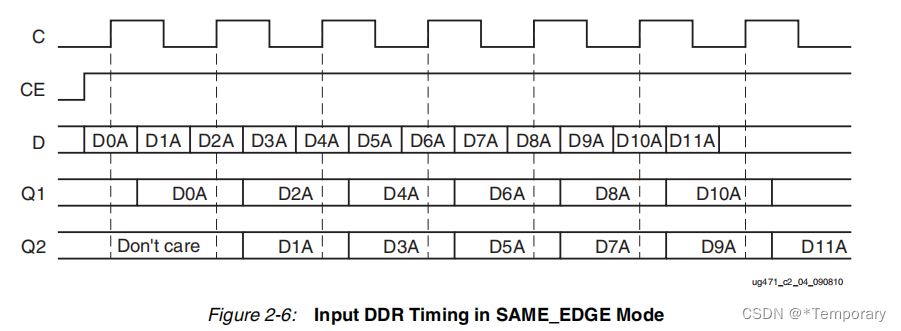

SAME_EDGE mode

该模式允许设计者将时钟下降沿的数据传输到ILOGIC区块的上升沿区域,以此节约时钟资源并提高性能。这个模式下,同样会在时钟的上升和下降沿将数据采集进来,但是Q1、Q2会在下一个时钟的上升沿同时输出,这是和上一个模式的区别,并且第一个时钟周期的的Q2的数据是不可取的。

-

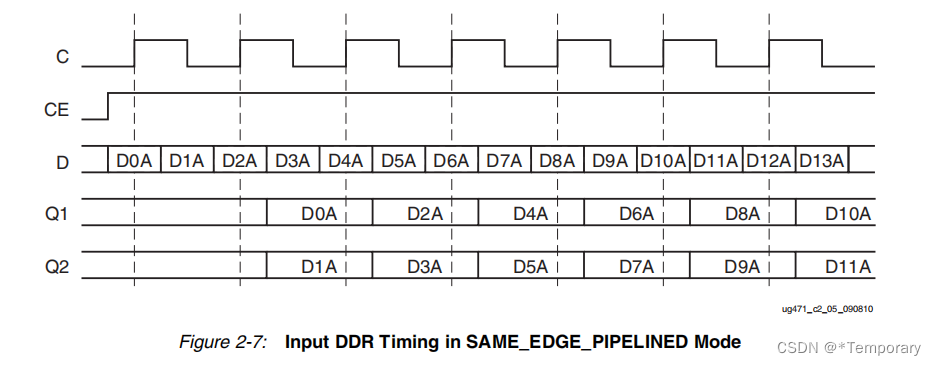

SAME_EDGE_PIPELINED mode

同上,这个模式也是在时钟的上升沿同时将Q1、Q2的数据输出,不同的是,这个模式的数据对将不会差一个时钟周期。但是我们看到虽然数据对是成双成对的出来了,但是我们需要手动添加一个周期的时钟延迟,也就是俗称的“打拍”。

参数来源:

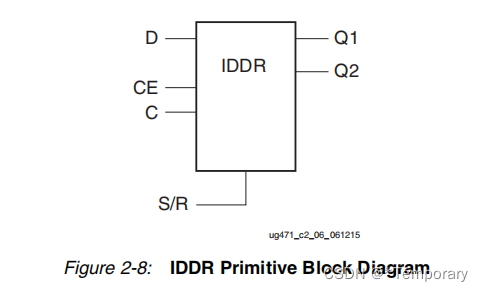

4. 整体框图

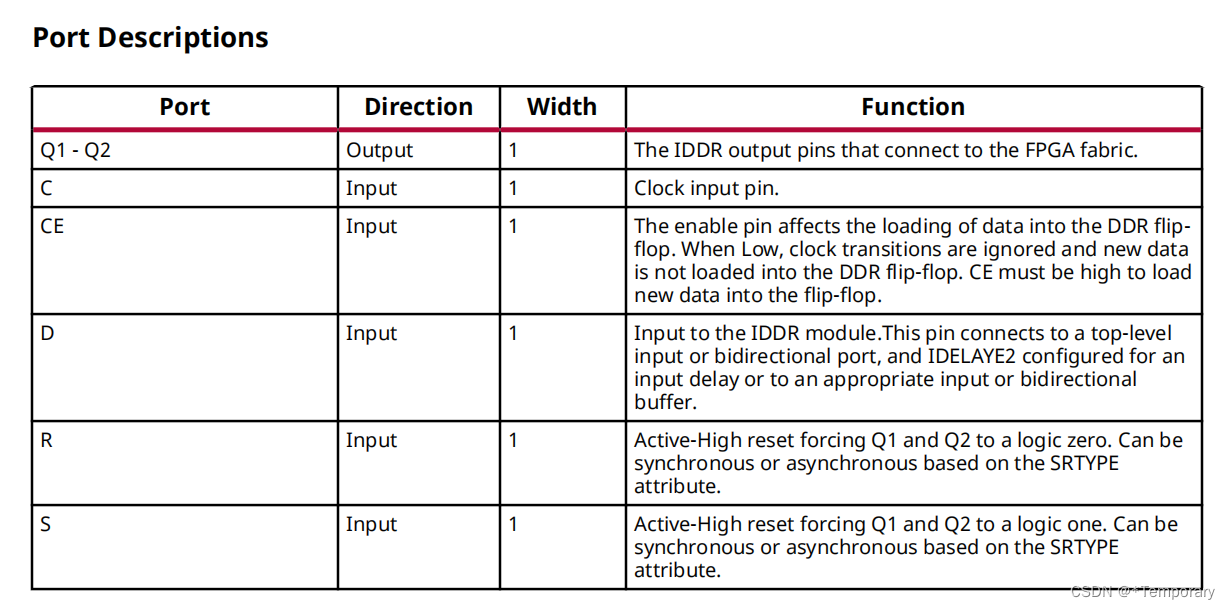

图中的S/R表示置复位信号,高电平有效,不可同时设置,所以在调用原语的时候要分开来写。

-

输入端口

-

输入参数

-

设计模板(注:以下模板来源于Xilinx官网提供的用户设计参考,本人只负责摘录,不负责解释)

//****************************************************************

// Verilog版本

//****************************************************************

// IDDR: Input Double Data Rate Input Register with Set, Reset

// and Clock Enable.

// 7 Series

// Xilinx HDL Language Template, version 2022.2

IDDR #(

.DDR_CLK_EDGE("OPPOSITE_EDGE"), // "OPPOSITE_EDGE", "SAME_EDGE"

// or "SAME_EDGE_PIPELINED"

.INIT_Q1(1'b0), // Initial value of Q1: 1'b0 or 1'b1

.INIT_Q2(1'b0), // Initial value of Q2: 1'b0 or 1'b1

.SRTYPE("SYNC") // Set/Reset type: "SYNC" or "ASYNC"

) IDDR_inst (

.Q1(Q1), // 1-bit output for positive edge of clock

.Q2(Q2), // 1-bit output for negative edge of clock

.C(C), // 1-bit clock input

.CE(CE), // 1-bit clock enable input

.D(D), // 1-bit DDR data input

.R(R), // 1-bit reset

.S(S) // 1-bit set

);

// End of IDDR_inst instantiation

//****************************************************************

// Verilog版本

//****************************************************************

Library UNISIM;

use UNISIM.vcomponents.all;

-- IDDR: Double Data Rate Input Register with Set, Reset

-- and Clock Enable.

-- 7 Series

-- Xilinx HDL Language Template, version 2022.2

IDDR_inst : IDDR

generic map (

DDR_CLK_EDGE => "OPPOSITE_EDGE", -- "OPPOSITE_EDGE", "SAME_EDGE"

-- or "SAME_EDGE_PIPELINED"

INIT_Q1 => '0', -- Initial value of Q1: '0' or '1'

INIT_Q2 => '0', -- Initial value of Q2: '0' or '1'

SRTYPE => "SYNC") -- Set/Reset type: "SYNC" or "ASYNC"

port map (

Q1 => Q1, -- 1-bit output for positive edge of clock

Q2 => Q2, -- 1-bit output for negative edge of clock

C => C, -- 1-bit clock input

CE => CE, -- 1-bit clock enable input

D => D, -- 1-bit DDR data input

R => R, -- 1-bit reset

S => S -- 1-bit set

);

-- End of IDDR_inst instantiation

- 仿真验证

对上面的IDDR进行仿真,代码如下:

reg clk;

initial clk = 1'b0;

always #(`CLK_PERIOD / 2) clk = ~clk;

reg rst;

initial rst = 1'b0;

reg data_in;

initial begin

data_in = 1'b1;

#100

data_in = ~data_in;

...

data_in = ~data_in;

end

wire q1;

wire q2;

IDDR #(

.DDR_CLK_EDGE("OPPOSITE_EDGE"), // "OPPOSITE_EDGE", "SAME_EDGE"

// or "SAME_EDGE_PIPELINED"

.INIT_Q1(1'b0), // Initial value of Q1: 1'b0 or 1'b1

.INIT_Q2(1'b0), // Initial value of Q2: 1'b0 or 1'b1

.SRTYPE("SYNC") // Set/Reset type: "SYNC" or "ASYNC"

) IDDR_inst (

.Q1(q1), // 1-bit output for positive edge of clock

.Q2(q2), // 1-bit output for negative edge of clock

.C(clk), // 1-bit clock input

.CE(1'b1), // 1-bit clock enable input

.D(data_in), // 1-bit DDR data input

.R(rst), // 1-bit reset

.S() // 1-bit set

);

仿真结果如下所示:

在前面几个初始周期中数据保持不变,IDDR还处于复位状态,这个我在手册上没有找到为什么,可能是这个原语调用的时候确实需要等待几个时钟周期,大家注意就好,后面的和我们所介绍的就一样了。其他几种模式下的调试大家可以自己去尝试,这里就不多介绍了。

结语

IDDR,就是在使用FPGA处理DDR信号的时候,提供的一种便利手段,同时也节约了FPGA的时钟和逻辑资源。

1561

1561

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?