写这篇文章的本意不是为了探讨AD9767怎么使用,因为9767的控制实在是太简单了,准备好数据直接输出即可,和网上大多数的并行DA输出基本上一模一样,更麻烦的反而是硬件方面。发文的原因是最近一位很细心的朋友发现AD9767的输出有些问题,本人调试觉得也很有意思,所以发出来分享一下。

本文还是意思一下先讲解9767的使用,下一篇文章着重分析一下9767设计时的一个软件bug。

硬件条件

FPGA:XC7A35T

DA芯片:AD9767

软件设计

DDS设计基本原理

此次设计所使用的DA芯片为ADI公司的AD9767,主要参数包括10-14位可调位数输出,最高125M的输出频率,单片拥有两个并行通道输出,每通道最多由14位并行数据控制输出。下图所示为AD9767的框图:

介绍完DA芯片,FPGA就不多介绍了,接下来介绍基本原理。

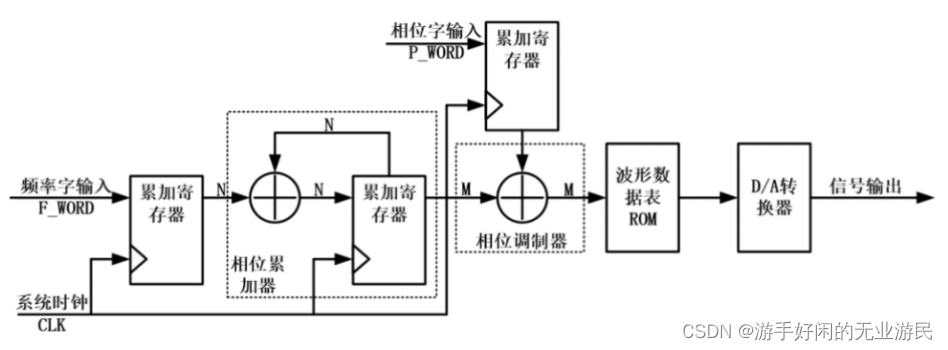

我们知道9767是一个14位的并行DA芯片,所以本次设计将会通过在ROM中存储需要输出的波形(正弦波、方波、三角波)数据,然后FPGA输出对应控制ROM输出的地址信号,再将ROM的输出数据提供给9767的方法,达到DDS输出的效果。本设计给AD9767提供的时钟源固定为50MHz(系统主频),每一次时钟的上升沿相位累加器都会对频率输入字(FWORD)进行累加,设累加器的位数为N,那么计数范围从0-(2的N次方-1),也就是说对于我们输出的波形,分辨率为1/2的N次方。每一次累加的值(FWORD)实际上就是步长,所以最终得到Fout的频率为FWORD × (1/2N) × 50MHz。除开频率控制字之外,还附加了相位控制字,这一点很好理解,只需要在相位累加器的输出结果基础上在加上对应的相偏数据,就可以得到相位偏移的波形了。以下是DDS波形发生的整体框图。如果输出的波形不是方波,可以在最后的信号输出可以再加一个低通滤波器滤除高频信号,使得输出曲线更加平滑。

上图中之所以在字的输入端需要加入寄存器是为了寄存数据以防止在进行数据转换的过程中外界数据突然改变。OK,了解完设计原理后,接下来就是代码设计的思路了。根据上述的计算公式,那么在已知输出频率以及输入的时钟频率的情况下,我们可以得到FWORD的计算公式为:

根据奈奎斯特采样定律,每一个周期至少需要有两个点数,所以FWORD的设置应该小于2N-1才行。

此外,值得注意的是,频率累加器的位数为32位,如果将这个32位全部给到ROM中,问题倒是不大,但是比较吃资源,所以我们为了节省资源,采用12位地址的ROM,只需要将32位累加器的高12位输入到ROM中即可。这样子的结果就是累加器的低20变化时,ROM的地址线是不变的,只有经过220计数后才会变1,相当于是给9767的时钟频率进行了一个220的分频。不理解的朋友没关系,因为在最后我们计算的时候其实是不用管这个20的,因为我们需要的结果就是232的计数后能够让一个周期走完,而内部是如何运作的,完全可以当成一个黑匣子来看。

好了,介绍完理论部分之后就可以开始写代码了,代码部分其实相当简单,只需要每个时钟周期都给频率字计数器+FWORD的值即可,频率字计数器是一个32位的寄存器,我们将它的高12位输入给ROM作为数据寻址的地址,再将ROM的14位数据输出给AD9767即可,代码较为简单,将14位数据准备好通给AD9767之后,DA芯片就会随着时钟信号,将对应的电流输出,经过滤波电路以及运放后即可得到电压。需要程序文件的下篇文章会一起附上。

基于FPGA的简易DDS信号发生器的设计(二)

2万+

2万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?