本文内容整理自西安交通大学软件学院李晨老师的课件,仅供学习使用,请勿转载

计算机组成原理系列笔记汇总:计算机组成原理笔记及思维导图汇总附复习建议_Qlz的博客-CSDN博客

文章目录

文章目录

- 文章目录

- 本章思维导图

- External Devices

- I/O Modules

- Programmed I/O

- Interrupt Driven I/O

- Direct Memory Access

- I/O Channels

- External Interface

- Key points

- Vocabulary

本章思维导图

External Devices

I/O Speed: bytes transferred per second(from mouse to display: 10-to-million)

Disk drive

- Contain two types of electronics

- One type for exchanging data, control and status signals with an I/O module

- The other for controlling the disk read/write mechanism

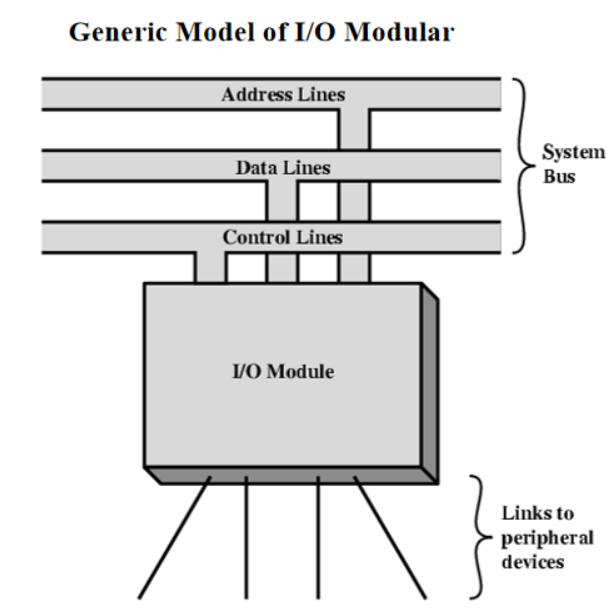

I/O Modules

Function of I/O Module

- Control & Timing

- CPU ~ I/O Communication

- Device ~I/O Communication

- Memory ~ I/O communication

- Data Buffering

- Error Detection

I/O Steps

- CPU checks I/O module and device status

- I/O module returns status

- If ready, CPU requests data transfer

- I/O module gets data from device

- I/O module transfers data to CPU

- Programmed-I/O

- Interrupt-Driven I/O

- DMA/Channel

I/O Communication

- Command decoding:

- Read sector, Seek track, Scan ID

- Which blocks can be read or written.

- Data exchange

- External data I/O module buffer through local bus

- I/O module buffer CPU/memory through system bus

- Status reporting

- Busy, ready, error, etc

- Address recognition

- Recognize each peripheral

Data Buffering

- Adapt peripherals to CPU or main memory in their velocities

- CPU/DRAM ← → \leftarrow \rightarrow ←→ I/O buffer

- I/O buffer ← → \leftarrow \rightarrow ←→ peripherals

Error Detection

- An I/O modular is often responsible for error detection and reporting errors to CPU

- One class of errors is hardware failure

- Mechanical or electrical

- E.g.: paper jam, bad disk track

- Another class of errors is transmitting errors

- Bit errors

- Data losses

I/O Module Decisions

- Support multiple or single device

- Hide or reveal device properties to CPU

- Control device functions or leave for CPU

- Also O/S decisions

- e.g. Unix treats everything it can as a file

Input Output Modes

- Programmed

- Interrupt driven

- Direct Memory Access (DMA)

- I/O Channel

- I/O processor

Programmed I/O

-

With programmed I/O, data are exchanged between the CPU and I/O modular

-

CPU has direct control over I/O in a program

- Sensing status

- Read/write commands

- Transferring data

-

CPU waits for I/O module to complete operation when it issues an I/O command

-

Wastes CPU time

process

- CPU encounters an I/O instruction

- CPU executes it, by sending a command to I/O modular, and waits for the I/O modular ready

- I/O modular performs the command and then set the appropriate bit in the I/O status register

- CPU periodically checks the status bit until it find the operation completed

I/O Commands

- CPU issues address

- Identifies module & device ( if >1 per module)

- CPU issues commands: 4 commands

- Control - telling module what to do

- e.g. rewind, open disk drive, etc

- Test - check status

- e.g. power? Error?

- Read/Write

- Module transfers data via buffer from/to device

- Control - telling module what to do

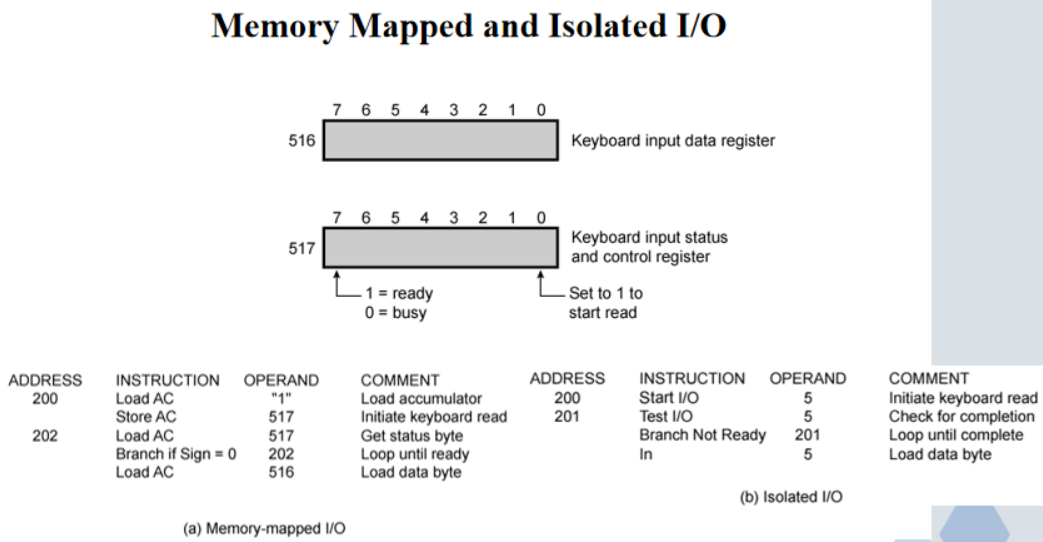

Addressing I/O Devices

- Under programmed I/O data transfer is very like memory access (CPU viewpoint)

- Each device given unique identifier

- CPU commands contain identifier (address)

I/O Mapping

不太明白

- Memory mapped I/O

- Devices and memory share an address space

- 0xxxxxx, 1xxxxxx

- I/O looks just like memory read/write

- No special commands for I/O

- Large selection of devices available

- Devices and memory share an address space

- Isolated I/O

- Separate address spaces

- Need I/O or memory select lines

- Special commands for I/O

- Limited set

Summary

- Advantage:

- Simple: processor is totally in control and does all

- Disadvantage:

- Polling overhead can consume a lot of CPU time

- Solution: use exception mechanism to help I/O. Interrupt program when I/O ready, return when done with data transfer

Interrupt Driven I/O

- Overcomes CPU waiting

- No repeated CPU checking of device

- I/O module interrupts when ready

Interrupt Driven I/O Basic Operation

- CPU issues read command, and then do other things

- I/O module gets data from peripheral whilst CPU does other work

- I/O module interrupts CPU

- CPU requests data

- I/O module transfers data through bus

- At last, CPU recover previous work

CPU Viewpoint

- Issue read command

- Do other work

- Check for interrupt at end of each instruction cycle

- If interrupted:-

- Save context (registers)

- Process interrupt

- Fetch data & store

- Restore context

- Continue previous work

I/O Module Viewpoint

- Receive a READ command from CPU

- Detect the state of the peripheral

- Read data from the peripheral, put it into registers

- Signal an interrupt to CPU

- Wait until its data are requested by CPU

- Place the data on the data bus

Design Issues

How do you identify the module issuing the interrupt

- Multiple interrupt lines

- Different line for each module, Limits number of devices

- Software poll

- CPU asks each module in turn through interrupt-service subroutine

- Command + address of I/O module

- Read addressable status register contained in each I/O module

- CPU branches to the device service routine

- Slow (time consuming)

- CPU asks each module in turn through interrupt-service subroutine

- Daisy chain or Hardware poll Bus

- All I/O modules share a common interrupt request line

- Once CPU senses an interrupt, Interrupt Acknowledge sent down a chain

- Module responsible places vector (address, id) on bus

- CPU uses vector to point to an appropriate device-service routine

- Referred to as vectored interrupt

- Arbitration (vectored)

- Module must claim the bus before it can raise interrupt

- CPU detects the interrupt, respond it through interrupt acknowledge line.

- I/O module places vector on the data bus

- e.g. PCI & SCSI

How do you deal with multiple interrupts

- With multiple lines, Each interrupt line has a priority

- Higher priority lines can interrupt lower priority lines

- With software polling, the order in which modules are polled determines their priority

- With daisy, the order of modules on the daisy determines their priority

Direct Memory Access

Drawbacks of programmed and interrupt-driven I/O

- Programmed I/O needs to occupy all CPU time

- Interrupt driven I/O still requires active CPU intervention, though more efficient CPU usage than Programmed I/O (transfer rate is lower)

- In both modes, data transfer must traverse CPU

- Transfer rate is limited

- CPU is tied up

- When large volumes of data are transferred, DMA is a more efficient technique

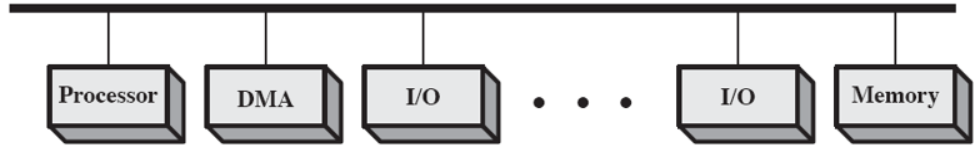

What is DMA

- External to the CPU

- Additional Module (hardware) on bus

- DMA controller takes over from CPU for I/O

- Transfer blocks of data to or from memory without CPU intervention

- In fact, DMA is also an I/O module

- Act as a master on the bus

- Memory system acts like slave

- Manage byte-word conversion

- Priority: DMA > CPU

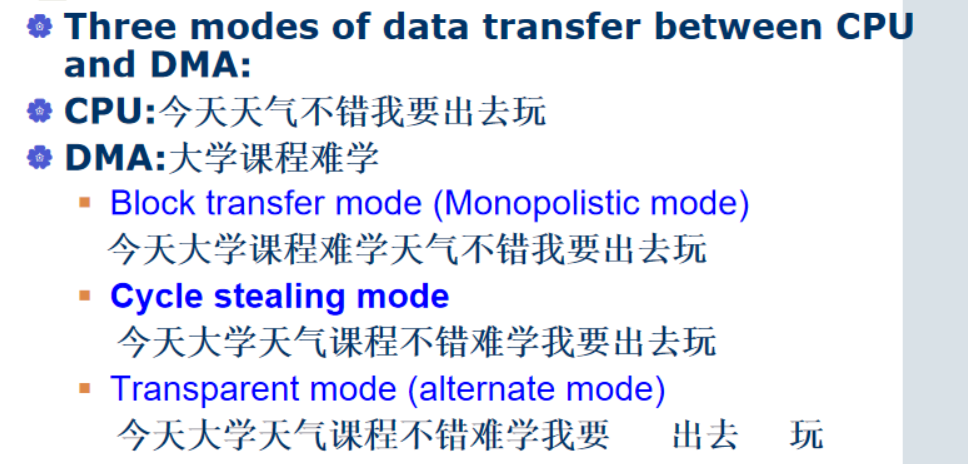

Three modes of data transfer between CPU and DMA

- Block transfer mode (Monopolistic mode)

- 当DMA传送数据的时候,CPU不能使用总线

- An entire block of data is transferred in one contiguous sequence

- If DMA transfers data, CPU be disabled for a duration until DMA release bus

- Useful for loading an programs or data files into memory

- Cycle stealing mode

- DMA与CPU交替传输数据

- DMA uses the bus only when CPU does not need it or forcing CPU to suspend operation temporarily

- DMA transfer one word of data, then release bus

- DMA interleaves instructions and data transfers

- Transparent mode (alternate mode)

- DMA与CPU分别占用时钟的上升沿和下降沿工作

- DMA and CPU use bus by division time multiplexing

- Require most time, but most efficient

DMA Structure

数据总线分别于数据计数器,数据寄存器,地址寄存器相连

过程

CPU首先通过Address Lines向地址寄存器发送需要请求的设备地址号,DMA将CPU传来的设备号直接发给I/O,然后CPU通过Data Lines向DMA发送对应的内存地址,存入地址寄存器中保存,CPU通过数据线将数据发送至数据寄存器,DMA将该数据再写入I/O设备中

- Preprocessing: CPU tells DMA controller

- Read/Write

- Device address

- Starting address of memory block for data

- Amount of data to be transferred

- CPU carries on with other work

- Data transferring: DMA controller deals with transfer (word by word)

- Postprocessing: DMA controller sends interrupt when finished

DMA Transfer Cycle Stealing

- DMA controller takes over bus for a cycle

- Transfer of one word of data

- Not an interrupt

- CPU does not switch context

- CPU suspended just before it accesses bus

- i.e. before an operand or data fetch or a data write

- Slows down CPU but not as much as CPU doing transfer

DMA and Interrupt Breakpoints During an Instruction Cycle

DMA Configurations

Single Bus, detached DMA controller

- Each transfer uses bus twice

- I/O to DMA then DMA to memory

- CPU is suspended twice

Single Bus, Integrated DMA controller

- Controller may support >1 device

- Each transfer uses bus once

- DMA to memory

- CPU is suspended once

Separate I/O Bus

- Bus supports all DMA enabled devices

- Each transfer uses bus once

- DMA to memory

- CPU is suspended once

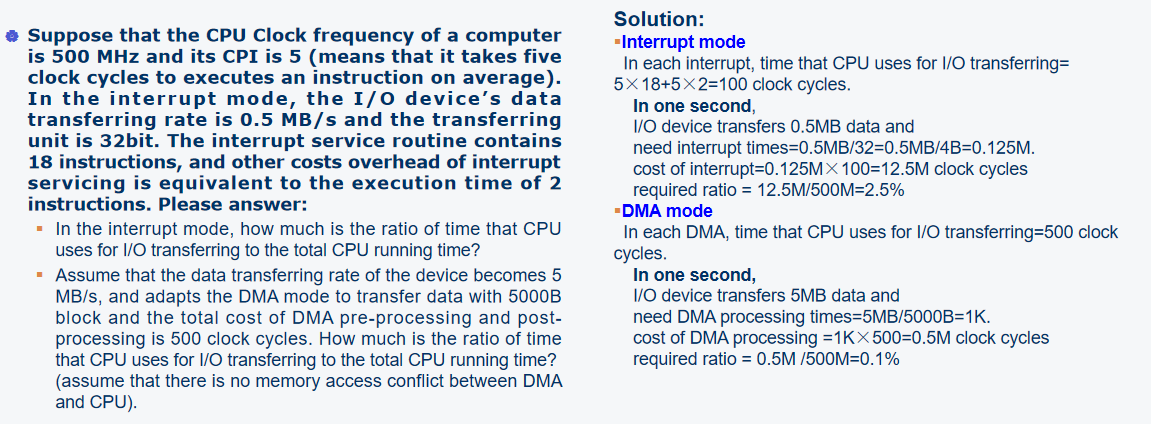

例题

I/O Channels

- I/O channel is an I/O module with its own processor which can execute I/O program

- I/O program is located in main memory

- In fact, the I/O channel represents an extension of the DMA concept

- Thus, an I/O channel has the ability to execute I/O instructions and control the I/O operations

Functions of I/O Channels

- Receive command from CPU

- Micro command

- Load I/O program from memory, send commands to device

- Buffer, control and transfer data, provide path for transferring

- Report device status or interrupt

Working Principle

- Master CPU sends I/O command and waits channel and device ready

- the number of Channel

- the number of device

- Entry of channel program

- Size of data

- Master CPU starts the channel and returns to main program

- The channel executes I/O program to transfer data between memory and device

- When data transfer completed, interrupt CPU

Types of I/O Channels

Channel Capacity/data-transmission rate

- Maximum data transmitted per unit time of channel

Selector channel

- At any one time, only one device is selected to transfer data

- High-speed devices

Multiplexor channel

- Byte multiplexor channel

- Round robin between devices

- For a device, only one byte data transferred

- For low speed devices

- Block multiplexor channel

- Round robin between devices

- For a device, K bytes data transferred

Evolution of the I/O Function

- CPU directly control a peripheral

- A control or I/O module is added

- programmed I/O

- Interrupt-driven I/O

- DMA

- Device–memory

- I/O channel

- I/O processor, no local memory

- I/O processor

- I/O processor + local memory

External Interface

没讲

Connecting devices together

- Point to point

- Dedicated line between I/O module and external devices

- E.g. keyboard, printer, modem, etc.

- Point to multi-point

- external buses

- External mass storage

- Multimedia devices (CD-ROMs, video, audio)

Serial or parallel

- Printer, mouse, keyboard, etc.

- Disk, tape, etc.

Write operation from I/O module to a peripheral

- I/O module sends a control signal requesting permission to send data

- The peripheral acknowledges the request

- The I/O module transfers data

- The peripheral acknowledges the receipt of the data

Small Computer Systems Interface (SCSI)

- Standard interface for CD-ROM drive, audio equipment, external mass storage devices

- Parallel interface

- 8, 16, 32 bit data lines

- Daisy chained local bus, attached to PCI

- Devices are independent

- Devices can communicate with each other as well as host

Key points

- Functions of I/O Module?

- I/O module structure

- Input Output Modes

- What is 82c59a?

- DMA &channel

- SCSI

- Firewire

Vocabulary

- Cycle stealing: 周期窃取

- Interrupt: 中断

- Isolated I/O:分离式I/O

- Memory-mapped I/O:存储映射式I/O

- Multiplexor channel:多路转换通道

- Parallel I/O:并行器I/O

- Peripheral device : 外围设备

- Selector channel:选择通道

163

163

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?