问题描述:

对于ZYNQ用到的纯PL程序,仍然需要引入PS端,通过fsbl来加载比特流文件。

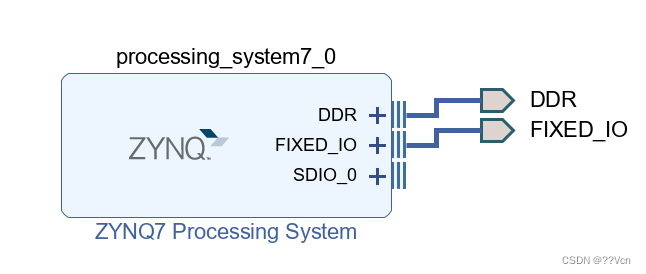

在Vivado编写PL端逻辑代码后,创建block design并添加ZYNQ IP,配置为最小系统。generate output products,create HDL wrapper。

在顶层模块例化block design和PL逻辑代码,编写xdc约束文件,并生成比特流文件,将硬件(.xsa)导出。

在Vitis以刚才导出的xsa文件为基础创建应用工程,应用模板选择zynq fsbl即可。

编译fsbl程序。

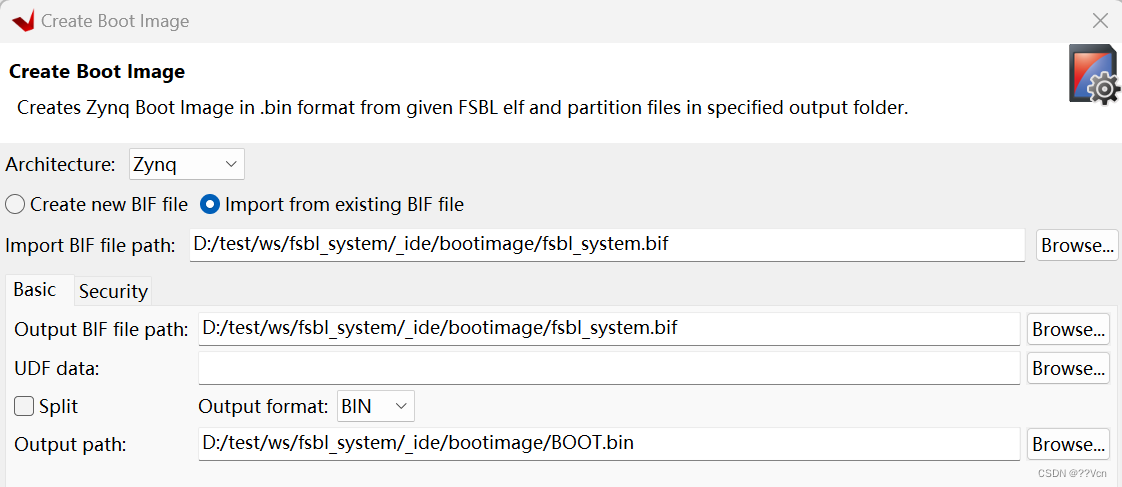

create boot image,选择导出的bif文件的路径。

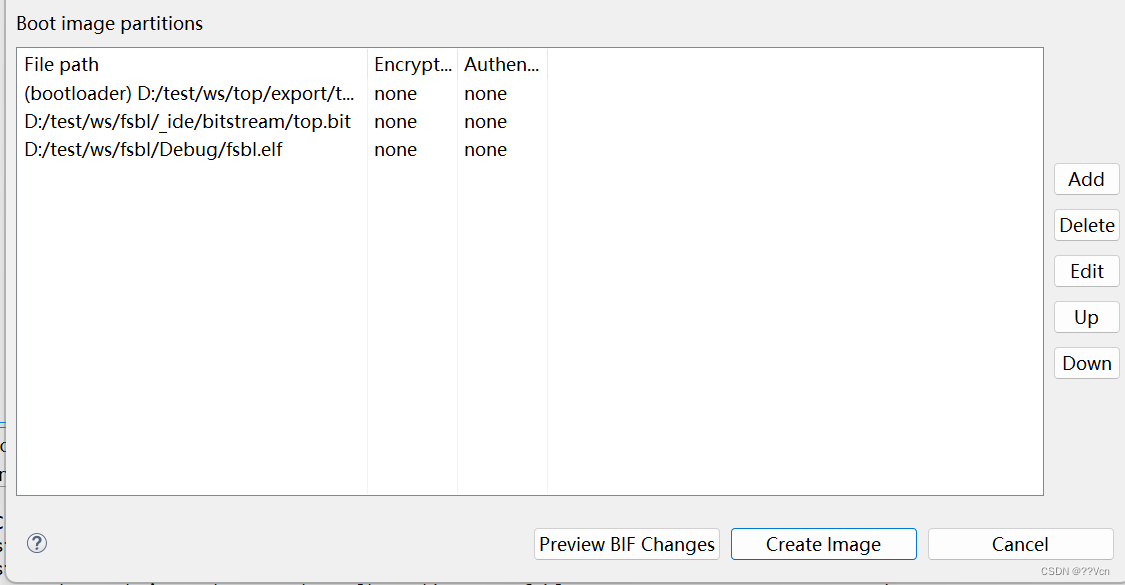

在窗口下方,依次添加fsbl.elf,比特流,应用程序的elf文件(此处仅用到PL逻辑,只添加了fsbl.elf和比特流)

点击create image,固化文件BOOT.BIN创建成功。

将刚才生成的BOOT.BIN拷贝到格式化后的SD卡根目录中,插入开发板并上电,观察到PL程序并没有成功运行。而且在vivado打开hardware manager也会提示no debug cores。

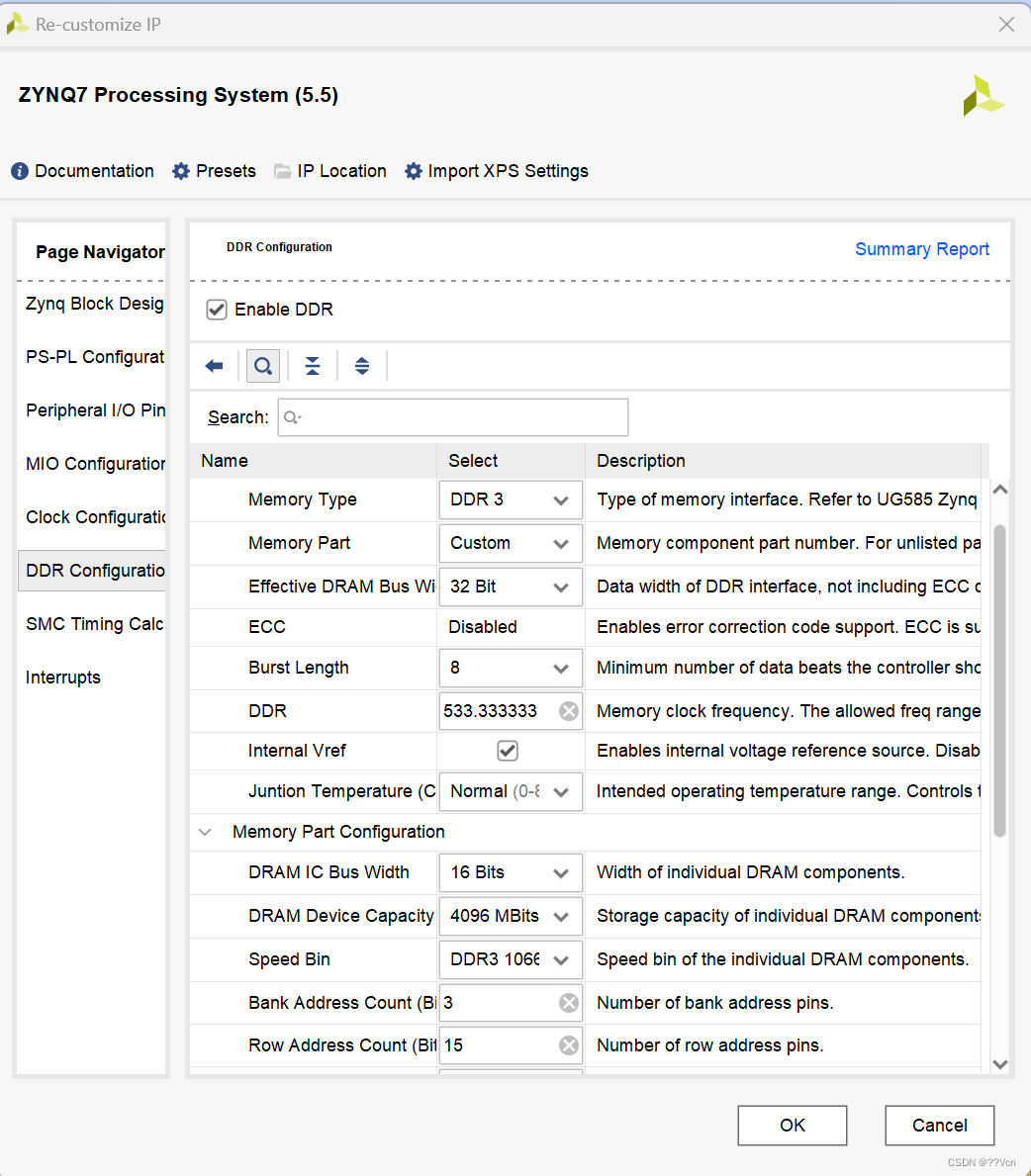

经过分析,可能的原因是在ZYNQ IP对DDR3的配置中,如果将memory part选择为Custom,需要根据板卡DDR3的具体情况来对ZYNQ PS7 IP进行配置。

将DDR3配置信息正确修改后,成功将PL端程序固化,将JTAG连接PC与板卡,在Vivado打开hardware manager也可以看到ILA界面。

参考链接:

7770

7770

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?