FPGA入门

1.用verilog HDL编写二选一选择器

module mux2(

a,

b,

sel,

out

);

input a;

input b;

input sel;

output out;

assign out=sel?b:a;

endmodule2.测试仿真脚本

`timescale 1ns/1ps

module mux2_tb();

reg s1;

reg s2;

reg s3;

wire Light1;

mux2 mux2_intest0(

.a(s1),

.b(s2),

.sel(s3),

.out(Light1)

);

initial begin

s1=0;s2=0;s3=0;

#100;

s1=1;s2=0;s3=0;

#100;

s1=0;s2=1;s3=0;

#100;

s1=1;s2=1;s3=0;

#100;

s1=0;s2=0;s3=1;

#100;

s1=1;s2=0;s3=1;

#100;

s1=0;s2=1;s3=1;

#100;

s1=1;s2=1;s3=1;

#100;

$stop;

end

endmodule计数器

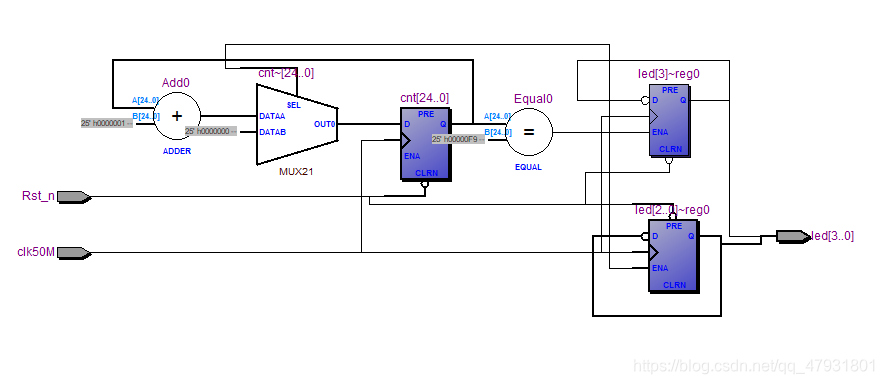

1.用verilog HDL编写计数器

module led_flash(

clk50M,

Rst_n,

led

);

input clk50M;

input Rst_n;

output reg[3:0]led;

reg[24:0]cnt;//25位寄存器

/*led<=4'b1111

led=!led

led<=1

led=!led

led<=0

逻辑取反

led<=4'b1111

led=~led

led<=4'b0000

led=~led

led<=4'b1111

按位取反

*/

always@(posedge clk50M or negedge Rst_n)

if(!Rst_n)

cnt<=25'd0;//非阻塞赋值方式

else if(cnt==25'd24_999_999)

cnt<=25'd0;

else

cnt<=cnt+1'b1;

always@(posedge clk50M or negedge Rst_n)

if(!Rst_n)

led<=4'b1111;

else if(cnt==25'd24_999_999)

led=~led;

else

led<=led;

endmodule 2.仿真脚本

`timescale 1ns/1ps

`define clock_period 20

module led_flash_tb();

reg clk50M;

reg Rst_n;

wire [3:0]led;

led_flash led_flash0(

.clk50M(clk50M),

.Rst_n(Rst_n),

.led(led)

);//生成50M时钟信号

initial clk50M=1;

always #(`clock_period/2) clk50M=~clk50M;

initial begin

Rst_n=0;

#(`clock_period*20+1) Rst_n=1;

#(`clock_period*25000000);

$stop;

end

endmodule

//module led_flash(

//clk50M,

//Rst_n,

//led

//);

//input clk50M;

//input Rst_n;

//output [3:0]led;

//reg [24:0]cnt;

//always@(posedge clk50M or negedge Rst_n)

//if(!Rst_n)

//cnt<=25'd0;

//else if(cnt==25'd24_999_999)

//cnt<=25'd0;

//else

//cnt<=cnt+1'b1;

//always@(posedge clk50M or negedge Rst_n)

//reg [3:0]led_r

//

//if(!Rst_n)

//led_r<=4'b0001;

//else if(cnt==25'd24_999_999)begin

//if(led_r==4'b1000)

//led_r<=4'b0001;

//else

//led_r<=led_r<<1;

//end

//else

//led_r<=led_r;

//assign led=~led_r;

//endmodule 计数器移位操作

1667

1667

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?