1.一位全加器

写法一:卡诺图描述

module fulladder(

input a,

input b,

input cin,

output s,

output cout);

assign s = a ^ b ^ cin;

assign cout = a & b | cin & (a ^ b);

endmodule写法二:行为级描述

module fulladder(

input a,

input b,

input cin,

output s,

output cout);

assign {cout,s} = a + b + cin;

endmodule2.行波进位加法器/串行加法器

module 4fulladder(

input [3:0] a_in,

input [3:0] b_in,

input cin,

output [3:0] s_o,

output cout_o);

wire [3:1] cin_o;

fulladder fulladder0(.a(a_in[0]), .b(b_in[0]), .cin(cin), .s(s_o[0]), .cout(cin_o[1]));

fulladder fulladder1(.a(a_in[1]), .b(b_in[1]), .cin(cin_o[1]), .s(s_o[1]), .cout(cin_o[2]));

fulladder fulladder2(.a(a_in[2]), .b(b_in[2]), .cin(cin_o[2]), .s(s_o[2]), .cout(cin_o[3]));

fulladder fulladder3(.a(a_in[3]), .b(b_in[3]), .cin(cin_o[3]), .s(s_o[3]), .cout(cout_o));

endmodule

module fulladder(

input a,

input b,

input cin,

output s,

output cout);

assign {cout,s} = a + b + cin;

endmodule3.超前进位加法器

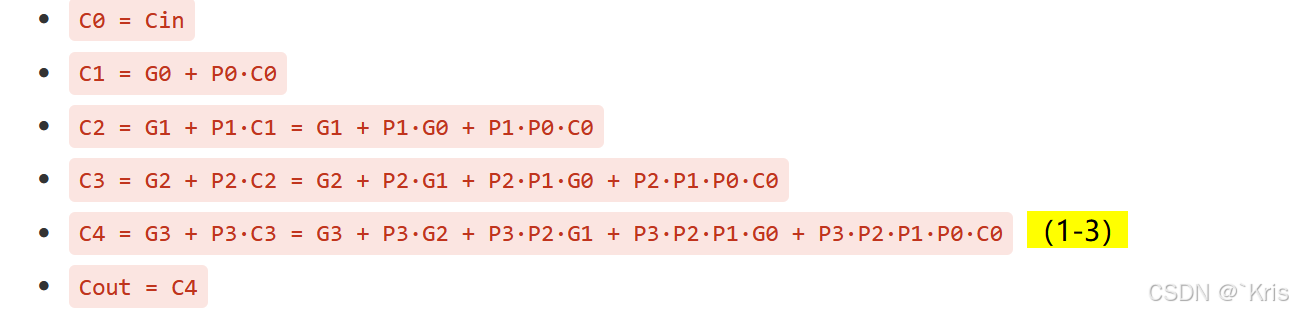

根据串行进位加法器的运算可以看出,前一位的进位要得到其进位信号以后才可以继续进行计算,这个过程浪费了太多时间。于是人们将表达式C_o = AB + Cin(A ^ B),令Gi = AB ,Pi = A^B,按位展开,惊奇的发现:

原来特定位的进位不需要得到输入进位信号,Pi~Gi是可以提前算出来的,C0也是已知的,他们可以并行算出!实现这个逻辑的部件,称为CLA部件。超前进位加法器和串行进位加法器的写法,我觉得只是超前进位加法器多了计算C的CLA步骤

module adder_4(

input [3:0] a,

input [3:0] b,

input cin,

output [3:0] s

output co);

wire [4:1] g, p;

assign g = a & b;

assign p = a ^ b;

wire c1,c2,c3,c4;

assign c1 = g[1] | cin & p[1];

assign c2 = g[2] | p[2] & g[1] | p2 & p1 & cin;

assign c3 = g[3] | p[3] & g[2] | p[3] & p[2] & g[1] | p[3] & p[2] & p[1] & cin;

assign c4 = g[4] | p[4] & g[3] | p[4] & p[3] & g[2] | p[4] & p[3] & p[2] & g[1] | p[4] & p[3] & p[2] & p[1] & cin;

fulladder adder1(.a(a[0]), .b(b[0]), .cin(cin), .s(s[0]), .co());

fulladder adder2(.a(a[1]), .b(b[1]), .cin(c1), .s(s[1]), .co());

fulladder adder3(.a(a[2]), .b(b[2]), .cin(c2), .s(s[2]), .co());

fulladder adder4(.a(a[3]), .b(b[3]), .cin(c3), .s(s[3]), .co());

endmodule

module fulladder(

input a,

input b,

input cin,

output s,

output co);

assign s = a ^ b ^ cin;

assign co = a & b | cin & (a ^ b);

endmodule

151

151

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?