在使用乘法器和乘加器中遇到了一些问题,解决后仍有疑问,以此记录

乘法器

乘法器是指只有数据中只有乘法运算,运算时p=a*b

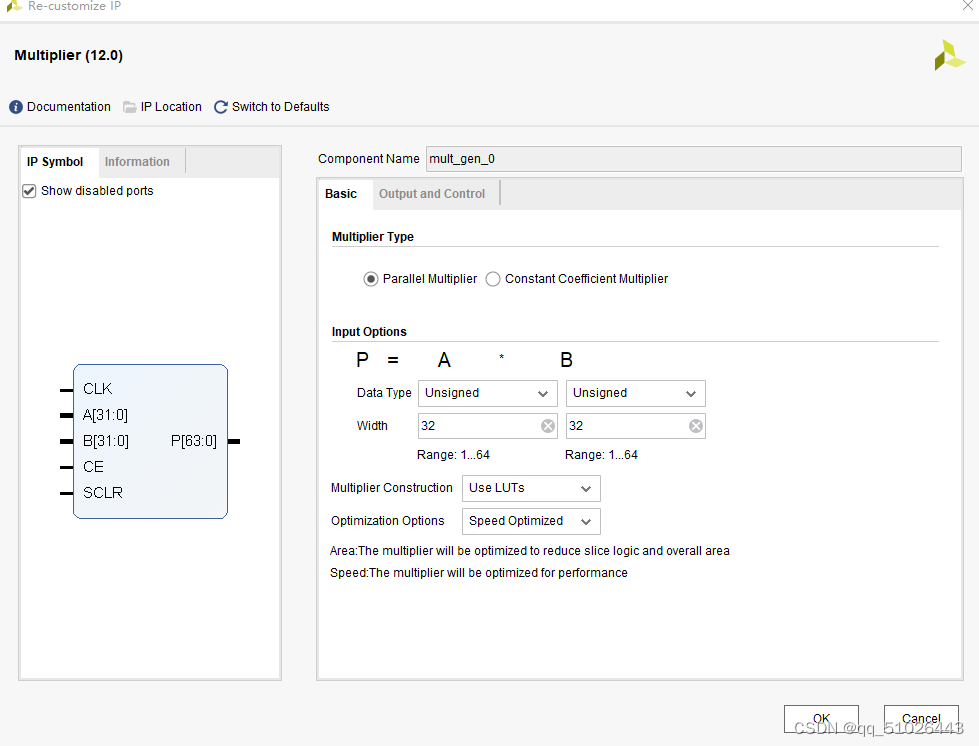

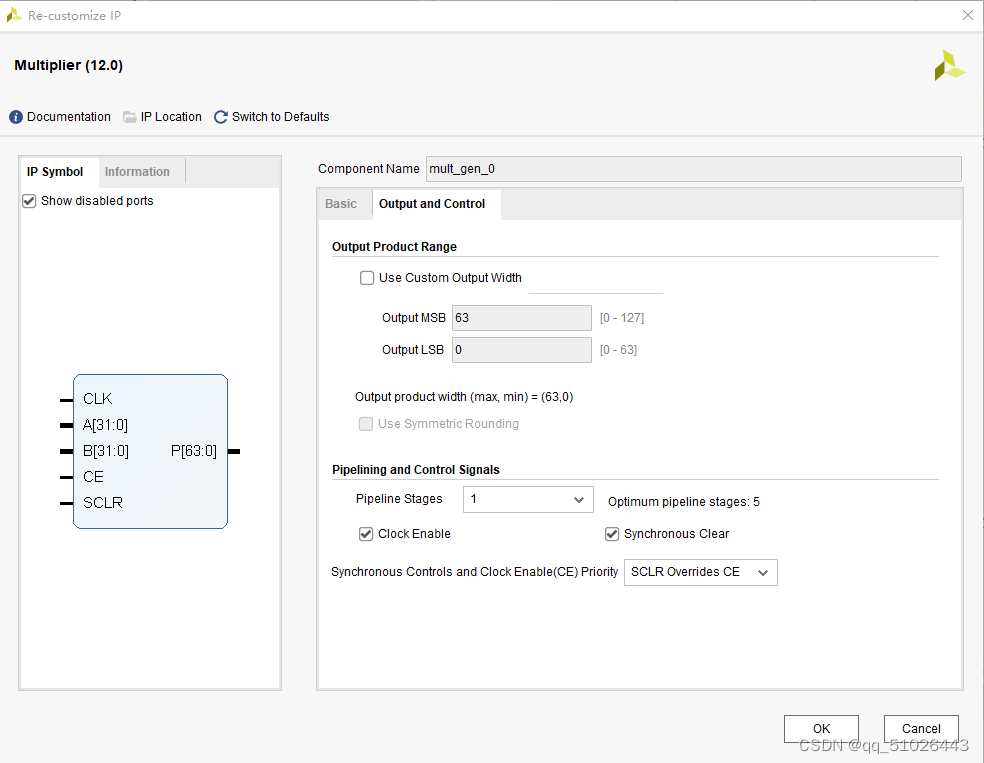

进行如下图所示设置

借用一张描

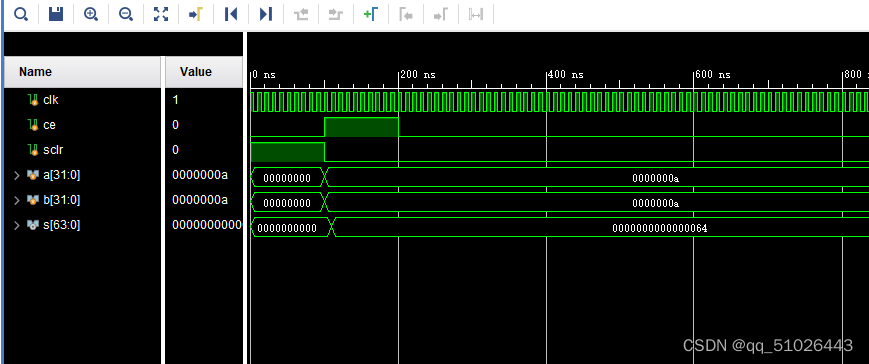

仿真代码

always #5 clk=~clk;

initial

begin

clk = 1;

a = 0;

b = 0;

ce = 0;

sclr = 1;

#100;

sclr = 0;

ce = 1;

a = 10;

b = 10;

#100;

ce = 0;

end

mult_gen_0 uut (

.CLK(clk), // input wire CLK

.A(a), // input wire [15 : 0] A

.B(b), // input wire [15 : 0] B

.CE(ce), // input wire CE

.SCLR(sclr), // input wire SCLR

.P(s) // output wire [31 : 0] P

);

endmodule成功得到仿真结果100

乘加器

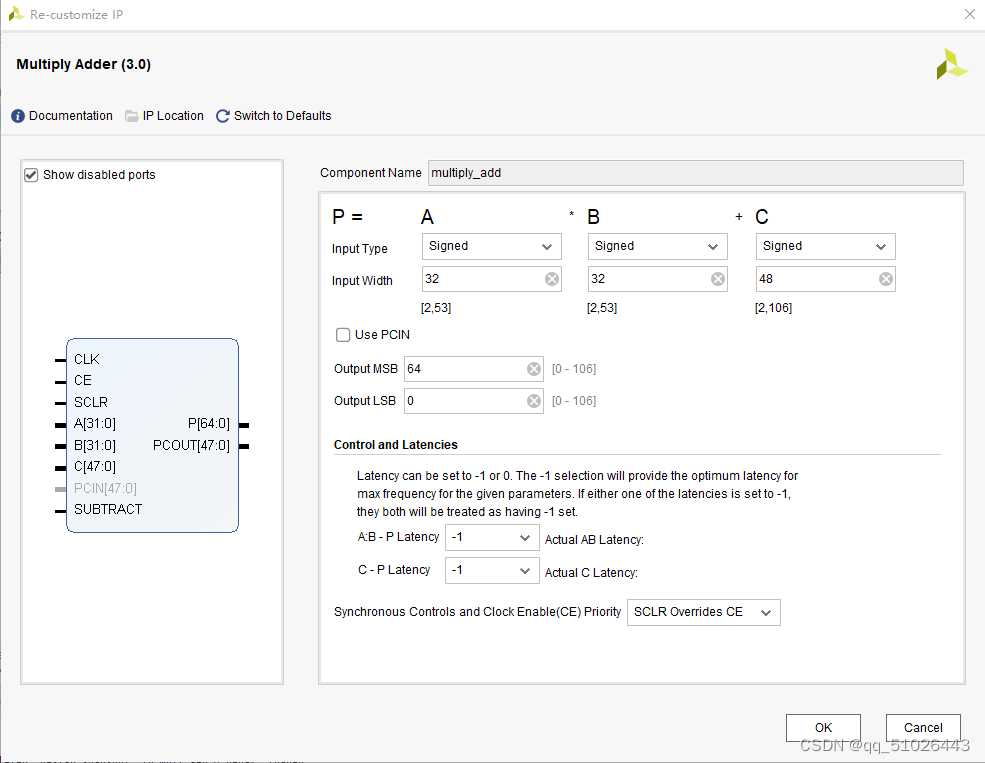

乘加器的运算时p=a*b+c,在此不进行+c的运算,只运行a*b的运算,并不进行级联运算

以下为端口定义

A[N:0] Input A输入(乘法操作数1)

B[M:0] Input B输入(乘法操作数2)

C[L:0] Input C输入(加减操作数)

PCIN Input 级联输入

SUBTRACT Input 控制加/减操作(1=减法,0=加法)

CE Input 时钟使能 (高有效)

CLK Input 时钟信号,上升沿有效

SCLR Input 同步复位,高有效

PCOUT Output 输出级联

P[Q:0] Output 输出端口

原文链接:https://blog.csdn.net/weixin_41445387/article/details/119777736

仿真代码

module tb_mult_gen_0;

// Inputs

reg clk;

reg ce;

reg sclr;

reg [31:0] a;

reg [31:0] b;

// Outputs

wire [63:0] s;

// Instantiate the Unit Under Test (UUT)

always #5 clk=~clk;

initial

begin

clk = 1;

a = 0;

b = 0;

ce = 0;

sclr = 1;

#100;

sclr = 0;

ce = 1;

a = 10;

b = 10;

#100;

ce = 0;

end

multiply_add uut (

.CLK(clk), // input wire CLK

.CE(ce), // input wire CE

.SCLR(sclr), // input wire SCLR

.A(a), // input wire [15 : 0] A

.B(b), // input wire [15 : 0] B

.C(0), // input wire [47 : 0] C

.SUBTRACT(0), // input wire SUBTRACT

.P(s) // output wire [40 : 0] P

);

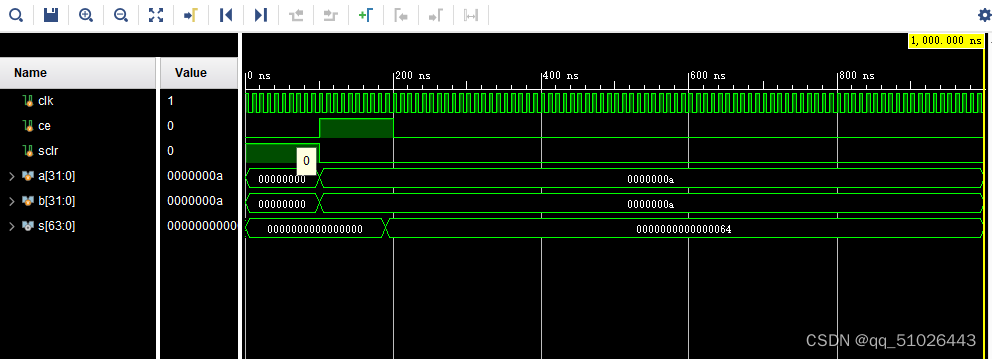

endmodule得到正确仿真结果100

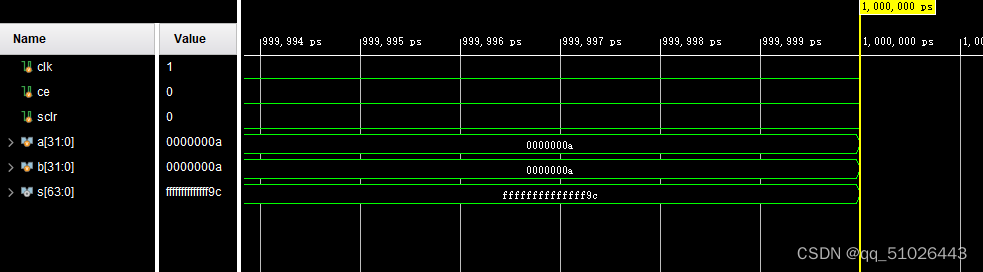

但当

SUBTRACT(0)改为 SUBTRACT(1)时

输出结果为-100

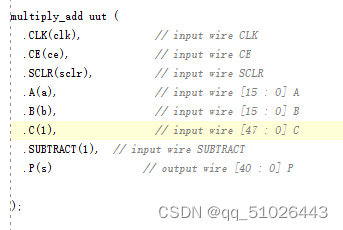

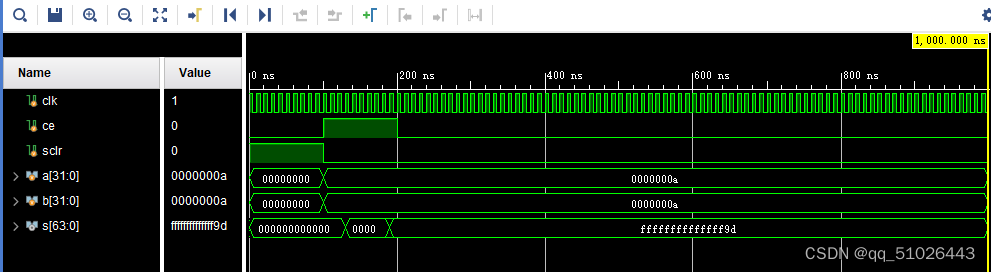

将例化中c改为1

得到结果为-99

总结

所以乘加器在此次仿真时SUBTRACT 端口为0,乘出的结果为负,为1乘出的结果为正,再去加上c

文章介绍了在Verilog中对乘法器和乘加器进行仿真的过程。乘法器实现了简单的乘法运算,而乘加器则可以进行乘法加法操作。在乘加器的仿真中,改变SUBTRACT信号的值会影响输出结果,当SUBTRACT为1时,结果会变为负数,表明其进行了减法运算。通过设置不同的输入值,观察到乘加器如何根据SUBTRACT端口的值来决定是执行加法还是减法,并影响最终的输出结果。

文章介绍了在Verilog中对乘法器和乘加器进行仿真的过程。乘法器实现了简单的乘法运算,而乘加器则可以进行乘法加法操作。在乘加器的仿真中,改变SUBTRACT信号的值会影响输出结果,当SUBTRACT为1时,结果会变为负数,表明其进行了减法运算。通过设置不同的输入值,观察到乘加器如何根据SUBTRACT端口的值来决定是执行加法还是减法,并影响最终的输出结果。

3927

3927

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?