笔记来自正点原子官方教学视频16.1-16.5讲

时间:2025/2/5

【第一期】手把手教你学领航者&启明星ZYNQ之FPGA开发篇【真人出镜】FPGA教学视频教程_哔哩哔哩_bilibili

前言

什么是在线调试?

在线调试也称为板级调试,它是将程序文件下载到FPGA芯片后分析代码运行的情况。

为什么要在线调试?

1、直接观察代码很难找到BUG ;

2、仿真不全面,难以做到100%的代码覆盖率;

3、在板级交互中,存在异步事件,很难做到仿真,或者仿真起来时间很长,无法运行;

4、外围电路可靠性问题,如电源问题、信号干扰等导致程序运行出错。

调试的重要性

1、在整个FPGA设计中,硬件调试与验证会花费超过40%的时间;

2、低效的策略可能导致产品发布延迟

相关介绍

在线调试的方法如下:

①、利用外部测试设备,如示波器和逻辑分析仪等;

②、利用FPGA开发工具自带的在线调试工具(在线逻辑分析仪)。

FPGA的开发工具会自带在线调试工具,举例如下:

| FPGA厂商 | FPGA开发工具 | 在线调试工具 |

| Xilinx | Vivado | ILA(Integrated Logic Analyzer ) |

| Xilinx | ISE | ChipScope |

| Altera | Quartus II | SignalTap II |

| 紫光同创 | PDS | Debugger |

| ...... | ...... | ...... |

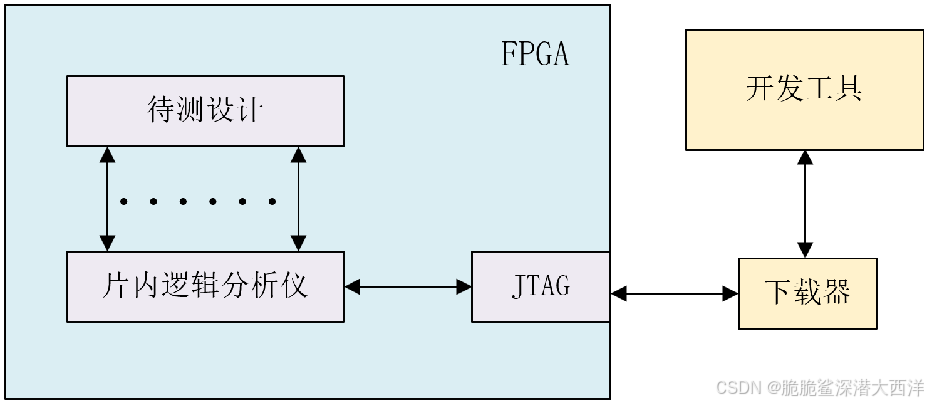

以下是在线调试工具的示意图:

需要注意的是:FPGA内部并非真的存在一个片内逻辑分析仪,这里利用FPGA的逻辑资源以及存储资源(例如:BRAM)来进行实现的,这个“片内逻辑分析仪”会将抓取到的信息存储在RAM中,再通过JTAG和下载器回传到开发工具。

另外一个需要注意的是:需要抓取的信号数量越多,位宽越大,占用的资源就越多。如果芯片剩余的资源不足,可能就无法实现片内逻辑分析仪的功能。这个时候就需要注释掉一些不重要的代码来保证来确保片内逻辑分析仪的功能能正常使用。

Xilinx在线调试解决方案:

①、Vivado工具集成了逻辑分析仪(ILA),用于替换外部的逻辑分析仪;

②、添加ILA核和VIO核实现在线调试;

③、通过JTAG接口和PC连接。

ILA(Integrated Logic Analyzer):监控逻辑内部信号和端口信号。

VIO(Virtual Input/Output ):实时监控和驱动逻辑内部信号 和端口信号。

添加ILA的方法如下:

①、添加ILA IP核,在代码中对ILA IP核进行例化;层次化最高的一种方法,比较直接,但缺点也比较明显,就是需要对HDL代码进行更改,在代码中对ILA进行例化,特别是在多个模块都有需要观察的信号时,每一个模块都需要单独例化一个ILA IP核。

②、(推荐方法)在原理图或者网表文件中添加”mark debug”属性;

③、(不推荐)手动地在XDC约束文件中编写对应的TCL XDC调试命令;层次化最低的一种方法,比较难写。

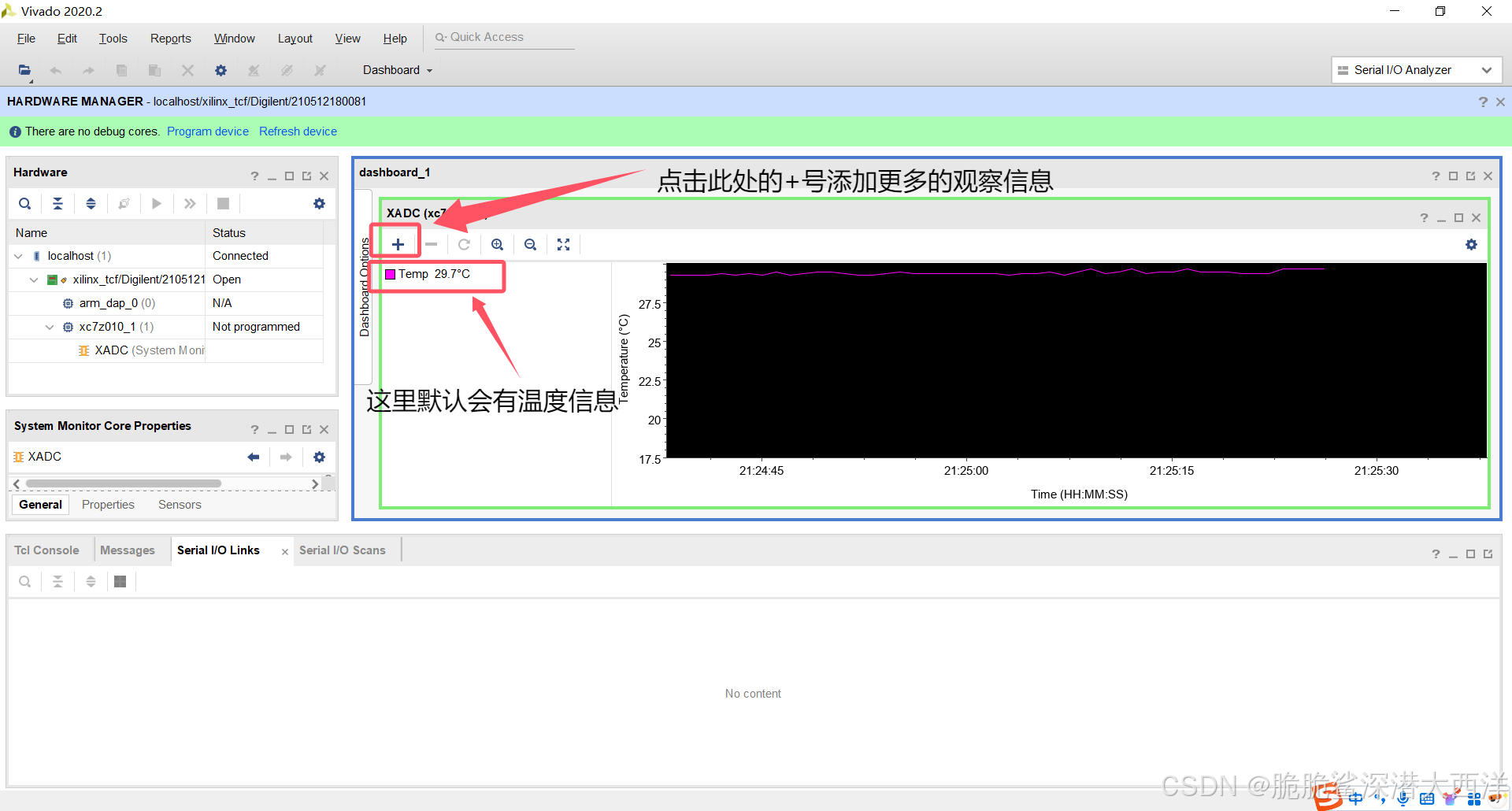

扩展部分(XADC硬核):FPGA的下载器不仅可以获取到FPGA内部的数据,并通过电脑来显示波形,其实还可以有更多的功能。FPGA内部有一个XADC硬核,可以通过这个硬核实时的采集芯片内部的温度和电压(比如:内核电压、BRAM电压)。

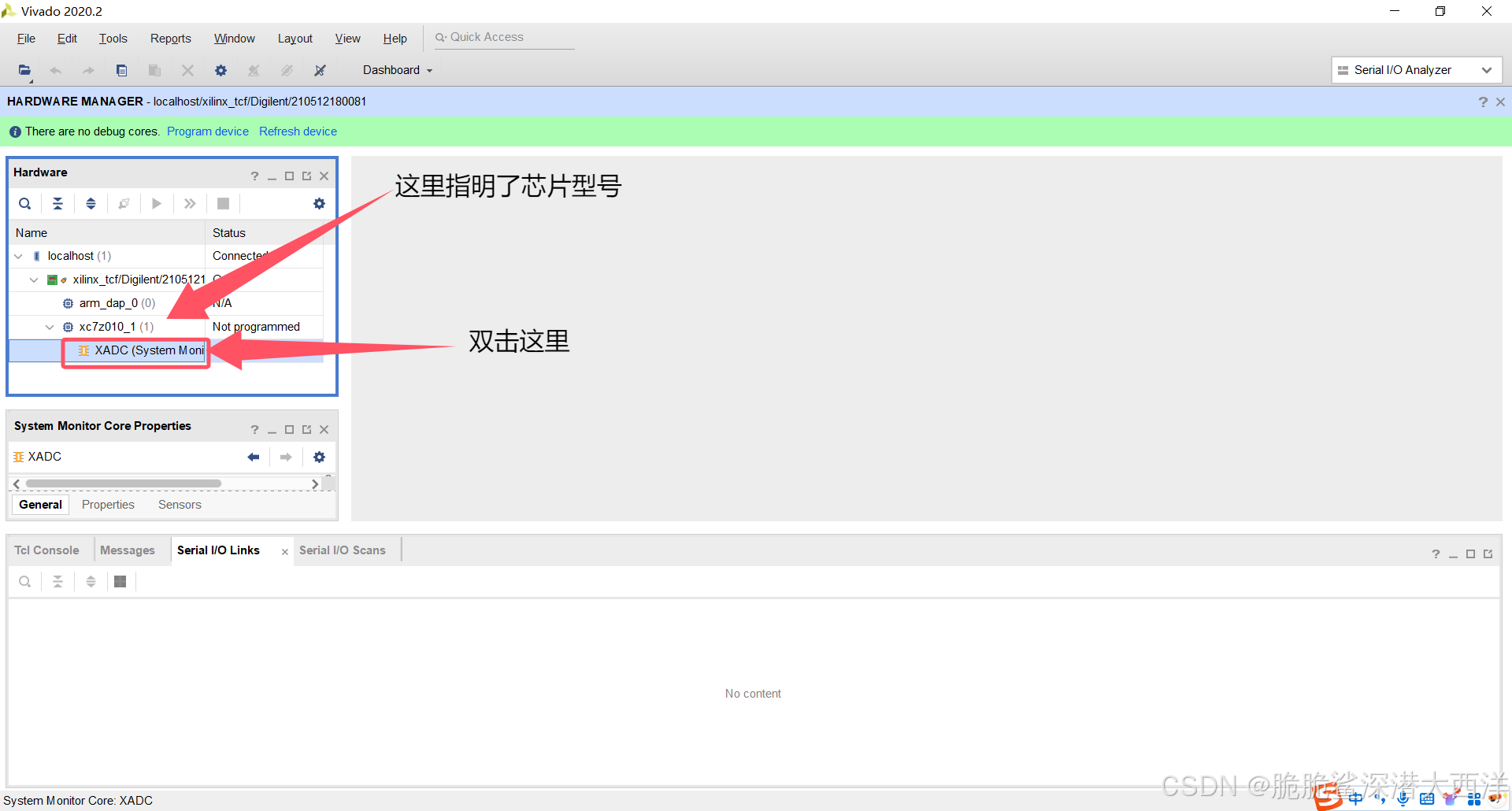

以下是XADC硬核的超详细使用方法:

①、将开发板的电源线和下载器正确连接,并接入电脑;

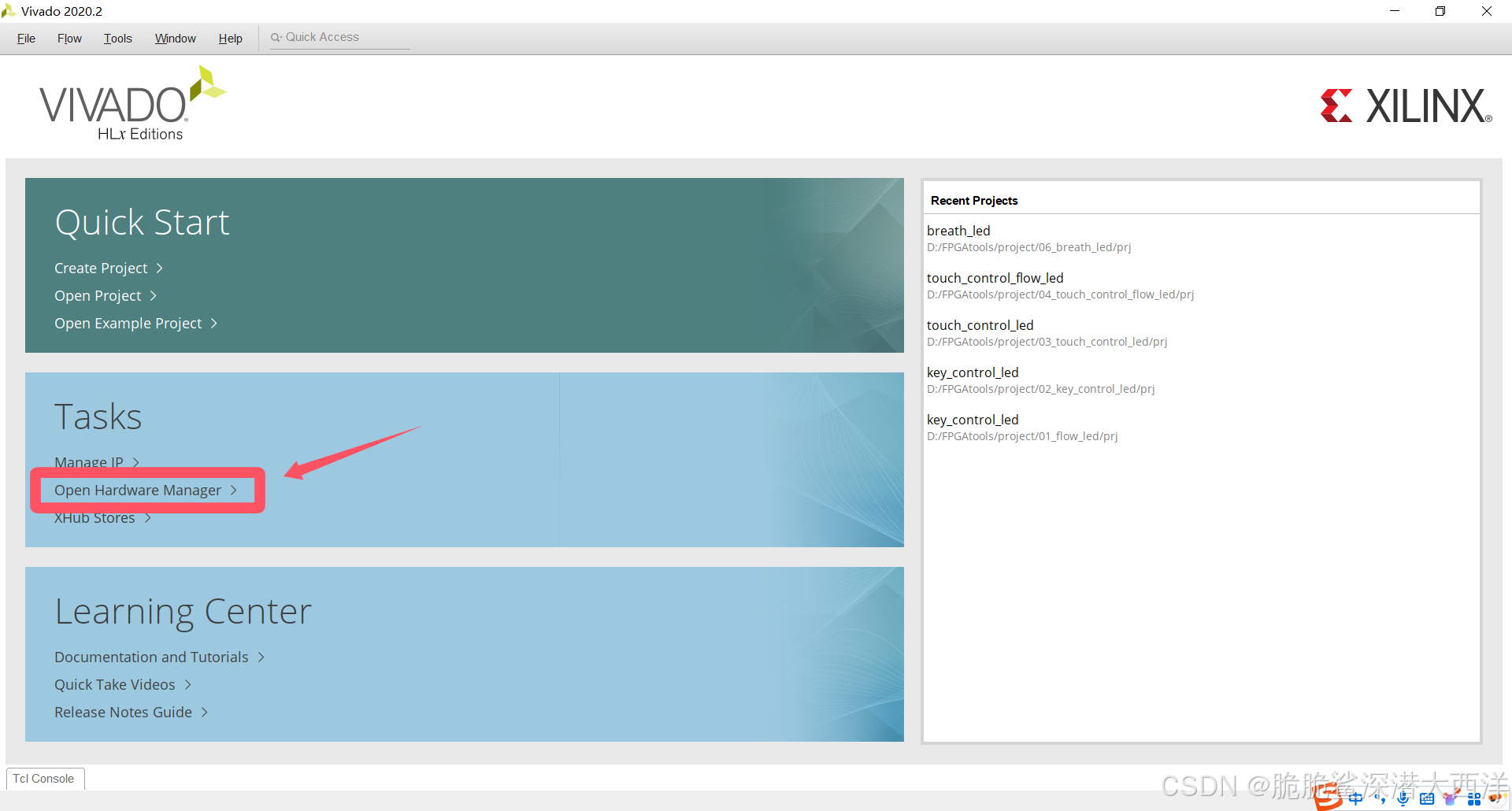

②、打开VIVADO软件,找到“Open Hardware Manager”选项,进入后连接开发板;

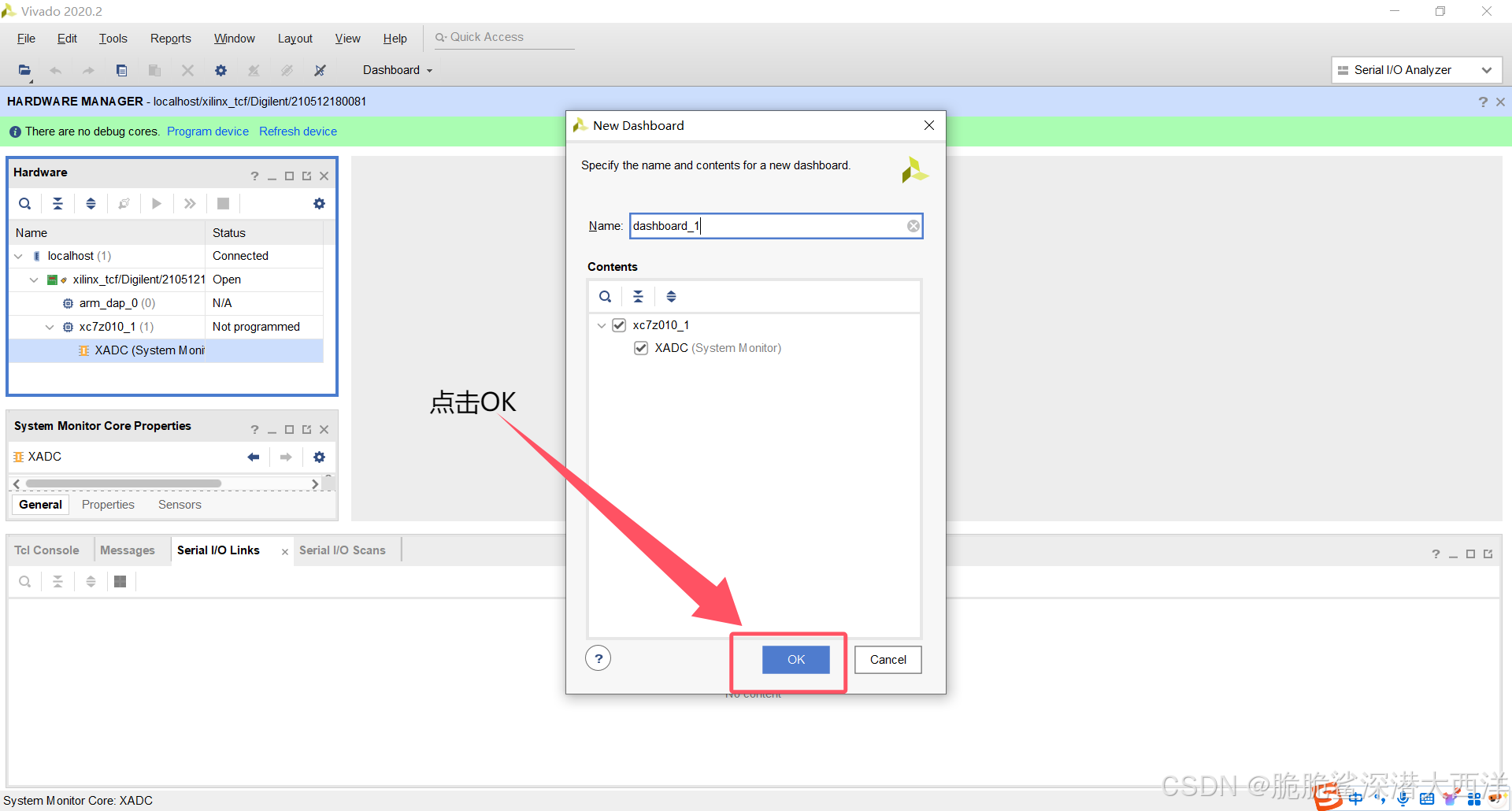

③、连接开发板,后续步骤也相当简单,如图所示。

在可以选择的更多观察信息中,简单说明以下两种:

有些电压是0的原因是相关功能还未使用,所以是为0V。

在线调试工具的具体使用方法

方法一:ILA IP核的使用

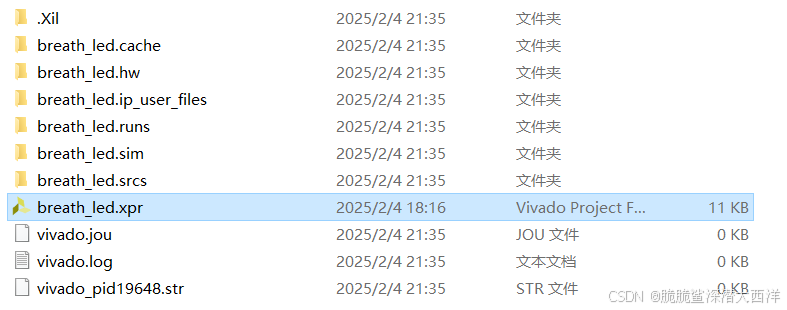

首先,打开一个FPGA项目(比如呼吸灯),找到.xpr文件,双击打开,如下所示:

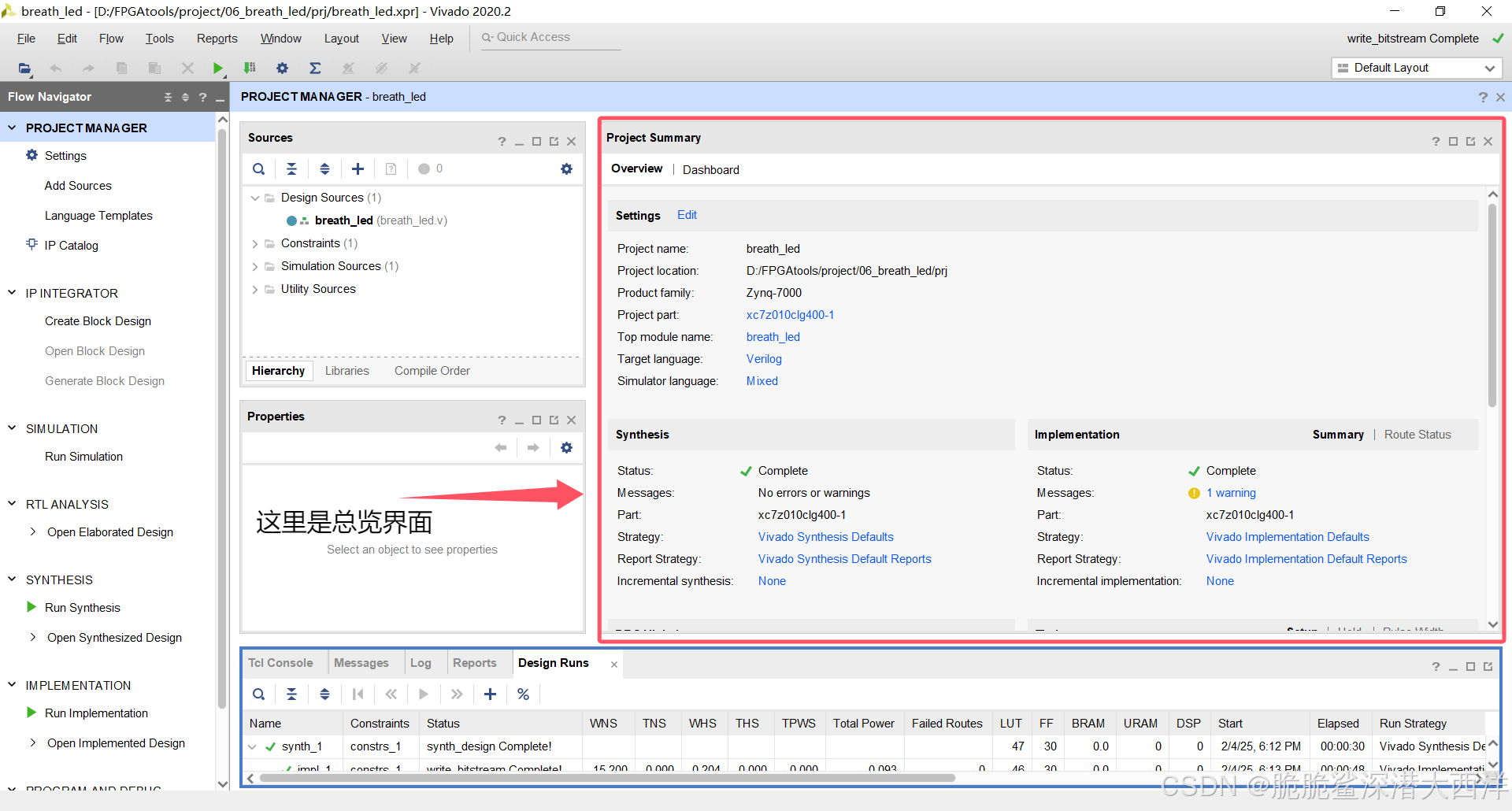

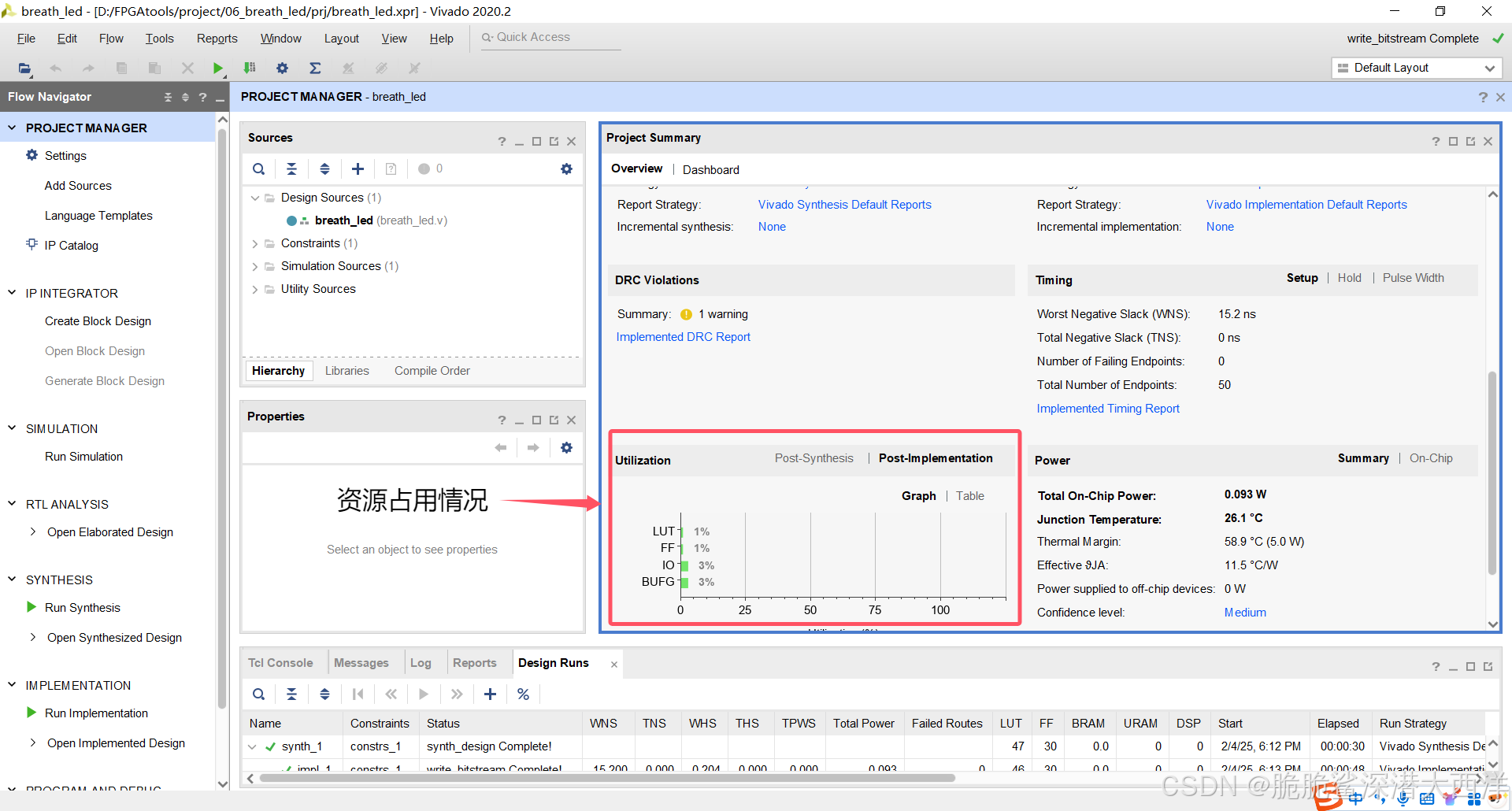

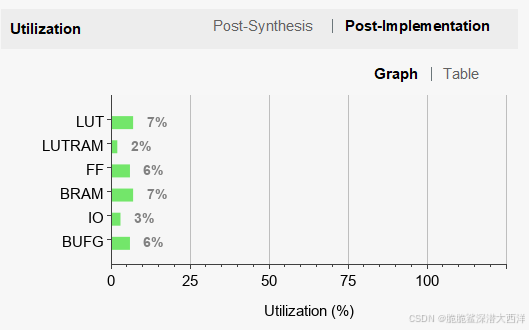

在总览界面向下滑动,找到Utilization部分,这里列出的是资源占用情况,从下图可以看出单纯的呼吸灯模块所占用的资源非常少,后续会与使用“片内逻辑分析仪”之后的占用情况进行对比。

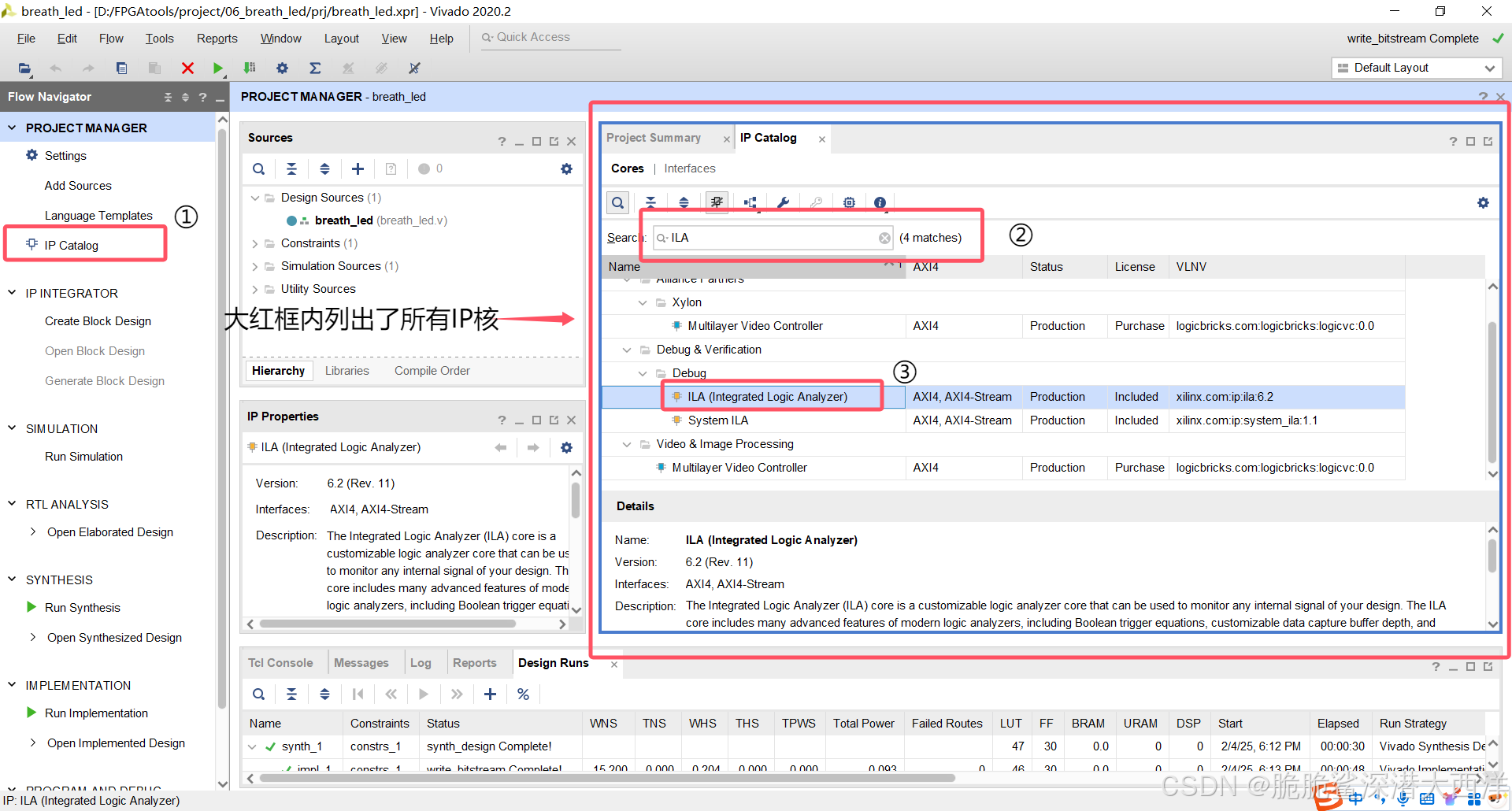

第一步:进入ILA IP核设置界面

首先第一步,点击左侧的“IP Catalog”选项,在搜索框中输入“ILA” ,接着双击“ILA (Integrated logic Analyzer)”,会弹出ILA的配置界面,以下来介绍配置界面。

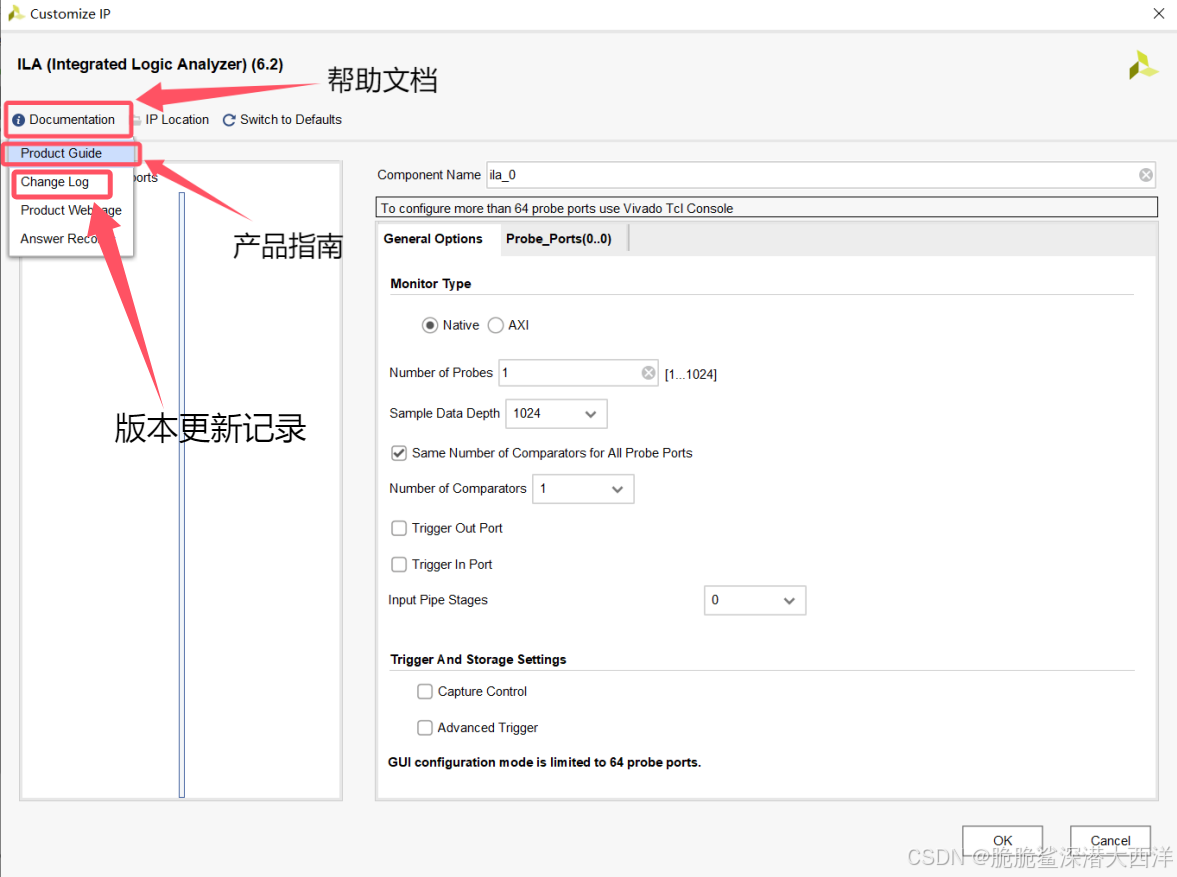

在打开的ILA配置界面中,“Documentation”是帮助文档,打开其中的“Product Guide”会打开DocNav这个软件中的IP核手册。 “Change Log”中记录了VIVADO版本的更新以及更新内容。

“Change Log”中记录了VIVADO版本的更新以及更新内容。

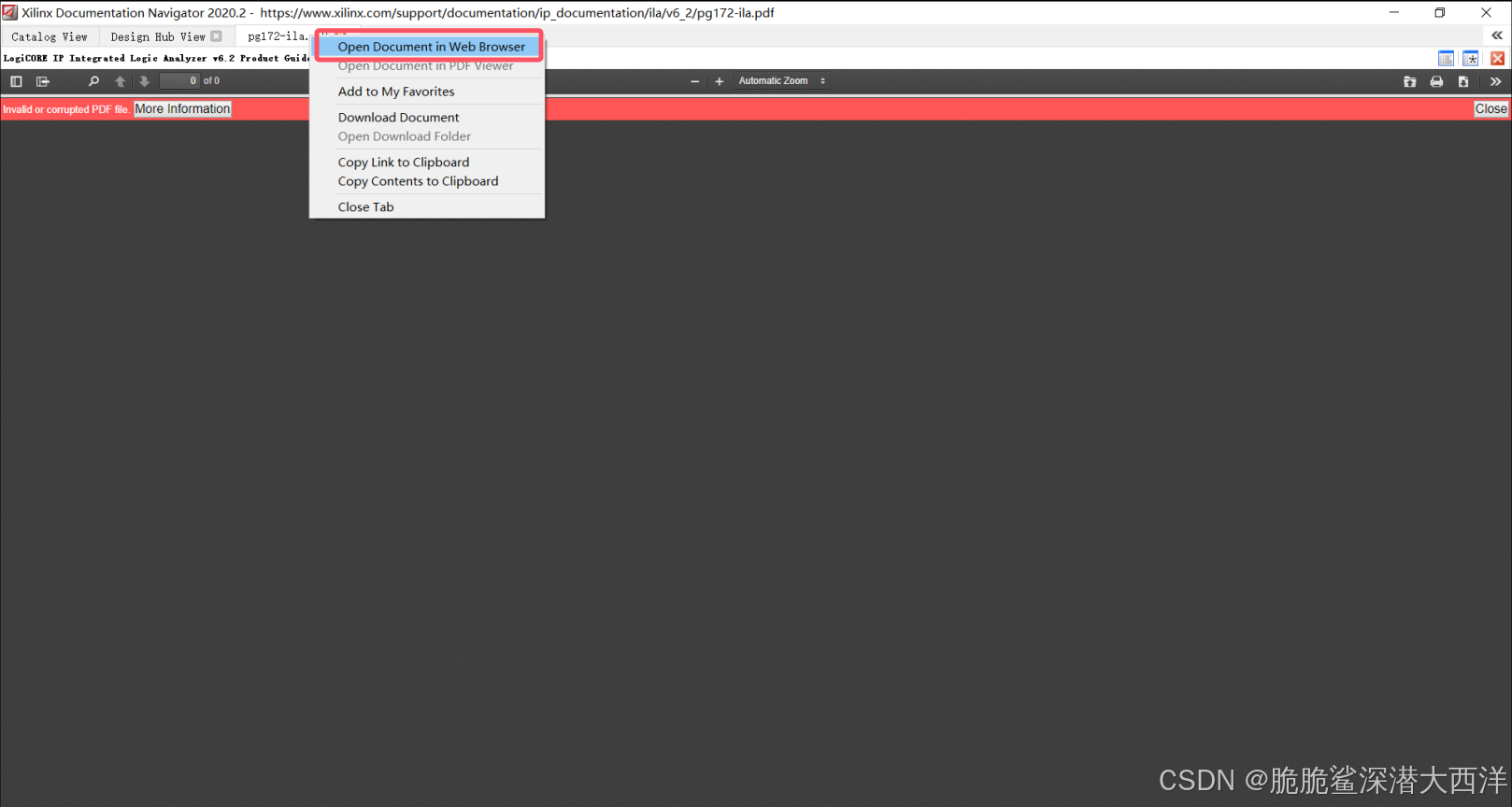

右键图中的选项卡,选择在浏览器界面中打开即可查看官方的IP核手册信息。

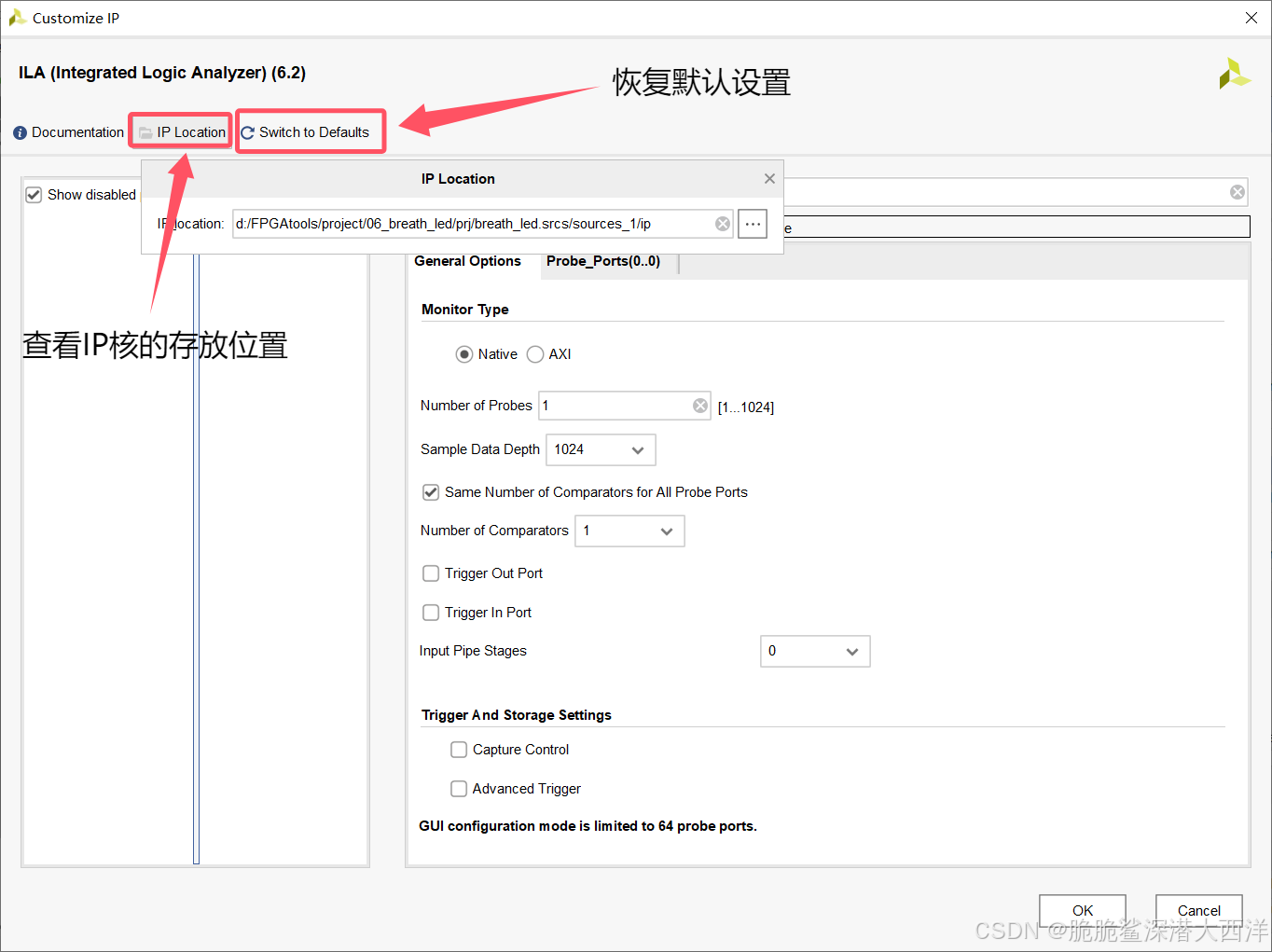

另外两个选项的功能如下图所示。

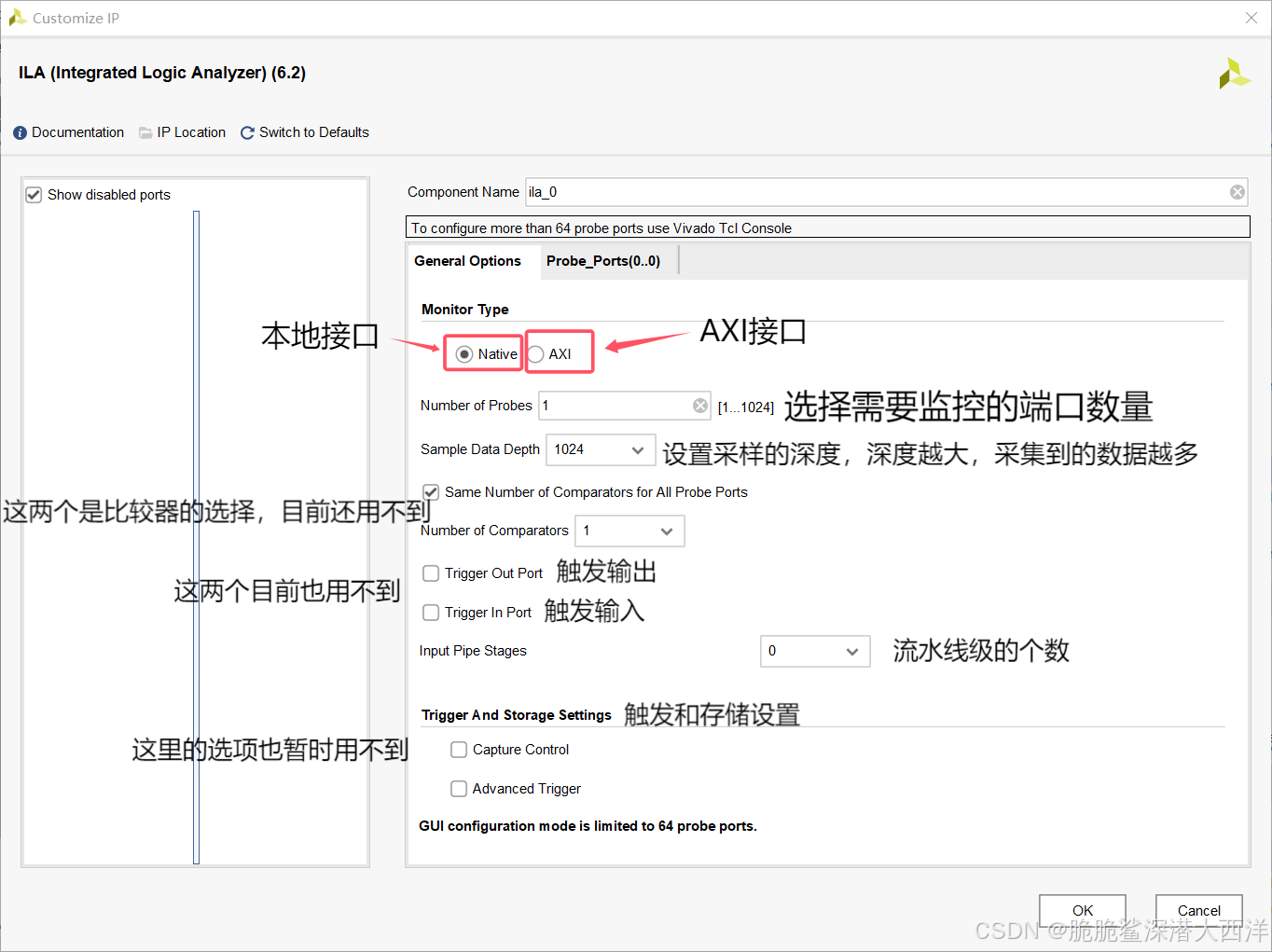

第二步:设置调试配置信息

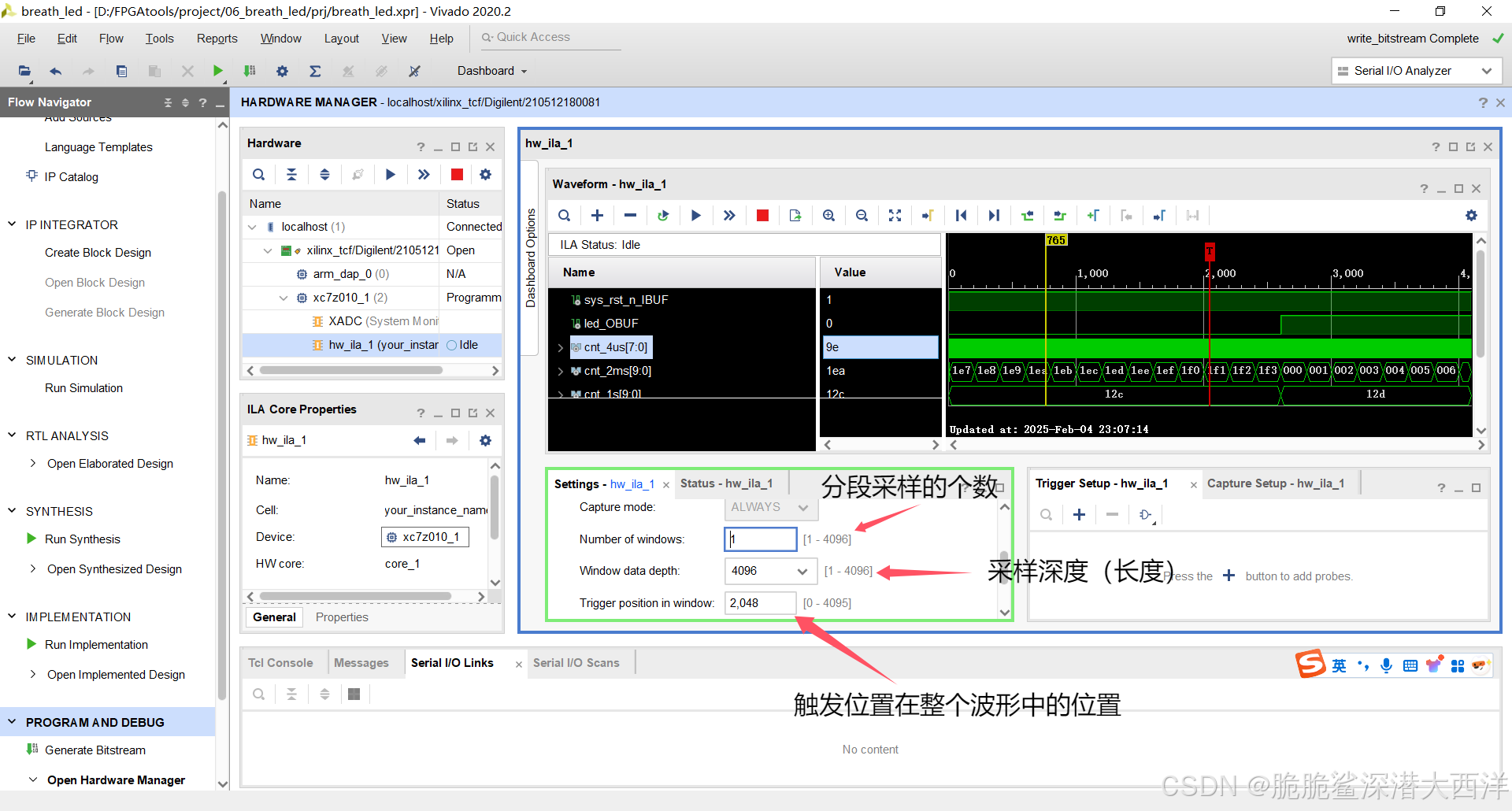

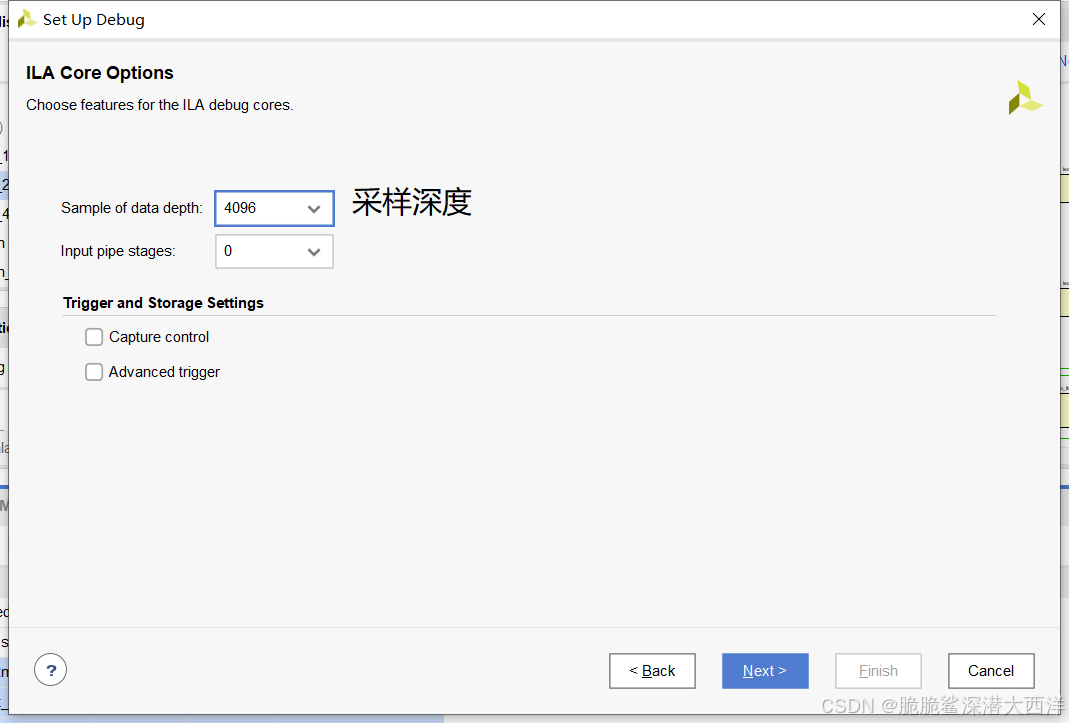

详细的配置页信息如下,需要注意的是,采样的深度越多,所消耗的资源数量就越多。对于呼吸灯实验,监控的端口数量为6(因为sys_clk不需要监控),采样深度为4096。

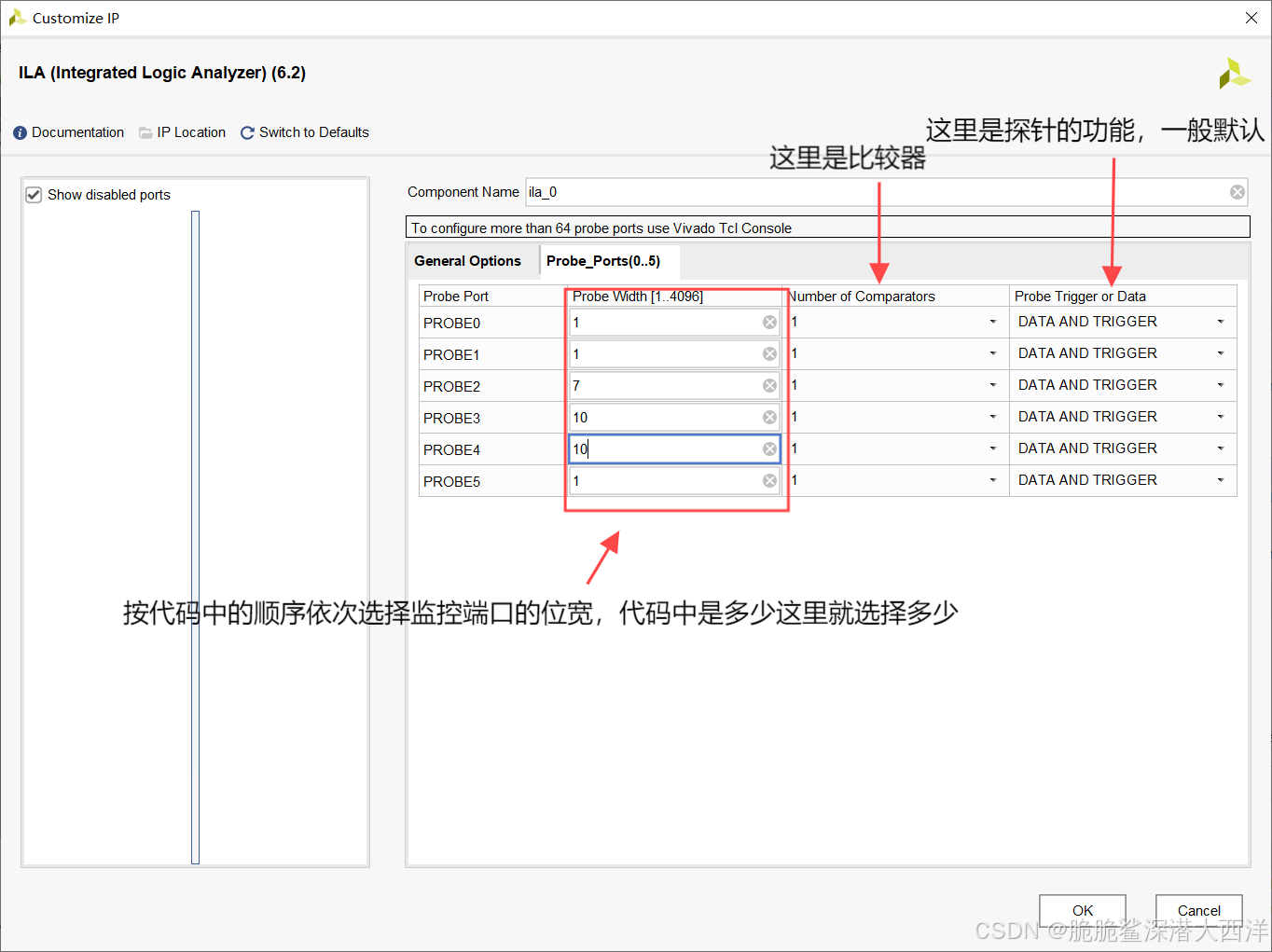

在第二个页面依次选择所需监控的端口的位宽,按照代码中的编写顺序和规定位宽来进行选择。完成后选择“OK”。

‘’

‘’

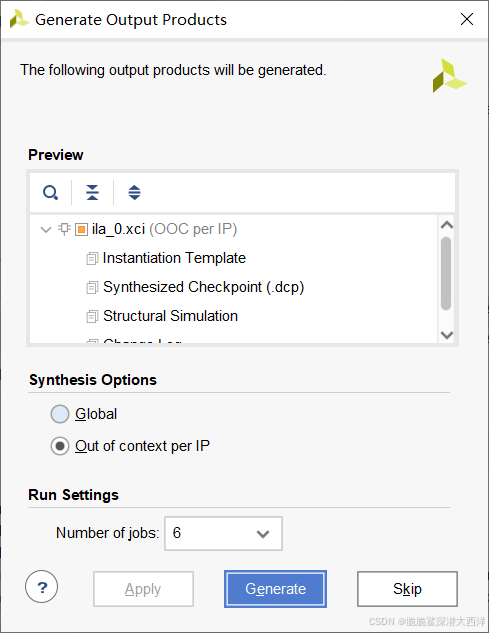

接着弹出此页面,编译选项包含 “Global” 和 “Out of context per IP”,区别为:选择 “Out of context per IP” 会将IP核作为一个独立的模块进行编译,并且生产独立的网表文件,在后续生成比特流文件时,就会省略掉对ILA IP核的编译过程,可以节省时间。如果选择 “Global” 则每次都会对IP核进行全编译,耗时比较长。

“Number of jobs” 是核心数,一般选择默认。

第三步:例化ILA IP核

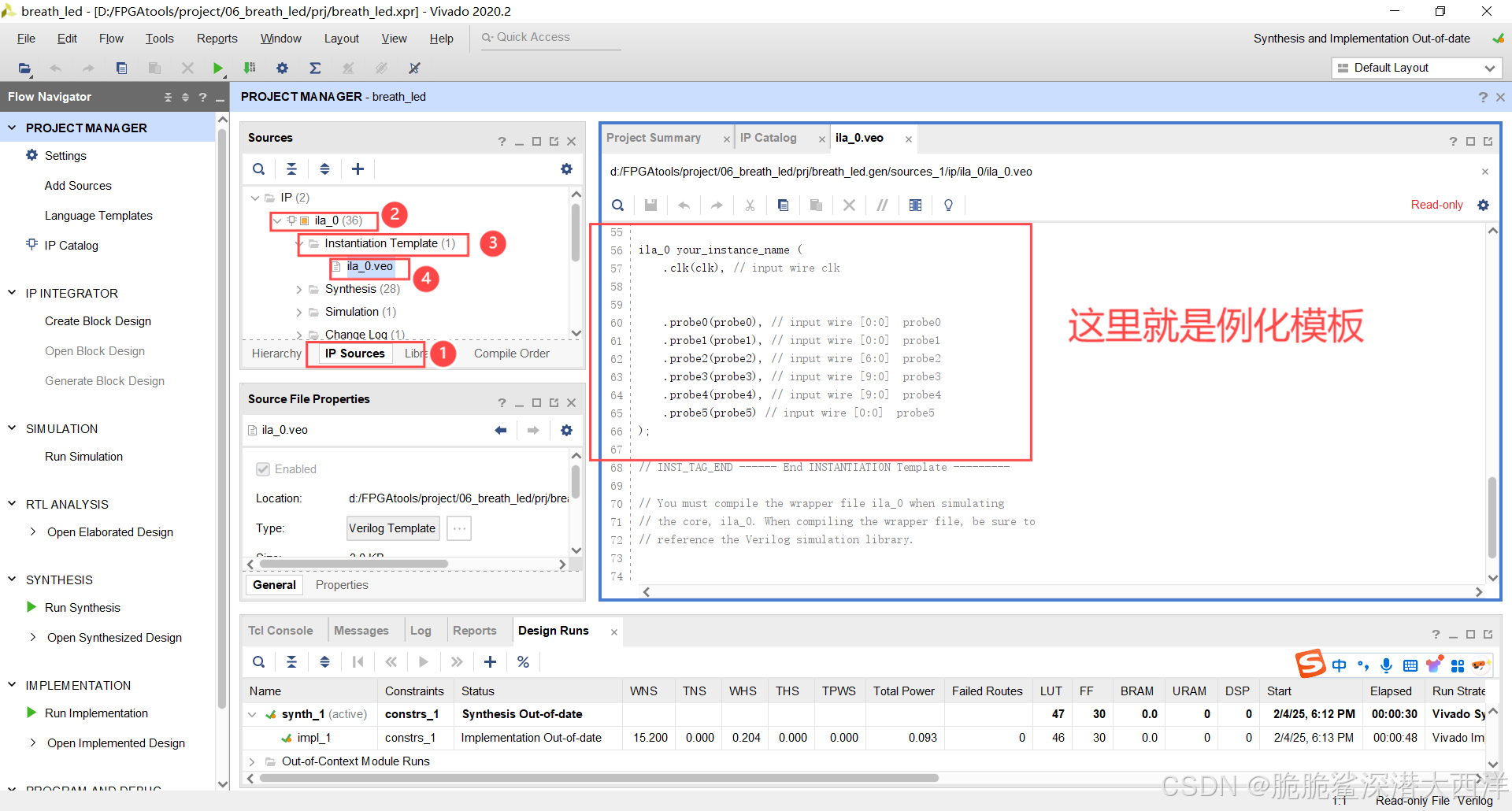

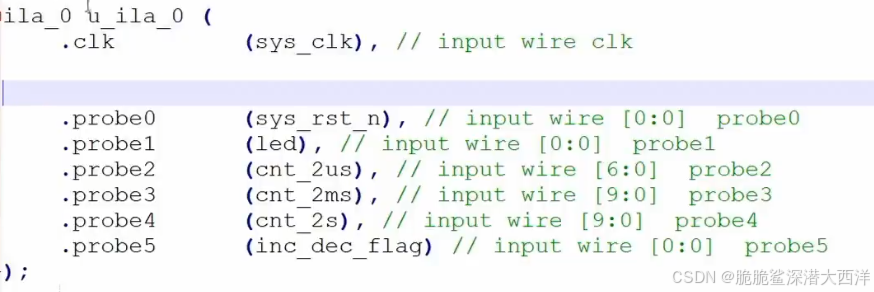

生成完成后,需要对IP核进行例化,操作步骤如下图所示,找到例化模板,并将模板复制到代码中,将括号中的内容更换成所需监控的端口即可,注意 clk 也要换成代码中定义的系统时钟。

举例如下:

第四步:重新生成比特流文件

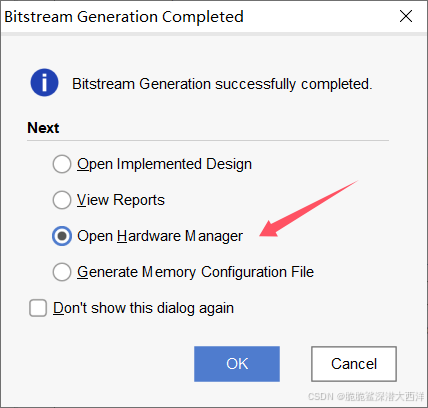

之后开始生产比特流文件,完成后选择打开硬件管理。

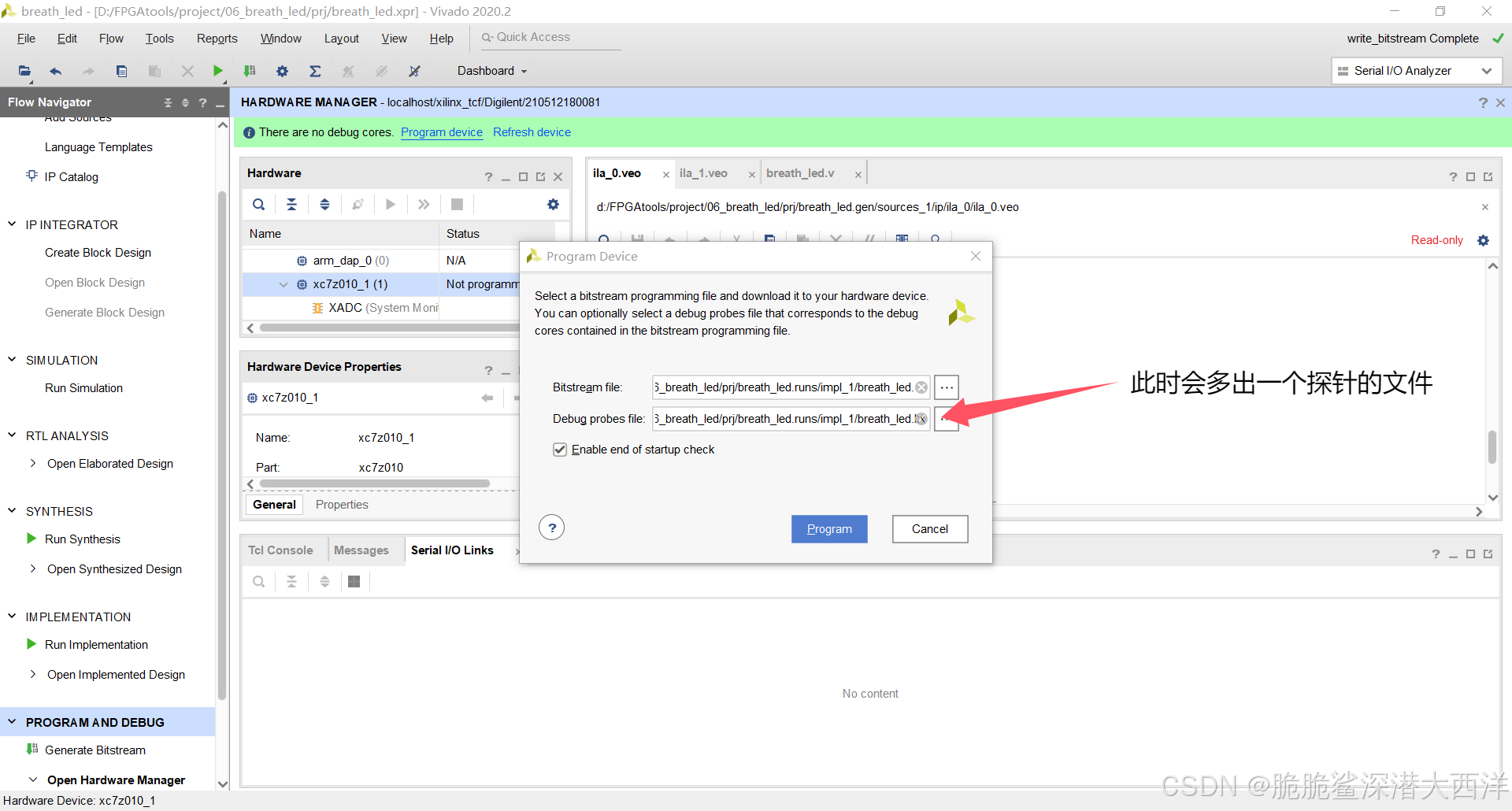

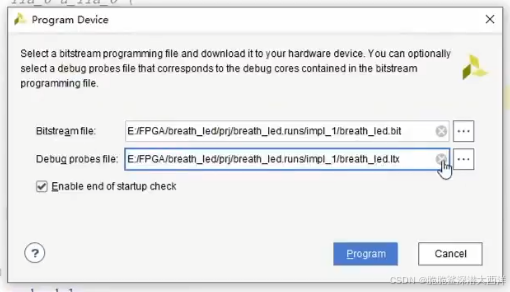

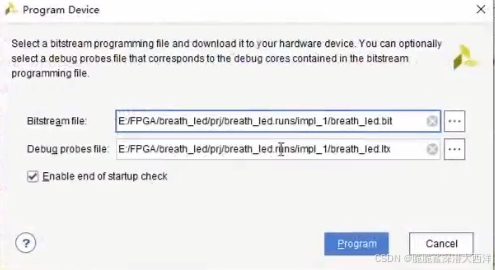

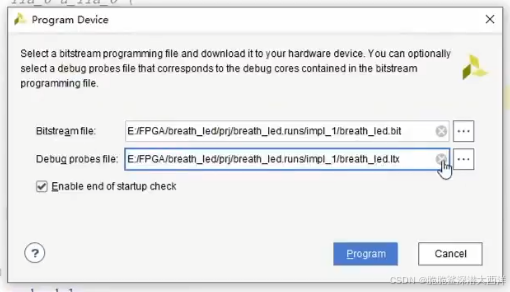

连接好硬件进行下载,下载界面会多出一个探针文件。

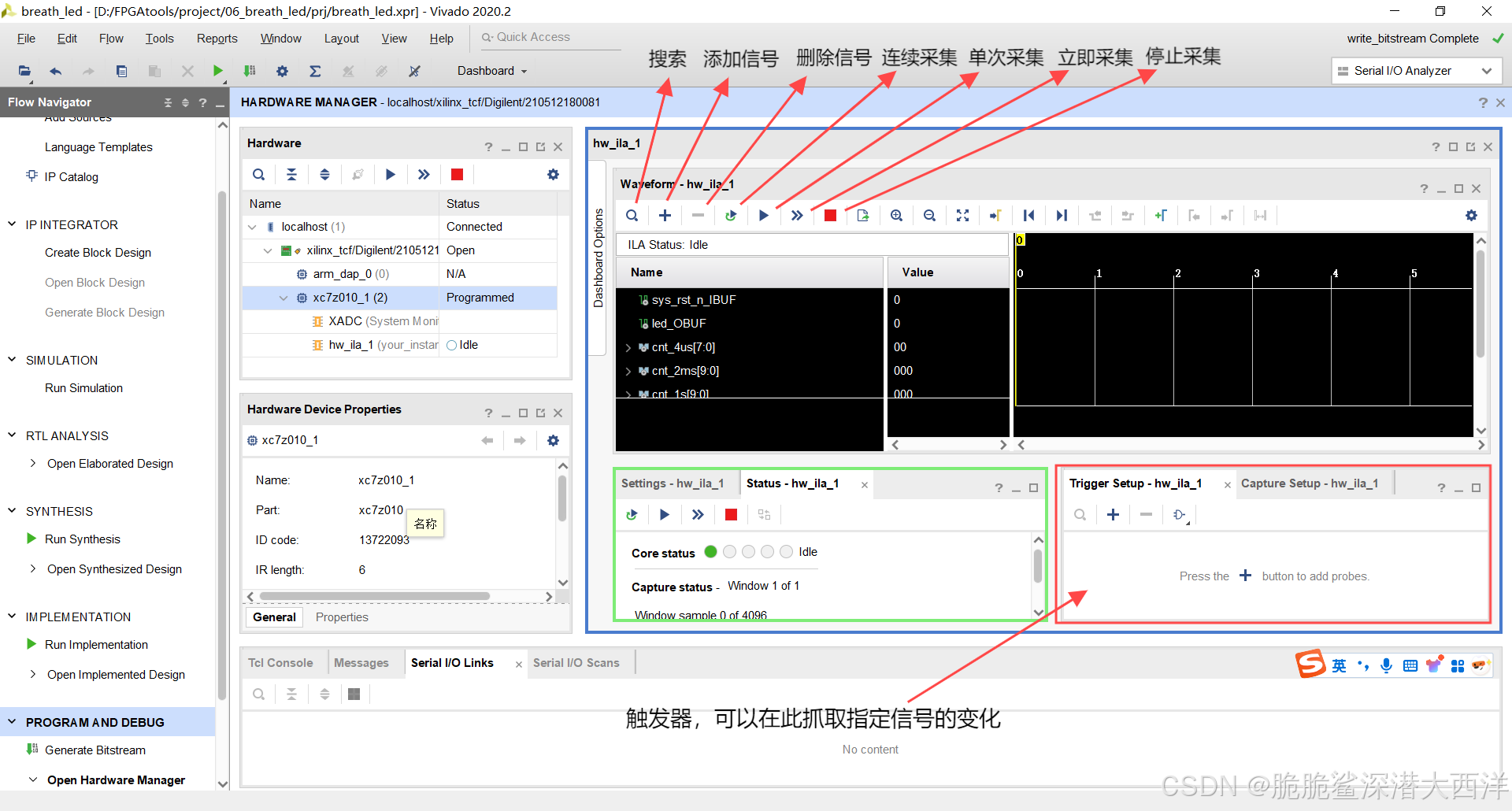

右键信号可以更改显示使用的进制等,对波形图按住鼠标左键,左滑就是缩小,右滑是放大,以下是部分功能介绍。

输入信号和输出信号分别会在变量名后加上新的后缀IBUF和OBUF。

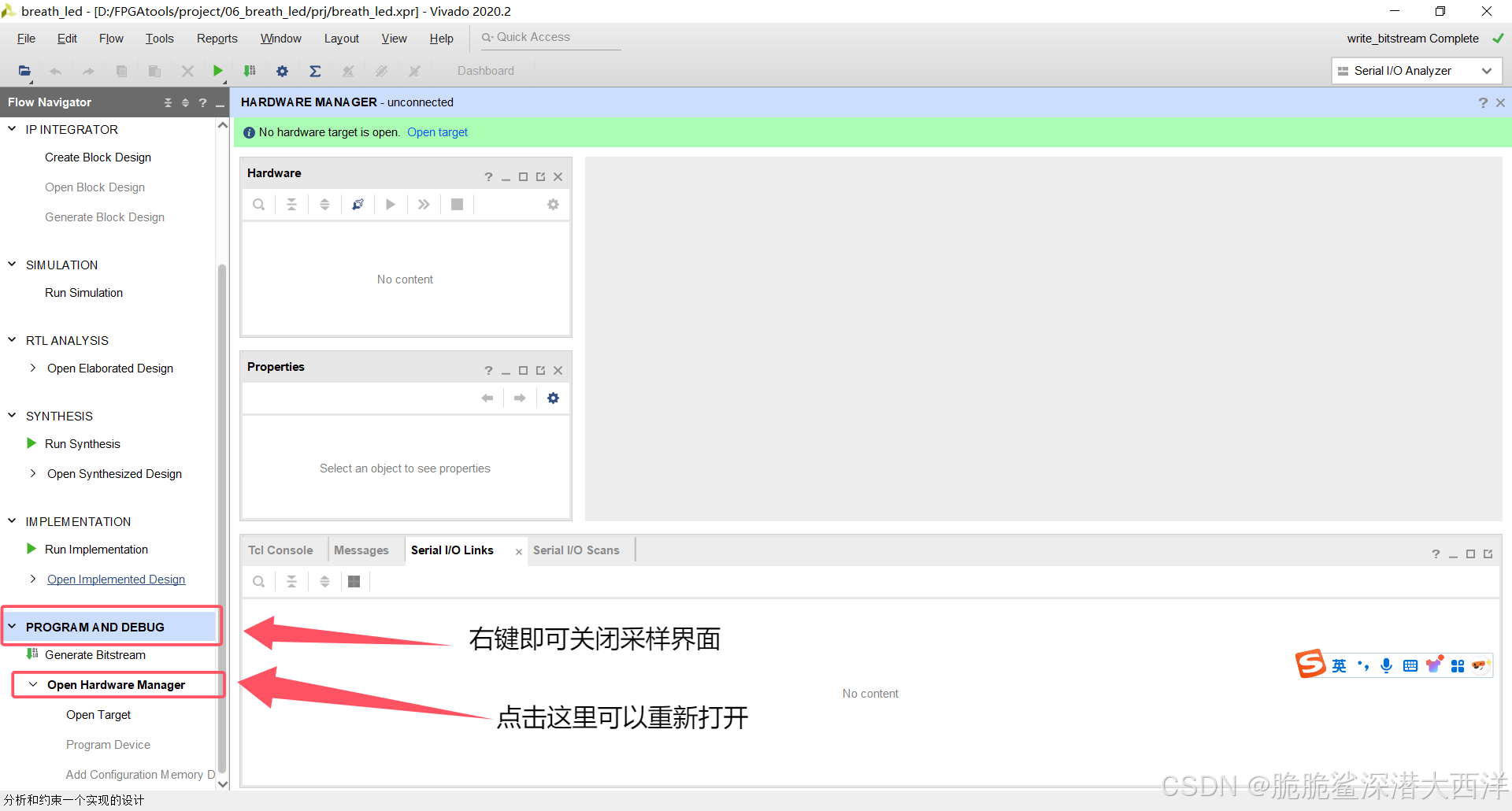

最后,关闭和重新打开采样界面的方法如下:

关闭后在此查看资源占用情况,可以看到ILA IP核占用了很多资源。 调试完成后可以在代码中将ILA IP的实例化部分代码注释掉并重新生产比特流文件以减少资源占用。如果再次下载程序到开发板上时仍然包含了探针文件路径,删掉即可。

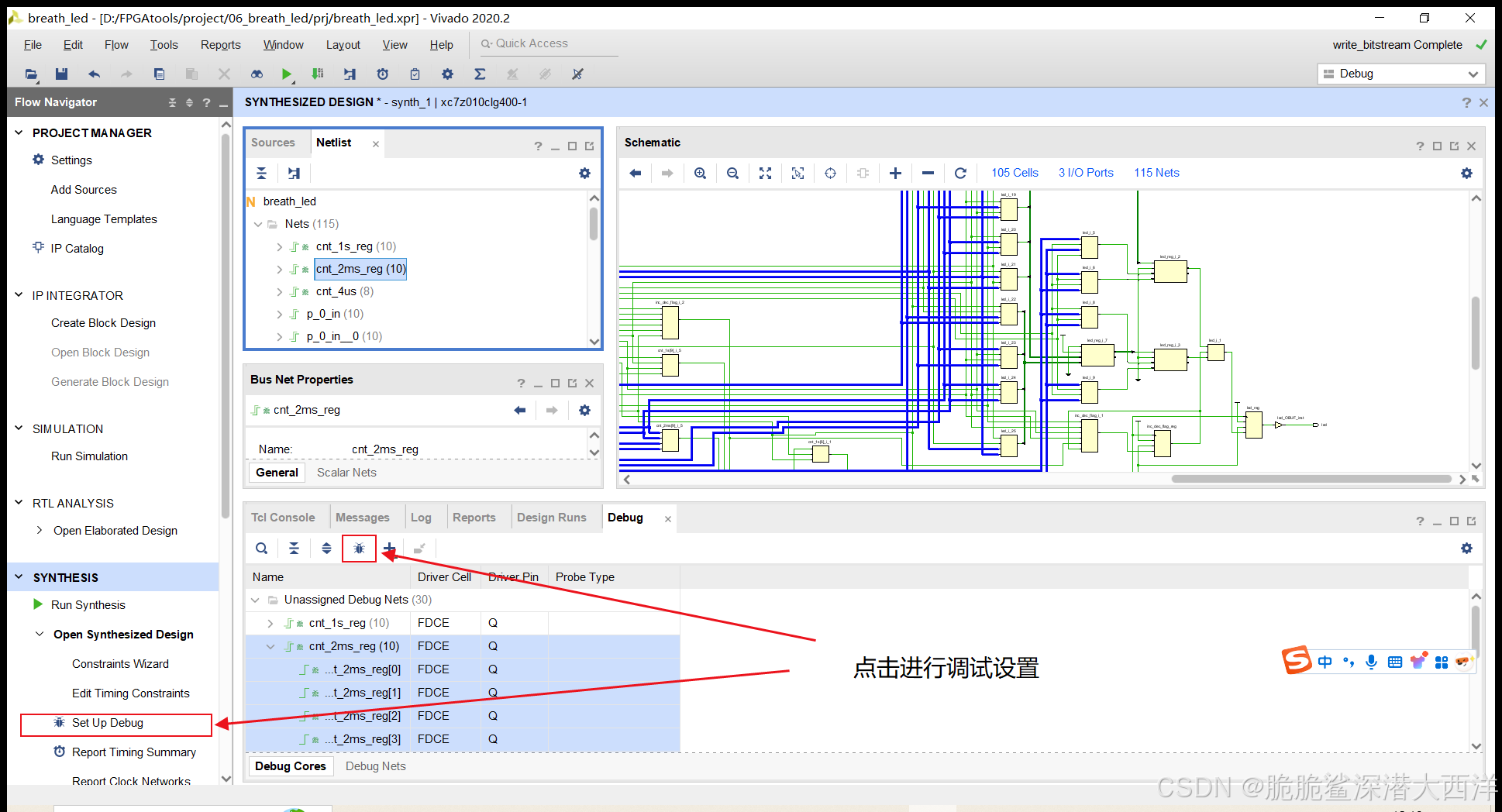

方法二:原理图或者网表文件中添加“mark debug”属性

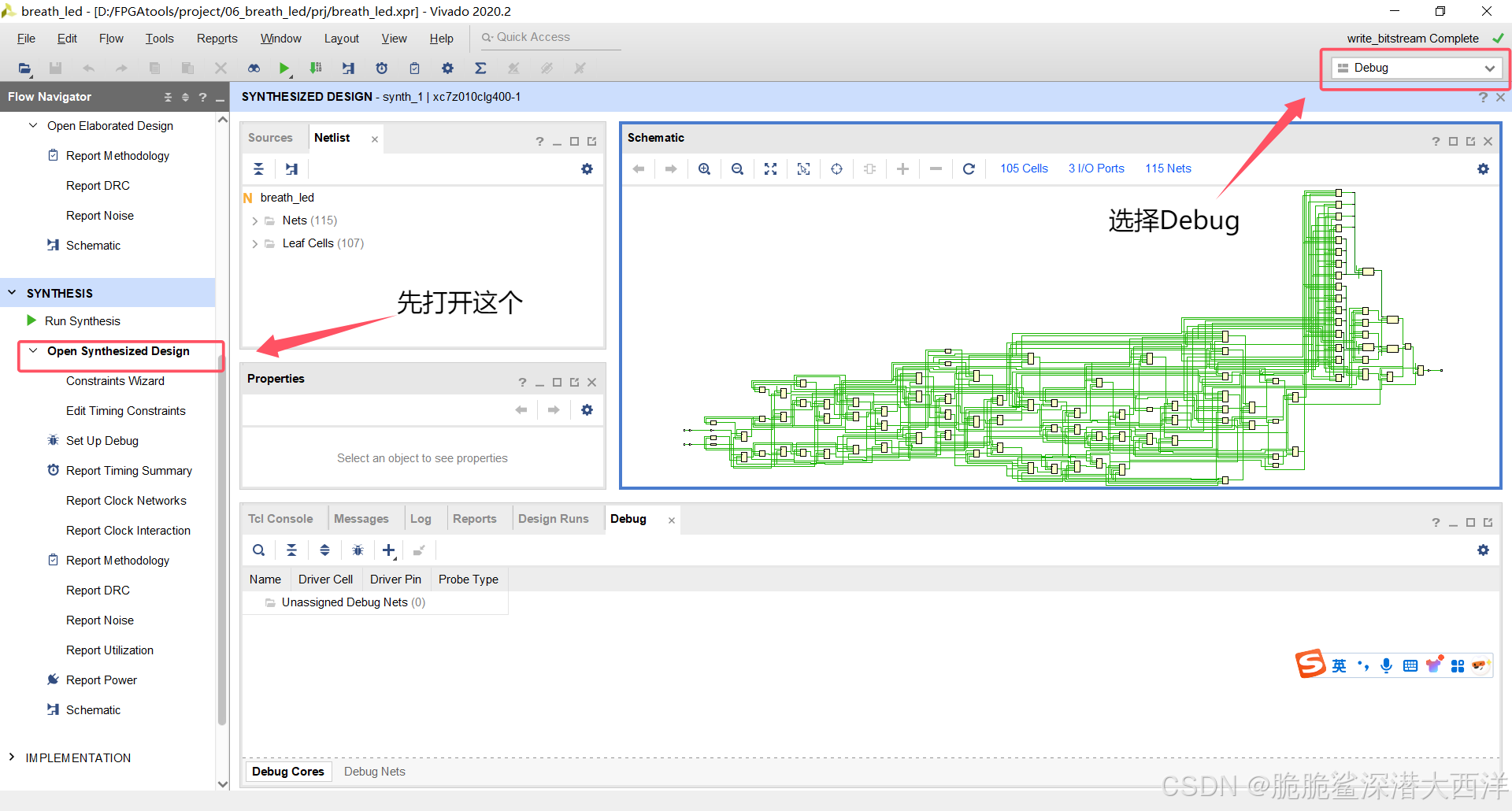

第一步:打开综合设计界面

第二步:添加需要调试的信号

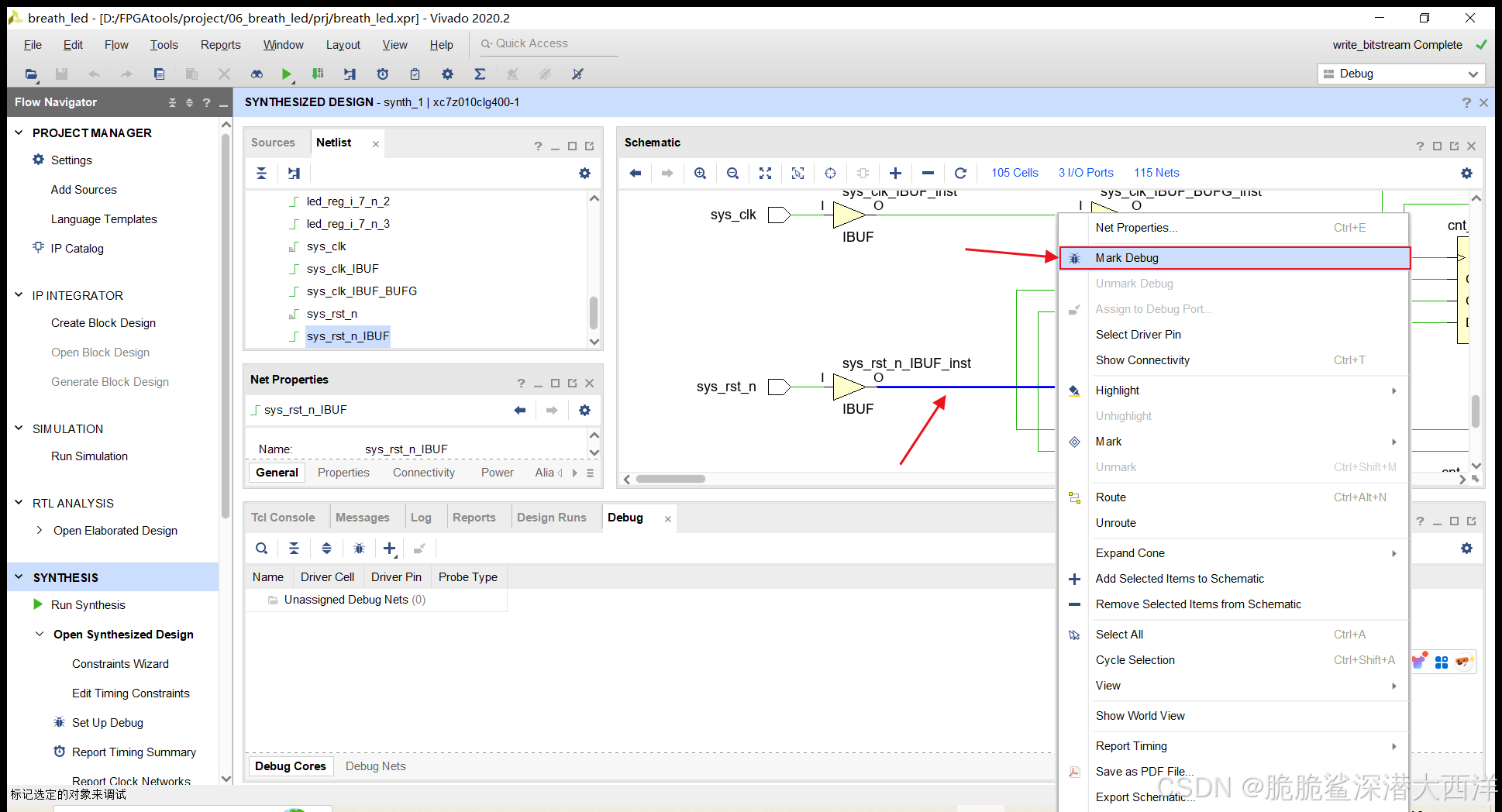

放大后在这根线上可以添加Mark Debug,这里解释一下为什么不从前面那根线进行抓取。因为被抓取的信号需要是内部逻辑信号(内部逻辑信号才是FPGA内部实际处理的输入值),外部的电平输入要先经过缓冲(或者说是IBUF)处理后才是内部逻辑信号。

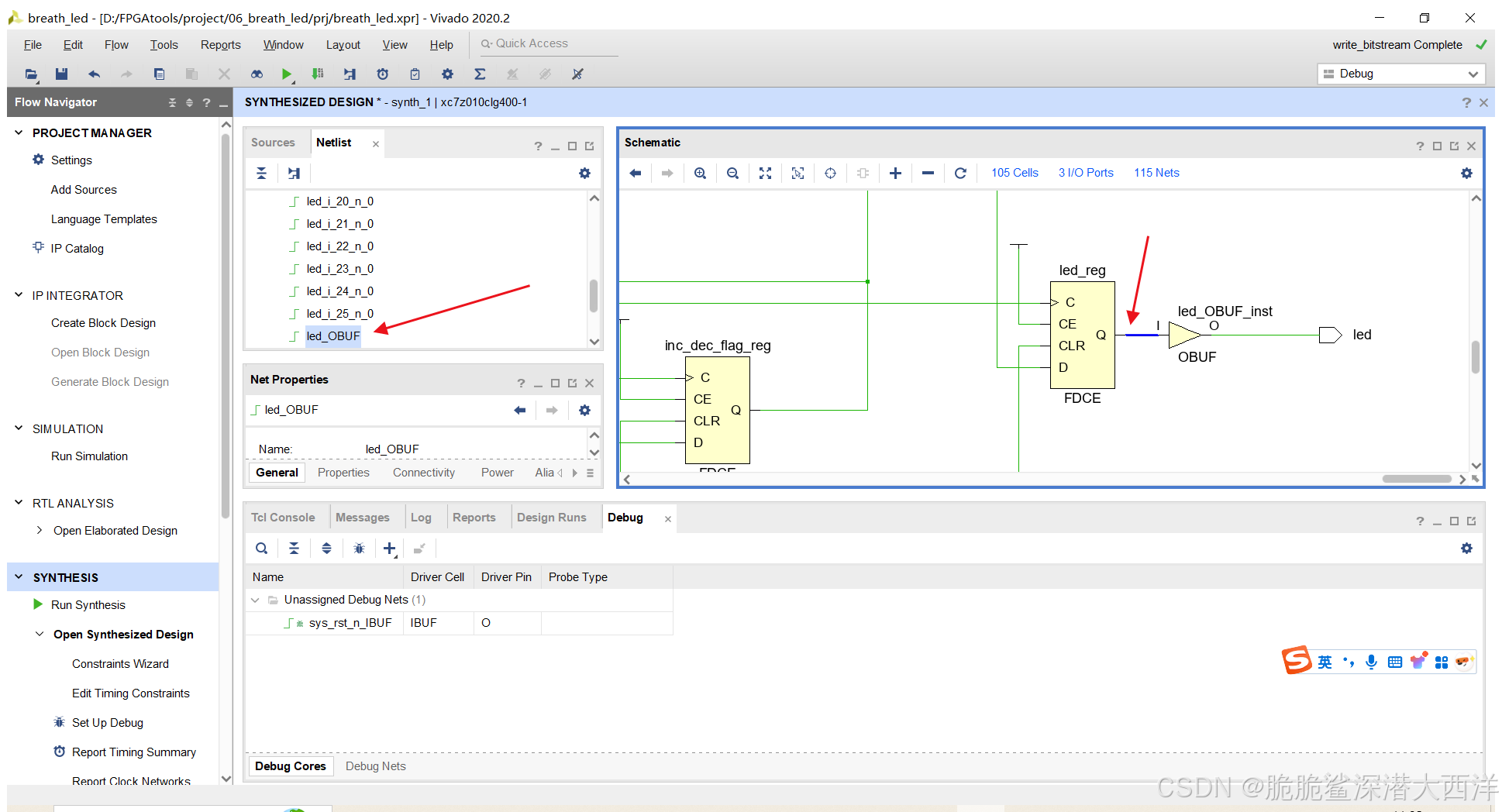

同理,给输出信号设置 Mark Debug 时,也需要是OBUF信号。这里解释一下为什么不是后面那根线:OBUF的作用:输出缓冲器将内部逻辑生成的电平转换为适合驱动外部负载(如 LED、显示屏)的电平,并增强驱动能力。OBUF的作用也可以从下图左侧红色箭头指向的地方看出。

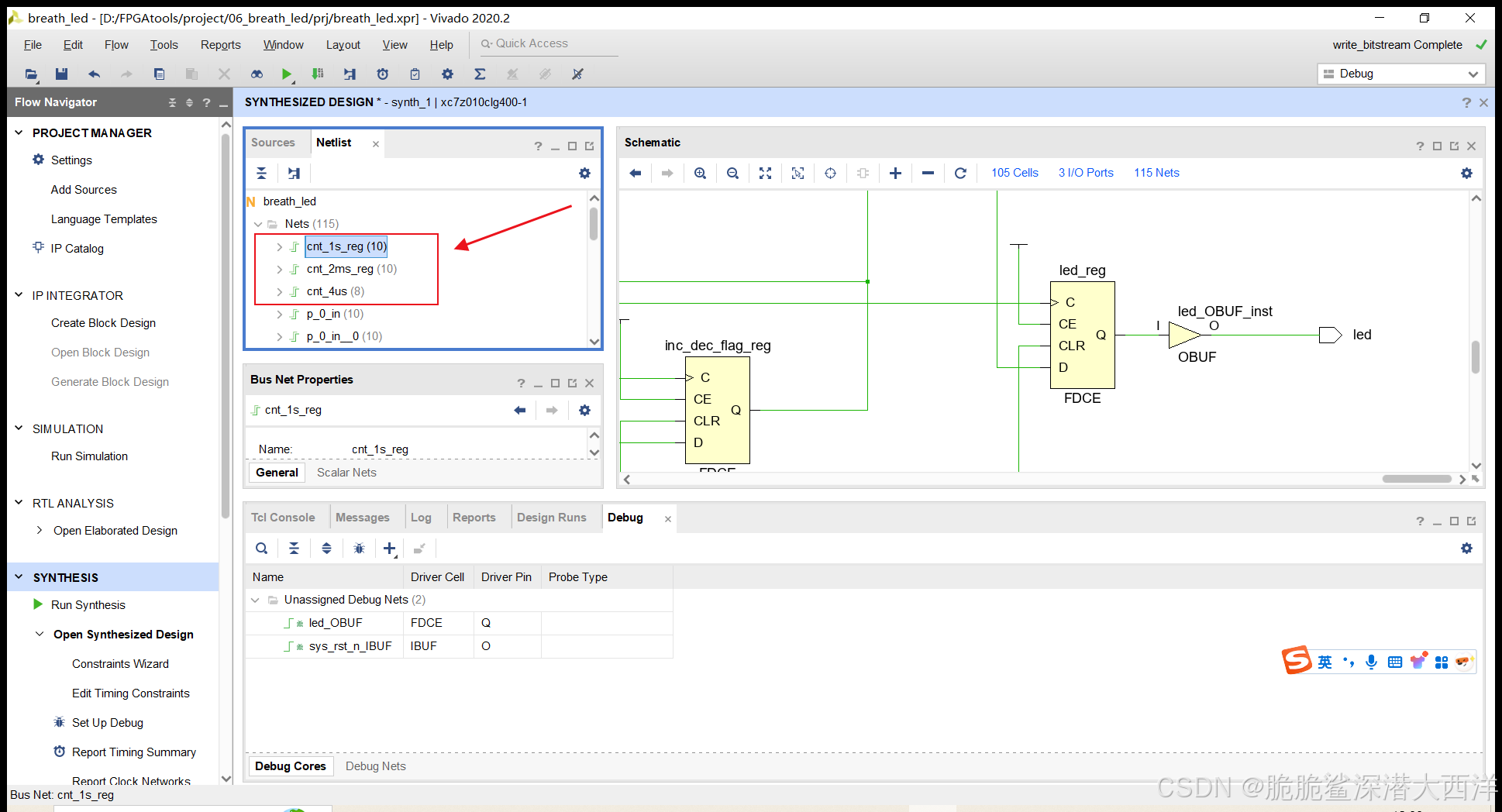

一些在网表文件中难以寻找的对象,如多位宽的计数器,可以在下图标记的地方进行添加。

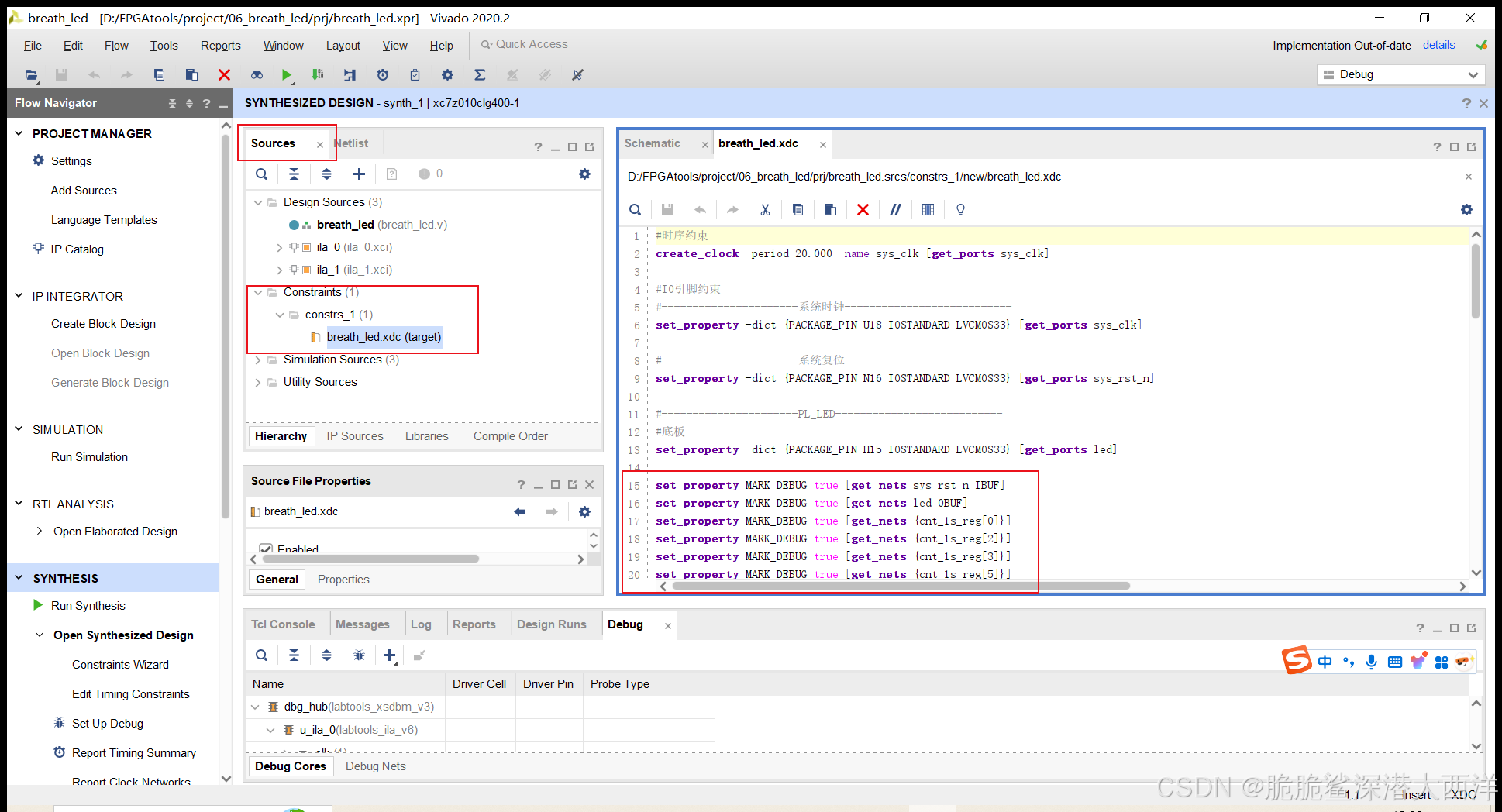

另外需要注意的是,软件在有些时候会对信号进行优化,比如8位宽的信号优化到7位宽。此时若是需要对原本8位宽的信号进行调试的话,可以在代码中对应的信号定义处添加(*mark_debug="true"*)来防止此信号被优化更改。更改完成后重新进行综合即可。

(*mark_debug="true"*)reg [9:0] cnt_2ms;第三步:进行调试设置

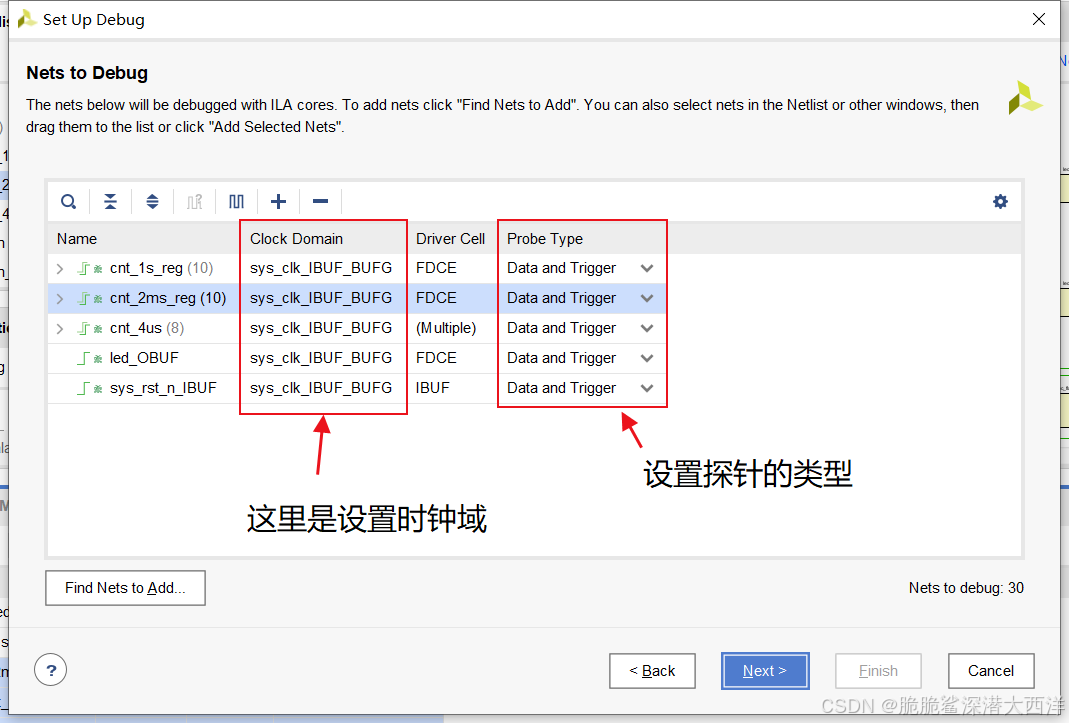

点击标记处可打开调试设置。

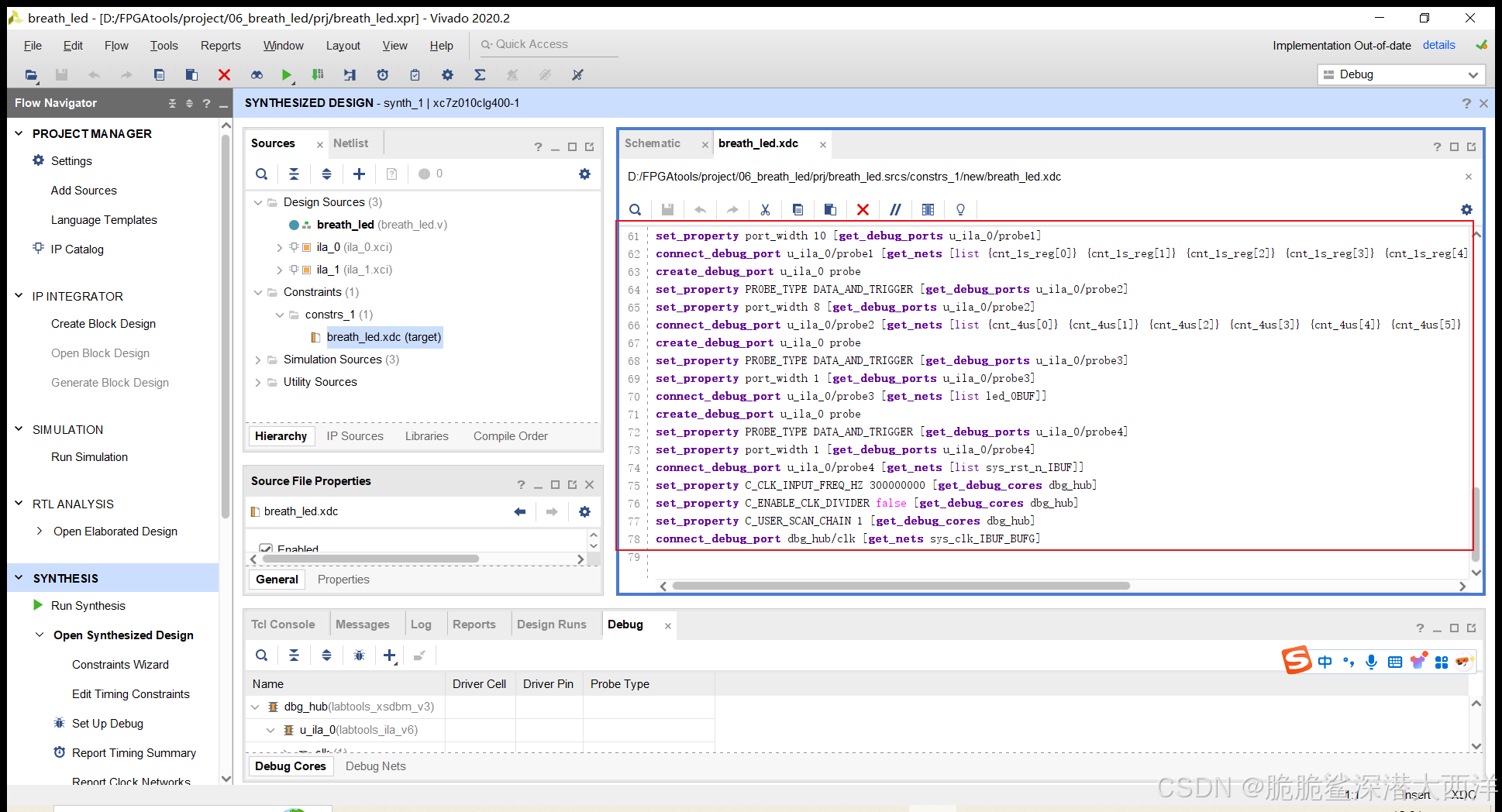

界面选项与使用ILA IP核类似。点击下一步后即可选择完成。完成后记得“ctrl+s”保存一下。

第四步:重新生成比特流文件

最后重新生产比特流文件,连接开发板进行下载,同样会识别到调试信息文件,后续操作与方法一一致。

取消调试

完成调试后,想要取消调试需要打开配置引脚的那个XDC文件,把下面的调试信息删除(代码中添加的调试相关代码也最好删除掉),再重新生成比特流文件下载即可。

注意下载时也要清除掉调试文件(即“Debug probes files”)。

1777

1777

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?