目录

1. 简介

1.1 VIO的功能

Xilinx VIO(Virtual Input/Output)IP核是一种基于硬件的实时调试工具,能够在不重新综合设计的情况下,动态监控和修改FPGA内部的信号值。其核心功能包括:

实时观测信号: 通过JTAG接口将内部信号实时输出到Vivado硬件管理器中。

动态控制信号: 通过虚拟输入端口(如按键、寄存器)修改FPGA内部信号的状态,触发特定操作。

简化调试流程: 无需添加额外的物理IO引脚或修改代码即可完成调试。

VIO尤其适用于以下场景:

- 实时监控状态机、计数器、标志位等关键信号。

- 动态调整参数(如PWM占空比、滤波器系数。

- 触发异常条件以验证系统的鲁棒性。

1.2 本文知识点

本文将从以下方面详细讲解VIO的使用:

- VIO IP核的配置: 关键参数说明与生成流程。

- 在线调试操作: Vivado硬件管理器中的VIO界面详解。

- 常见问题与解决方法: 信号不更新、触发失效等典型问题排查。

2. VIO IP核的配置

VIO IP核的配置分为参数设置和信号绑定两步,本节以Vivado 2022.2为例进行说明。

2.1 添加VIO IP核

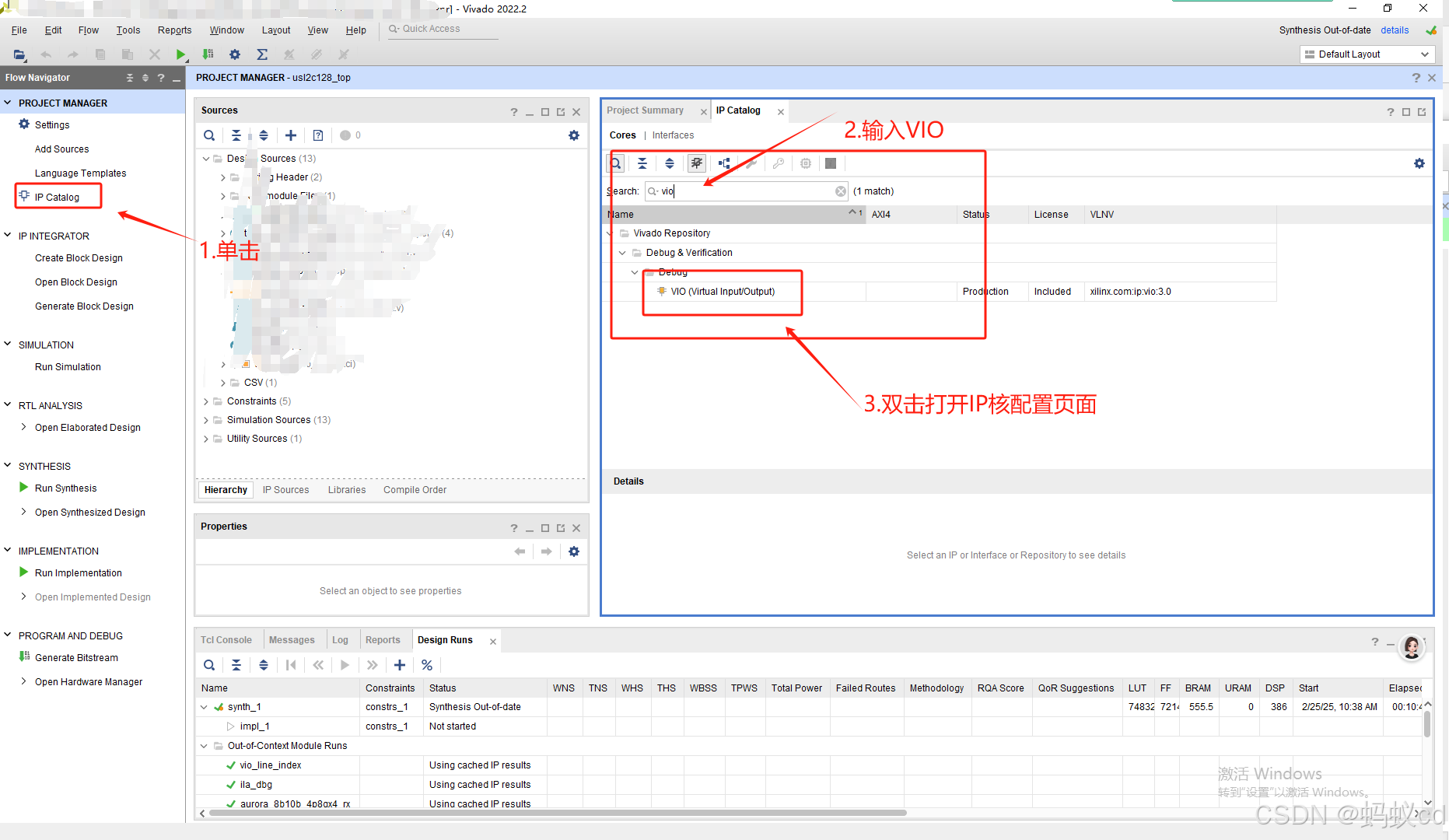

-

在Vivado工程中打开IP Catalog,搜索并双击“VIO (Virtual Input/Output)”,如下图。

-

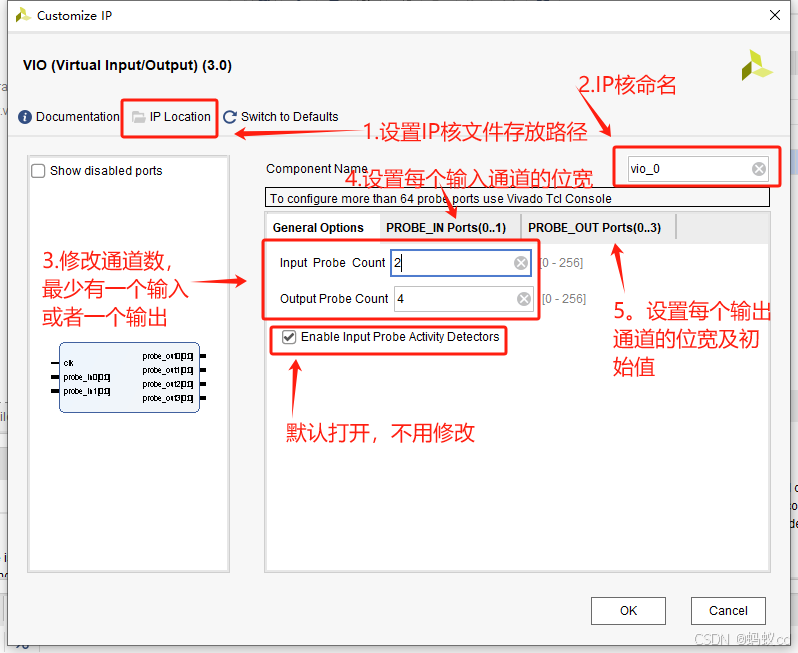

弹出配置窗口后,按需设置以下参数:

- General Options:

- Input Probe Count: 输入通道数。

- Output Probe Count: 输出通道数。

- Enable Input Probe Activity Detectors: 输入信号变化检测器(检测到输入信号变化时提示)

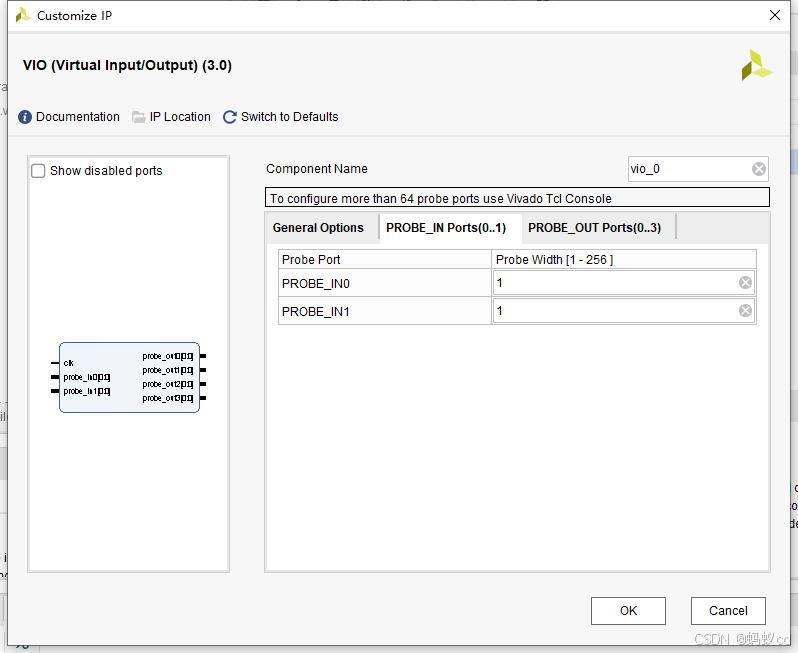

- PROBE_IN Ports:

- Probe Prot: 通道名称

- Probe Width: 设置每个通道的数据位宽。

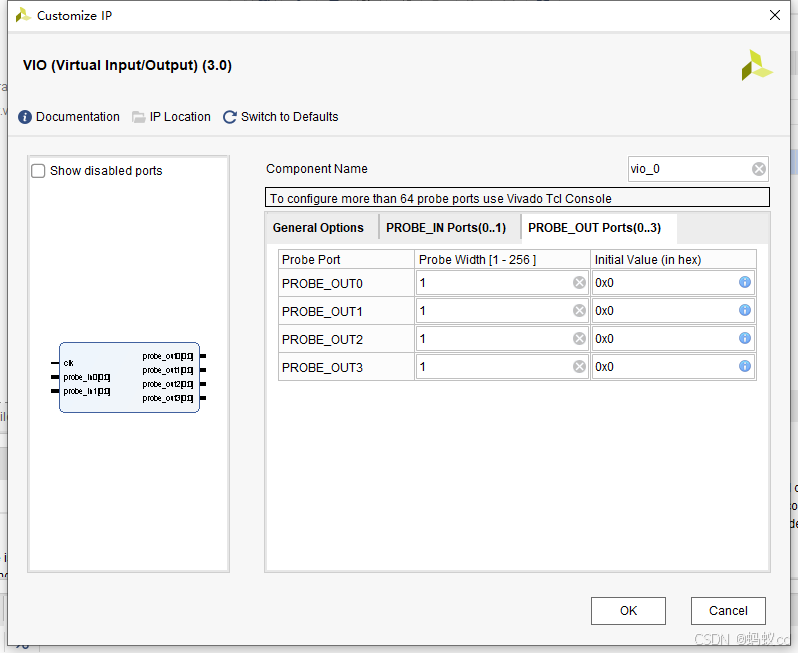

- PROBE_OUT Ports:

- Probe Prot: 通道名称

- Probe Width: 设置每个通道的数据位宽。

- Initial Value (in hex): 十六进制的初始值。

2.2 信号绑定

生成IP核后,需在顶层模块中实例化VIO并连接信号:

vio_0 your_vio_inst (

.clk(clk_50M), // 输入时钟(必须与调试时钟同步)

.probe_in0(counter), // 监控的计数器信号

.probe_out0(enable) // 输出的控制信号(如使能信号)

);

2.3 关键参数解析

- 时钟clk: VIO的时钟必须与监控信号所在时钟域一致,否则可能导致采样错误。

3.在线调试

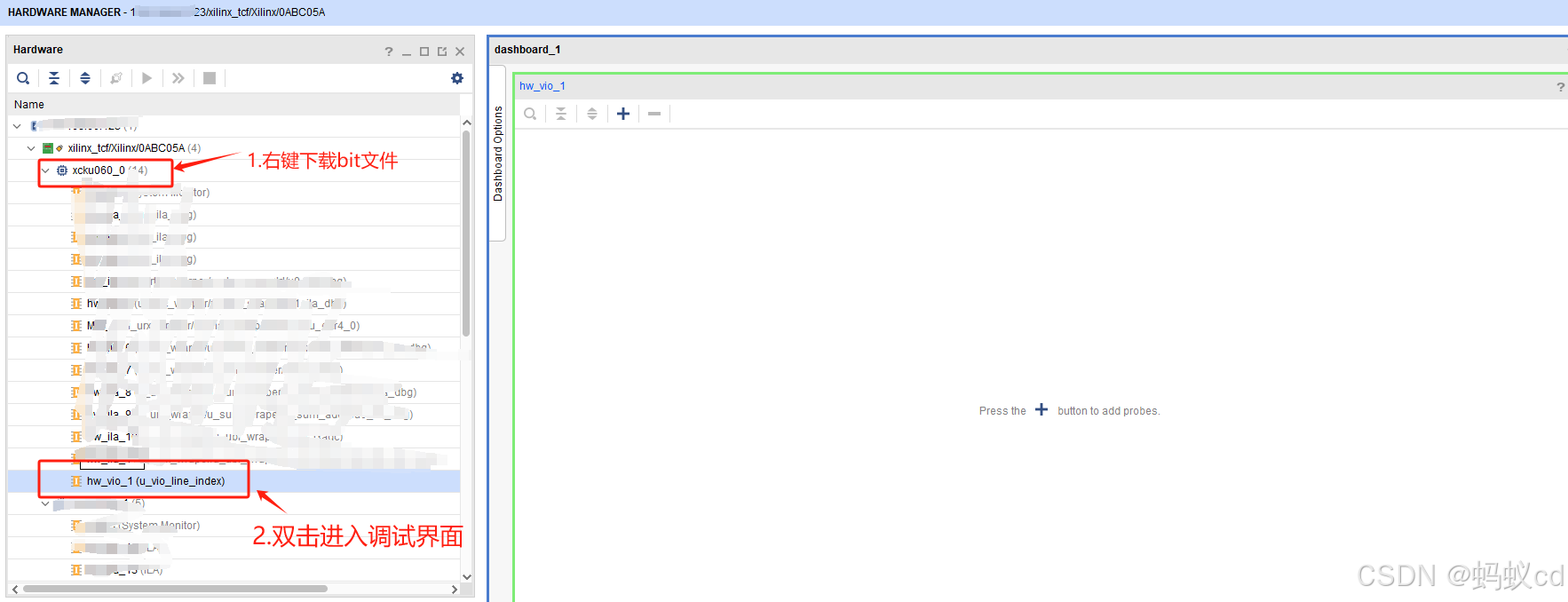

3.1 下载程序并连接硬件

生成比特流文件后,通过“Open Hardware Manager”连接FPGA开发板。

下载比特流(.bit文件),确保VIO逻辑已加载到FPGA中。

3.2 界面功能详解

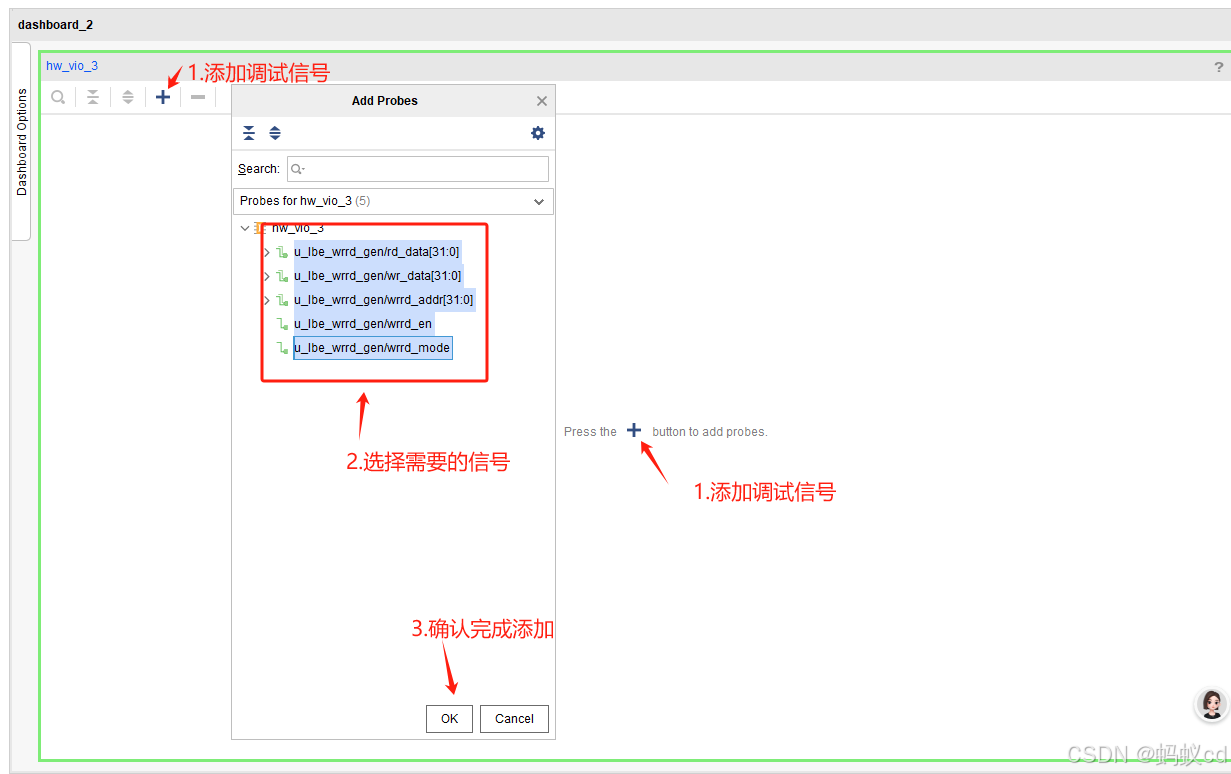

- 添加调试信号

- 信号显示窗口介绍

- Name: 信号名称。

- Value: 值,对输入/输出信号分别有多种显示方式,详见后文。

- Activity: 当输入信号值发生变化时,用箭头进行指示。

- Direction: 输入/输出方向

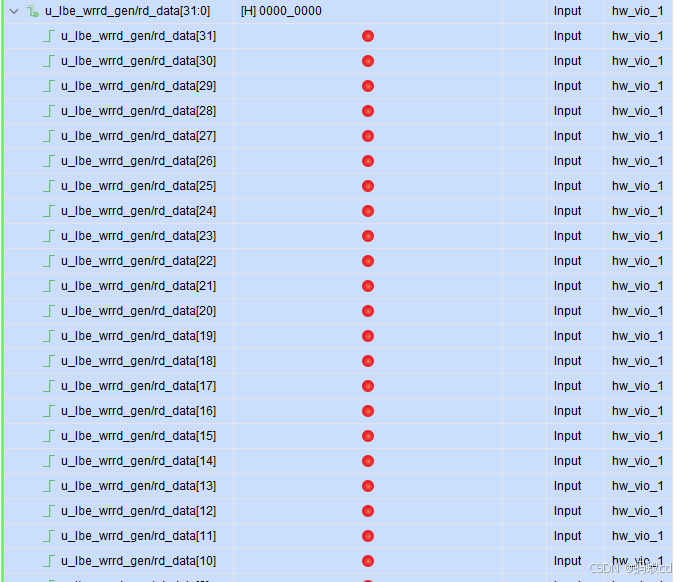

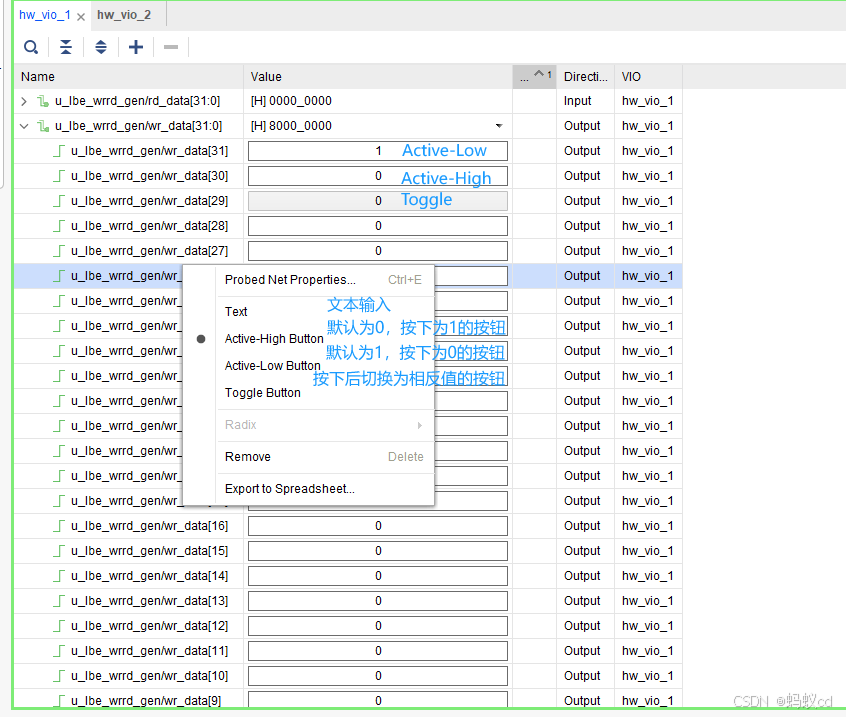

- 输入/显示方式配置

对输入信号 可以选择LED或者TEXT两种方式,LED仅针对单BIT信号(多BIT信号可展开成单BIT信号);

对输出信号可以选择TEXT、常高按钮、常低按钮、切换按钮等几种方式,后面三种仅针对单BIT信号(多BIT信号可展开成单BIT信号)。

多BIT输入信号配置为LED方式显示,输入信号状态对应LED颜色可以配置,展开后可对每个BIT单独配置。

多BIT输出信号配置为按键,展开后也可对每个BIT单独配置。

# 4. 常见问题

# 4. 常见问题

4.1 信号值不更新

可能原因:

- VIO IP核未正确绑定信号。

- 时钟未正确连接或频率过低。

解决方法:

- 确认信号绑定正确。

- 检查VIO实例的时钟是否与监控信号的时钟域一致。

5. 参考文档

- 《UG908-Vivado Design Suite User Guide – Programming and Debugging》

- 《XAPP1234-Advanced Debugging with VIO and ILA》

2310

2310

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?