前言

最近在学FPGA,使用HLS开发,我下载的Vitis2024.2版本,网上关于这个版本的教程很少,正在慢慢摸索中。Vitis 2024.2 将 HLS 和 SDK 功能融合在一起,支持使用 C/C++ 进行硬件设计。本文章主要是介绍了在Vitis中使用HLS组件和C++语言创建一个IP核然后导入到Vivado中使用。

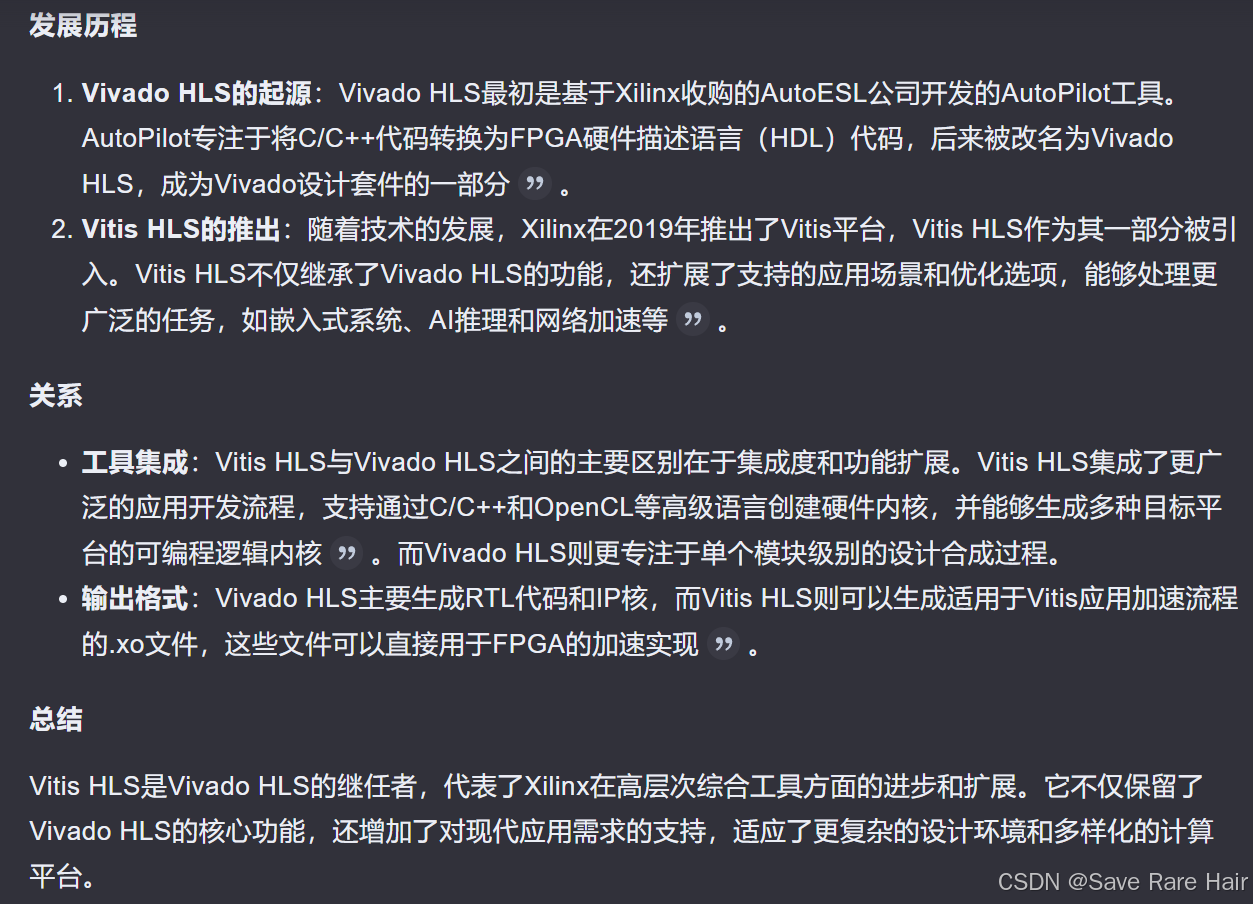

这里附一张Vivado HLS和Vitis HLS的介绍。

工程创建

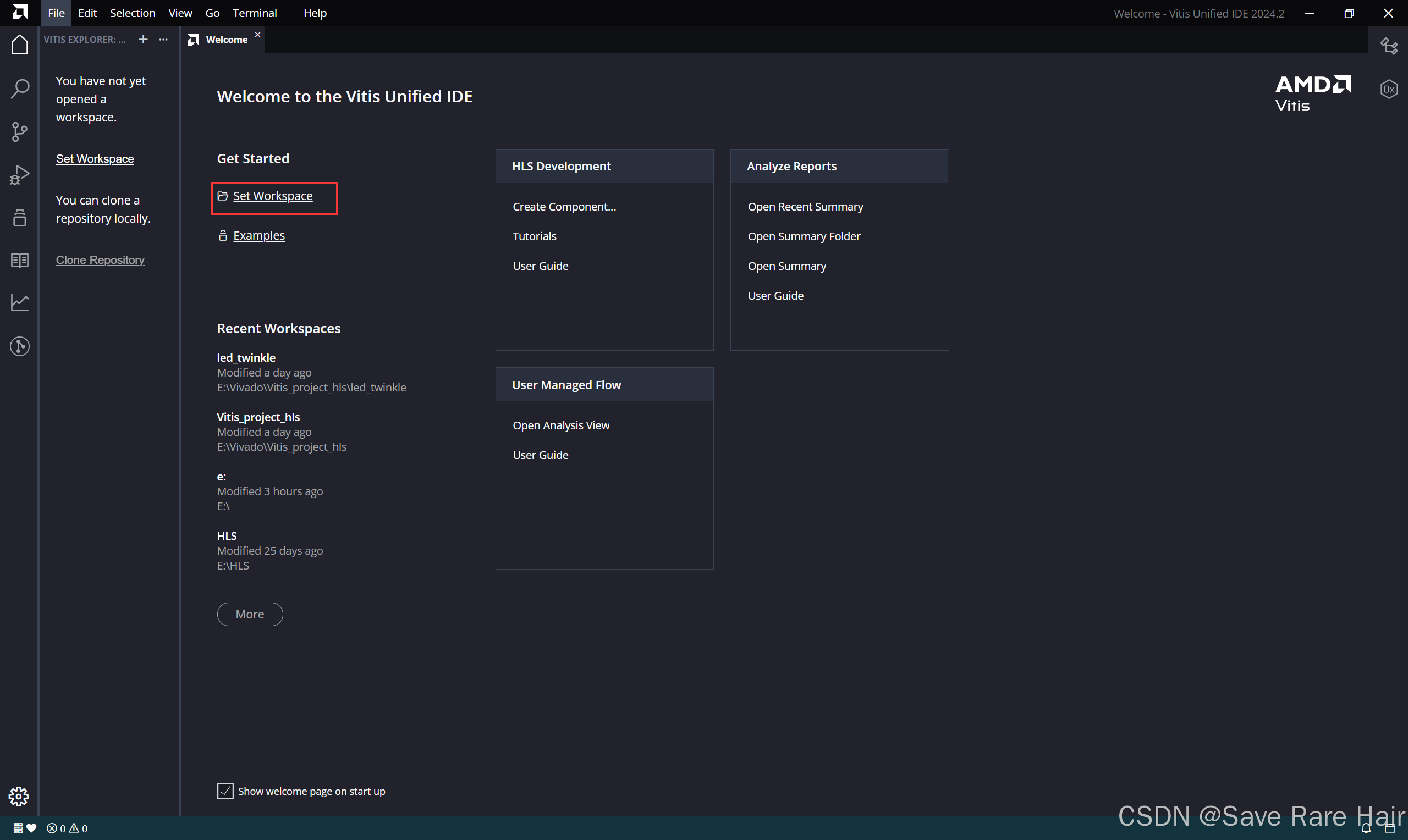

新界面如下图所示,首先需要为你的工程设置一个工作区,后续的工程都可以放到这个工作区内。

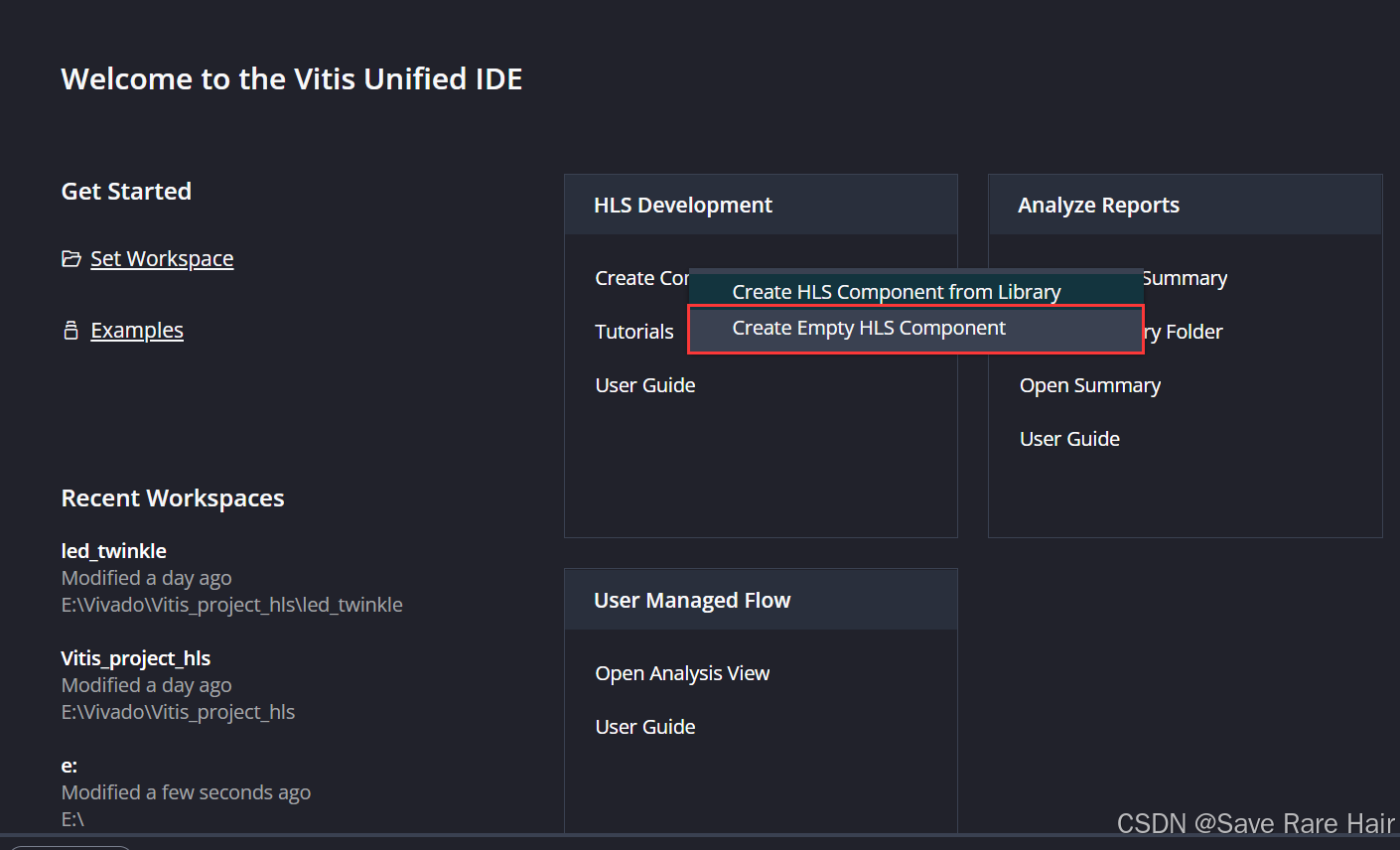

创建一个HLS空白组件

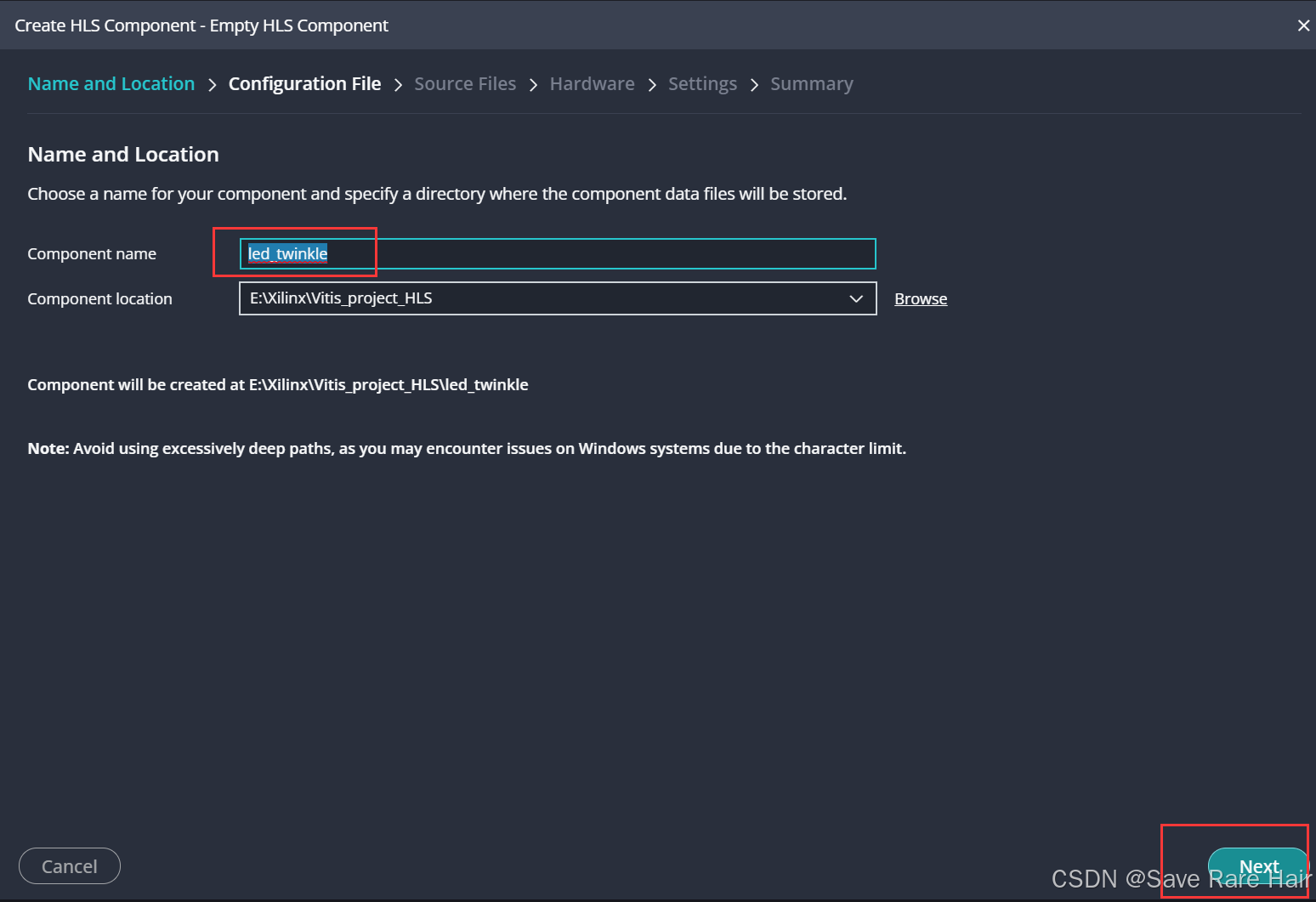

重命名你的组件名称,点击next。

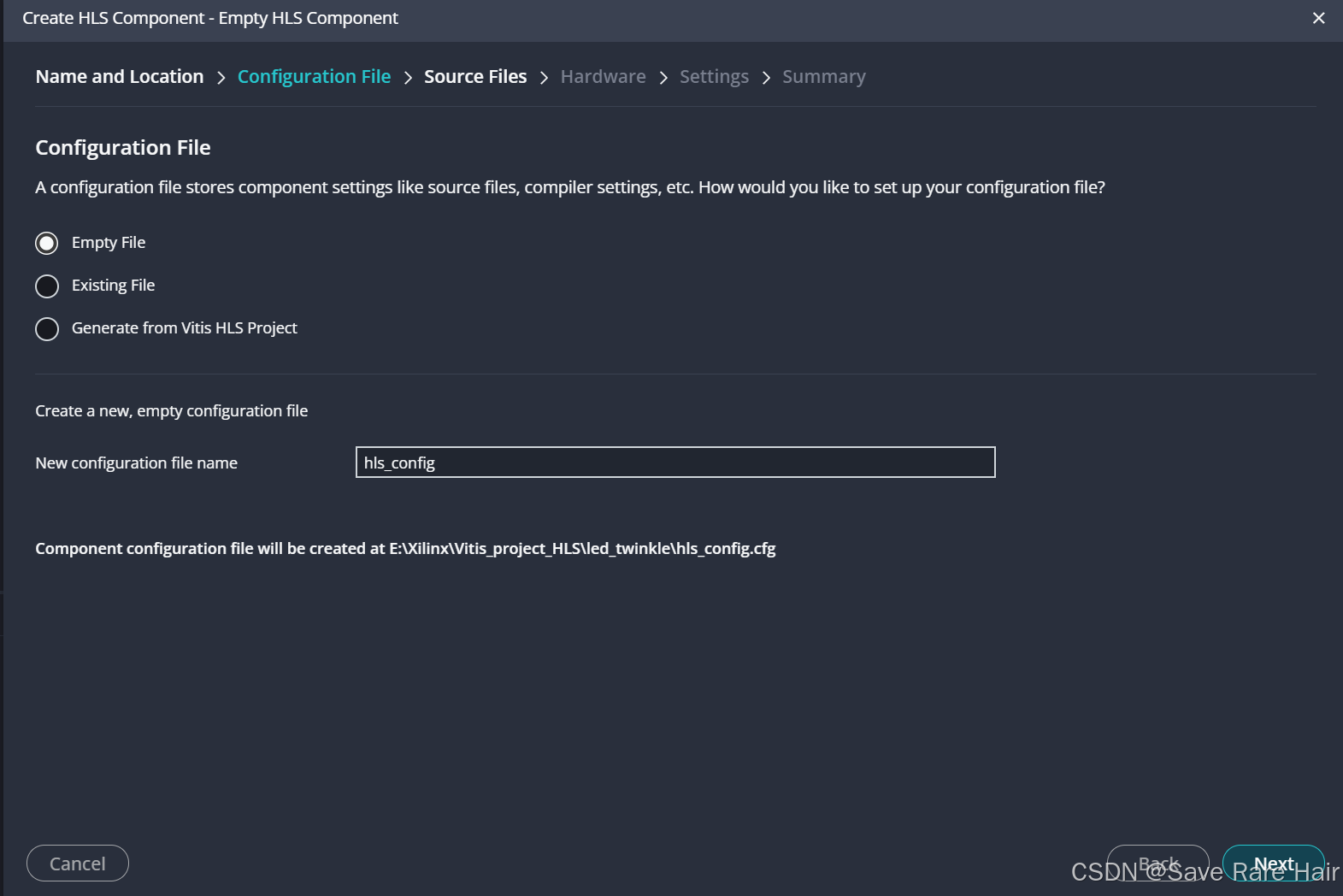

这里默认就好,后面会生成一个可修改的配置文件hls_config。

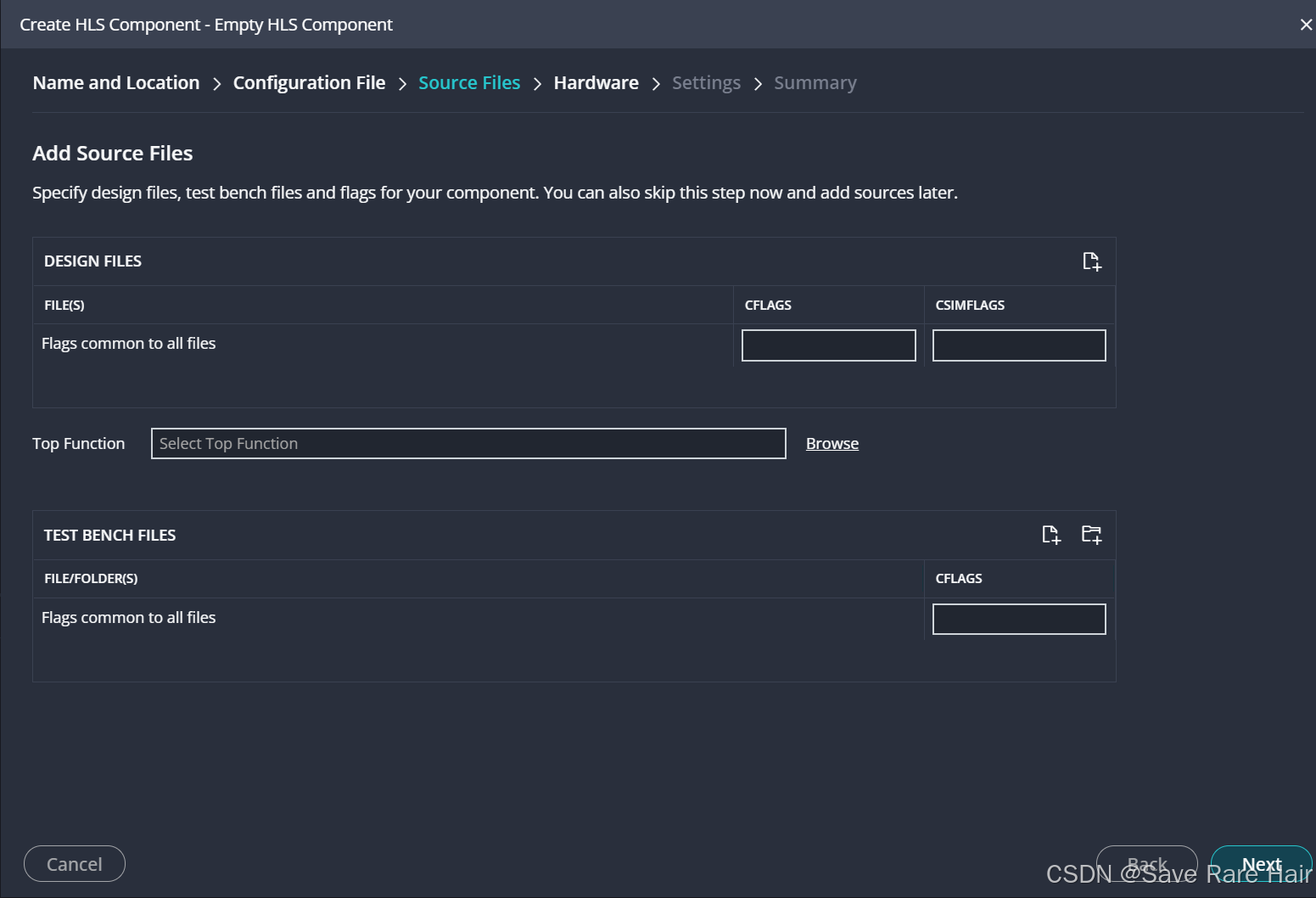

这里就先不导入源文件,待会儿自己写。

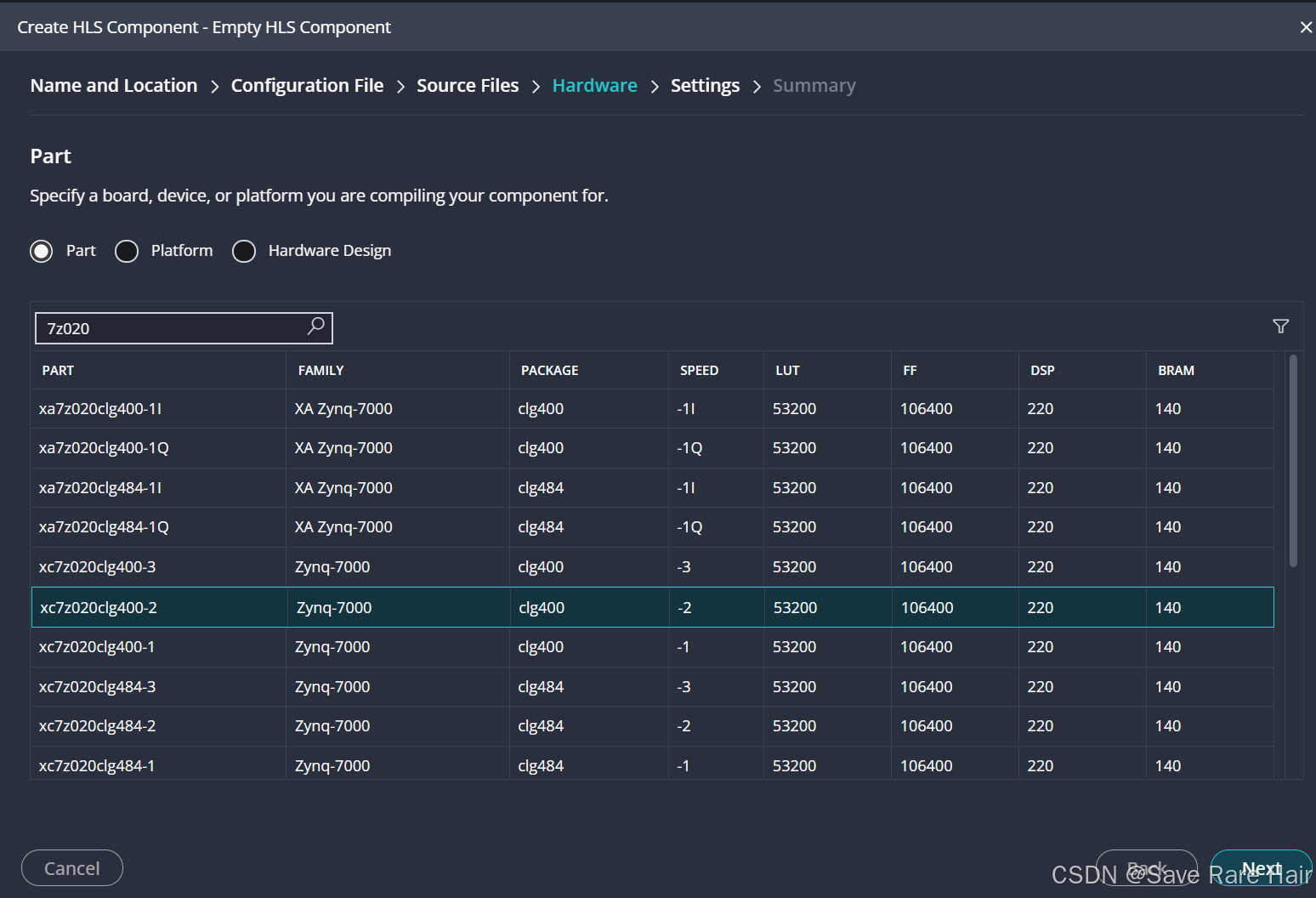

选择自己板子对应的器件型号。

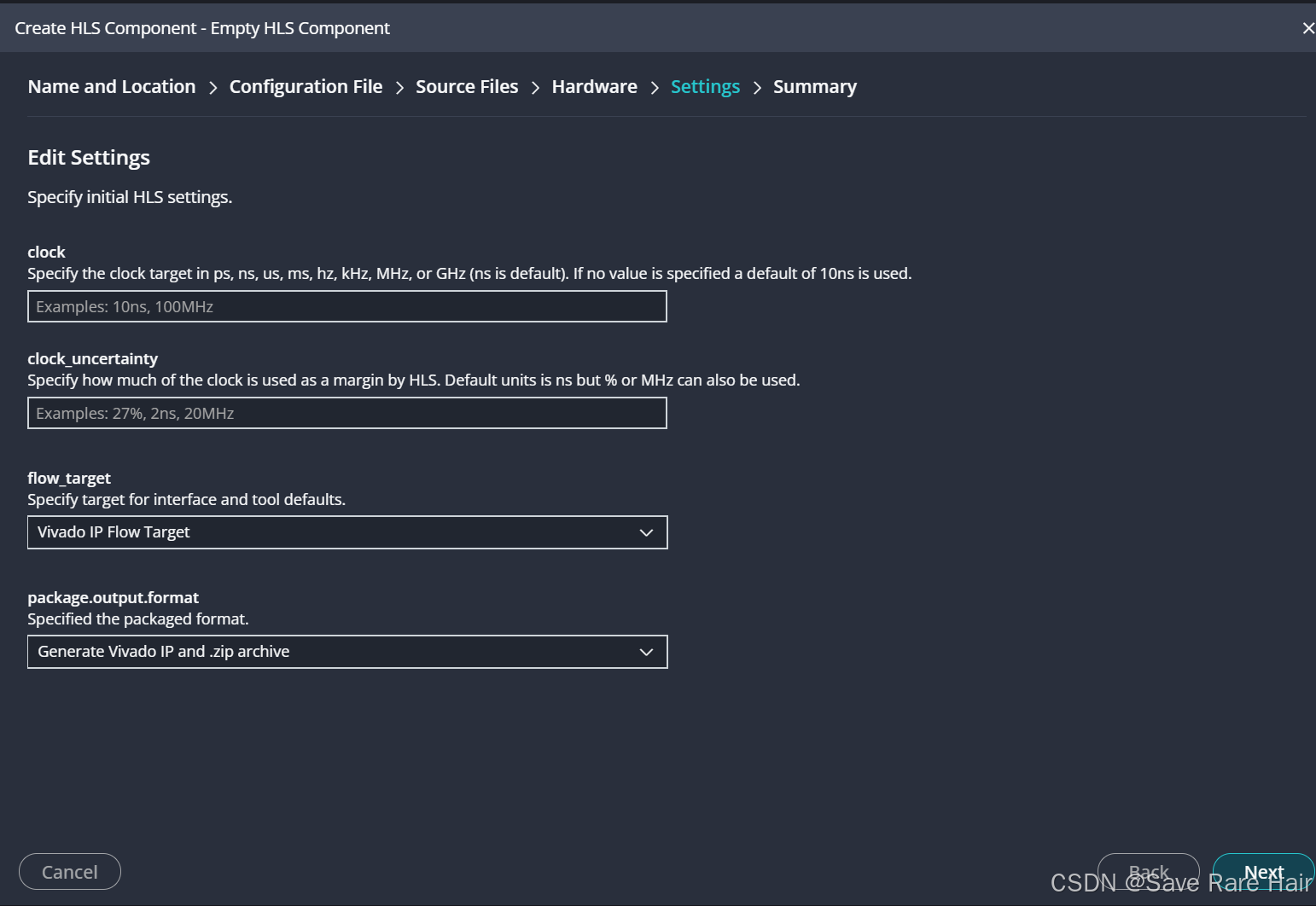

这里可以保持默认(7000系列的板子PL频率应该是50MHz和27%)。

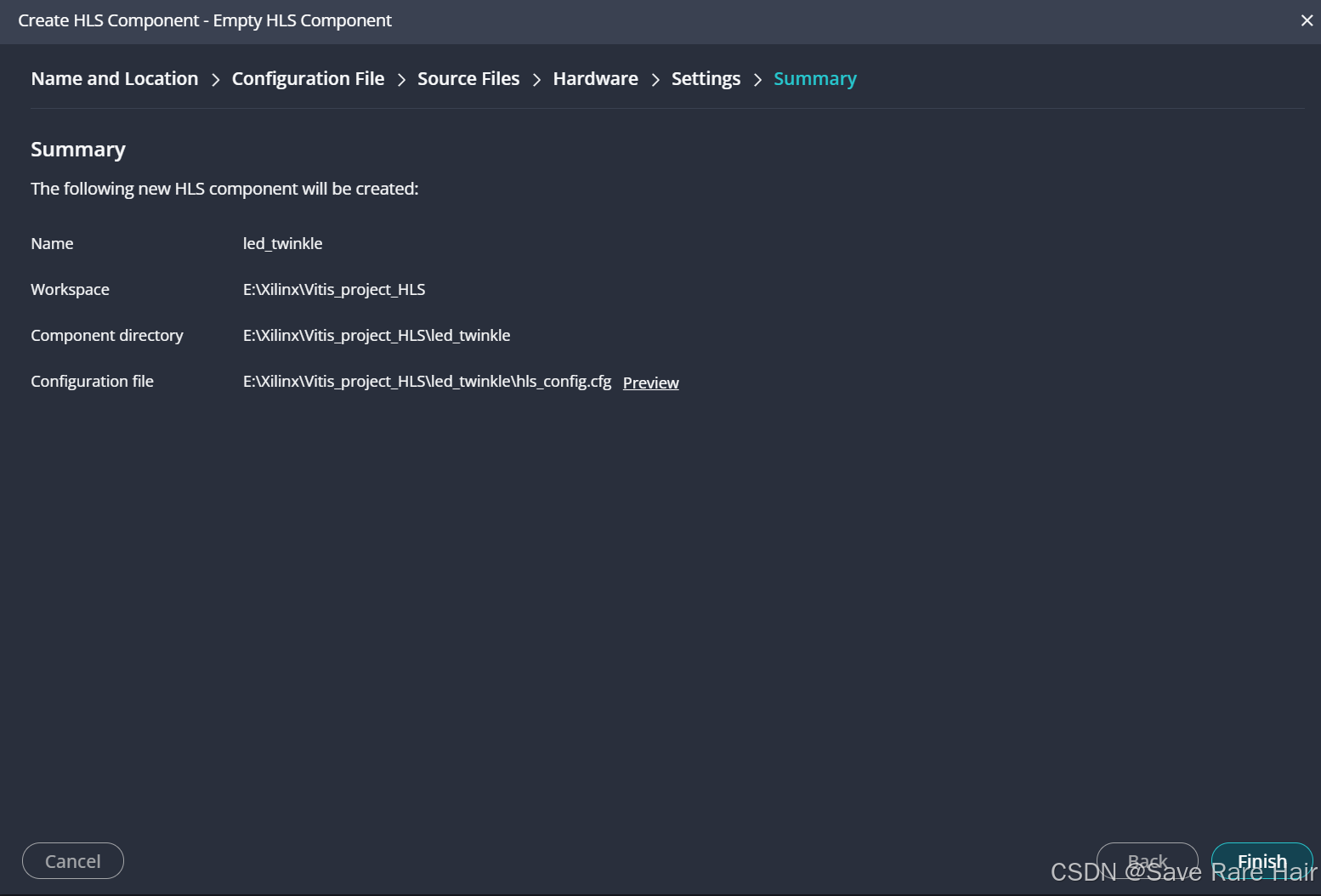

最后总结页面,点击finish。

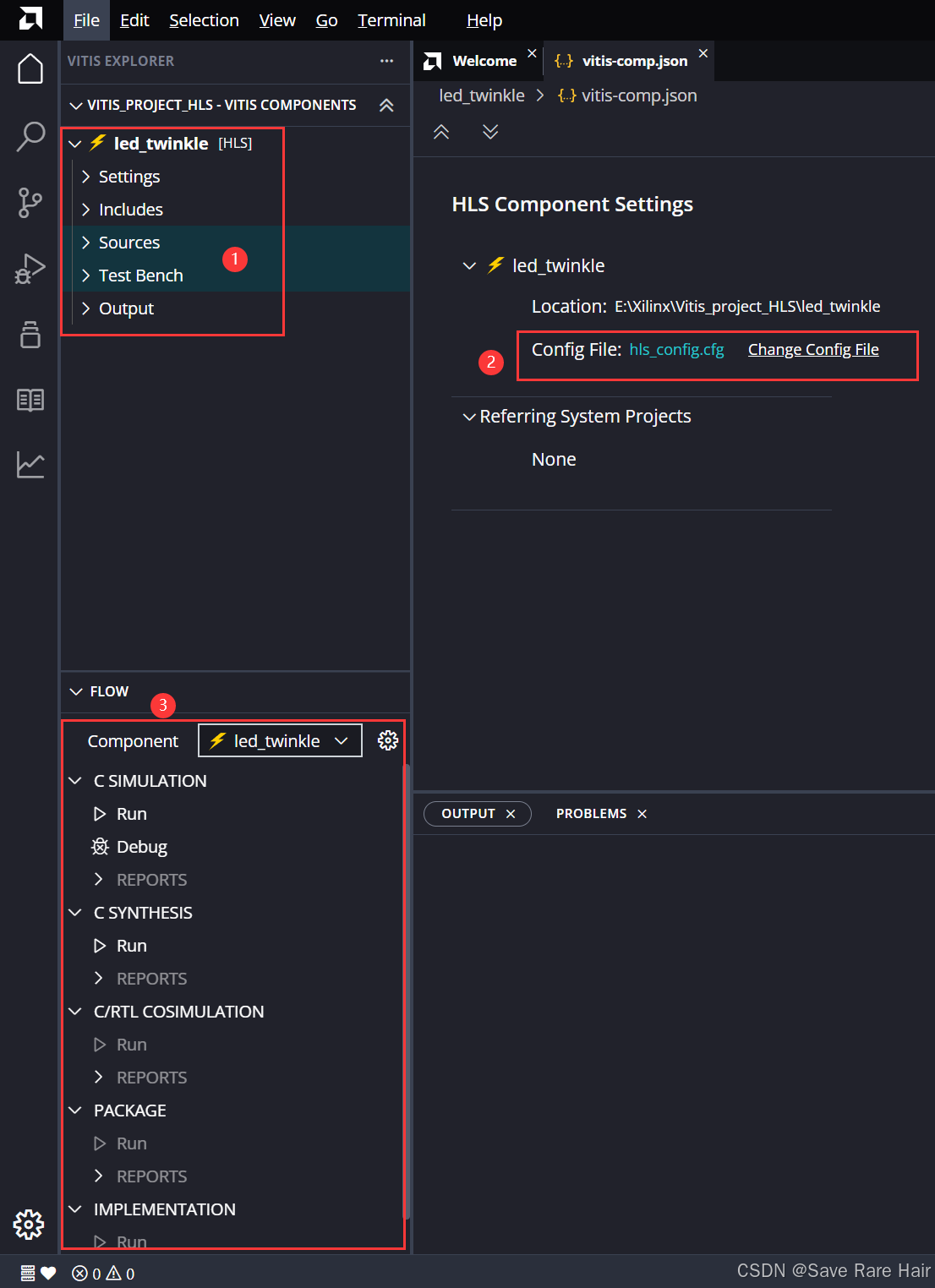

至此,工程创建完毕,工作区界面如下:

①工程文件目录

②可以在这里修改设置

③最后要进行的编译步骤

编写代码

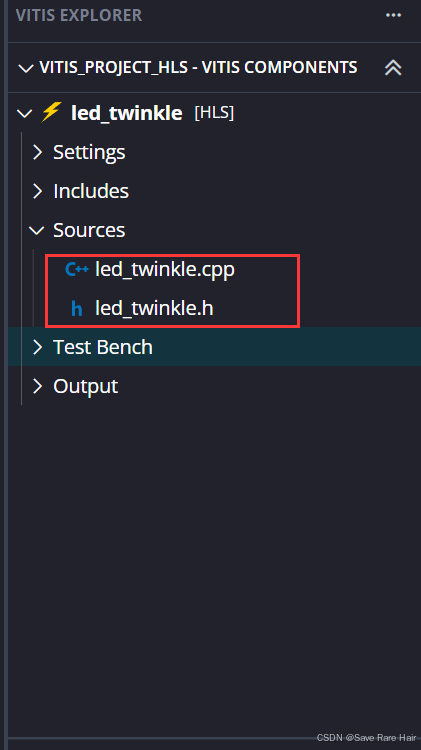

添加源文件

首先添加两个源文件:led_twinkle的.c和.h文件。

下面附上这两个文件的代码:

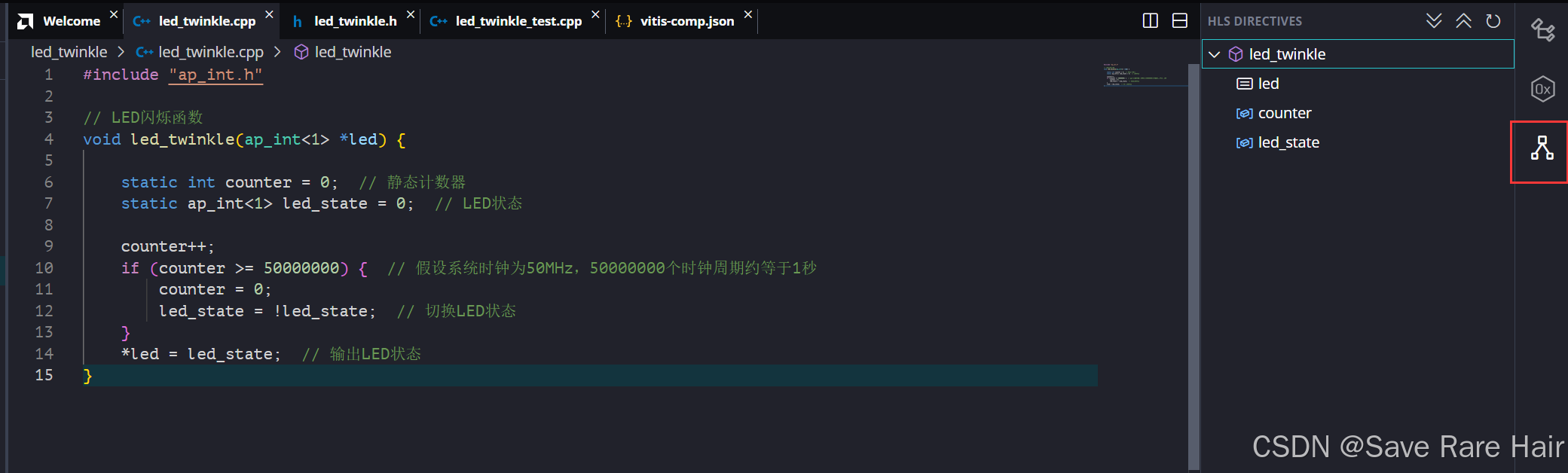

led_twinkle.cpp

#include "ap_int.h"

// LED闪烁函数

void led_twinkle(ap_int<1> *led) {

static int counter = 0; // 静态计数器

static ap_int<1> led_state = 0; // LED状态

counter++;

if (counter >= 50000000) { // 假设系统时钟为50MHz,50000000个时钟周期约等于1秒

counter = 0;

led_state = !led_state; // 切换LED状态

}

*led = led_state; // 输出LED状态

}

led_twinkle.h

#include <ap_int.h>

void led_twinkle(ap_int<1> *led);

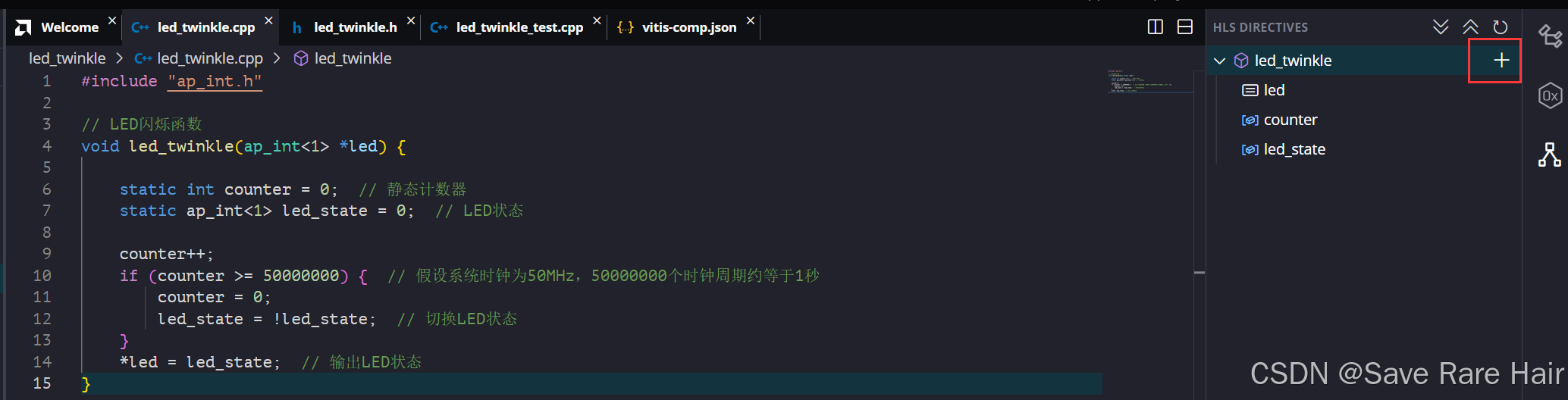

点击到led_twinkle.cpp文件里,在右边点开HLS DIRECTIVES按钮。

指令优化:在Vitis HLS中,优化代码性能通常涉及使用特定的指令(pragma)来指导编译器如何综合代码,以提高硬件效率和性能。

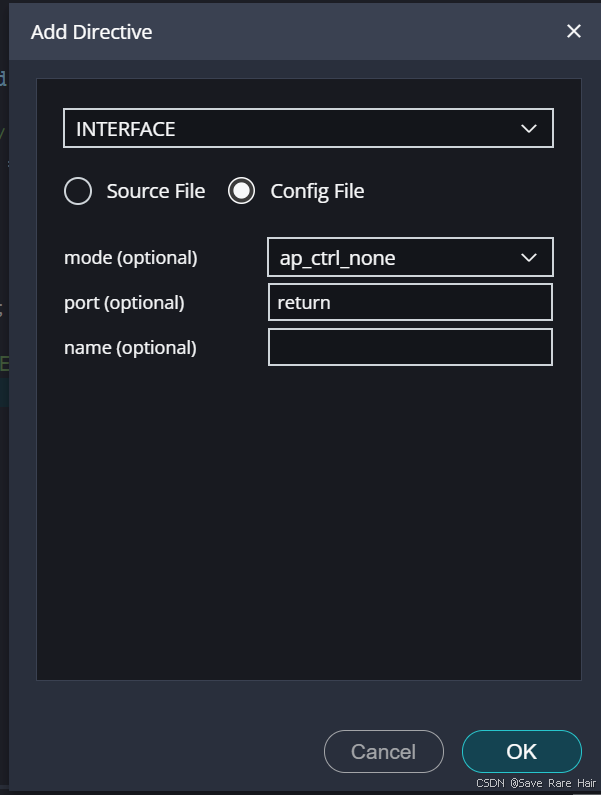

选中led_twinkle,点击右边的加号。

按照下图配置。

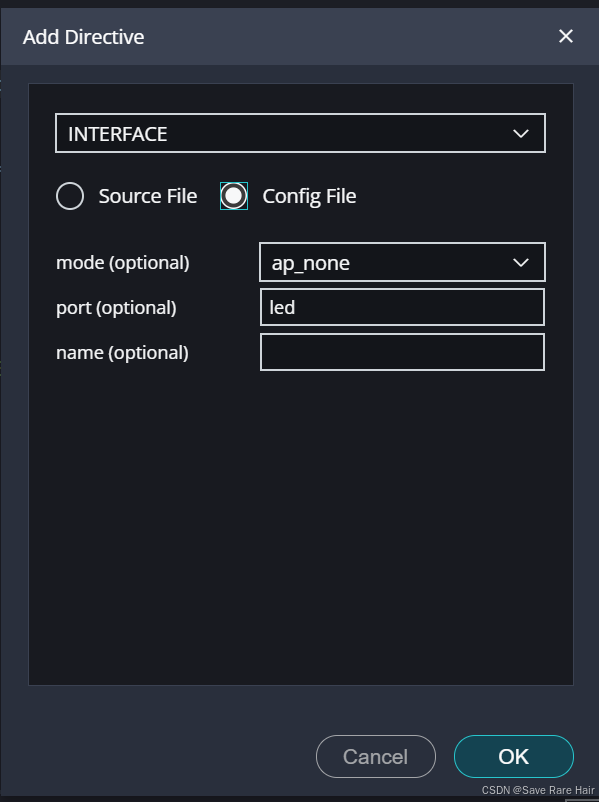

再选中led,点击右边加号。

在弹出来的界面中,按照下图配置。

添加测试文件

在Test Bench中添加一个新测试文件。源码如下:

#include "led_twinkle.h"

ap_int<1> led_1;

int main(){

led_twinkle(&led_1);

printf("Run successfully!");

return 0;

}

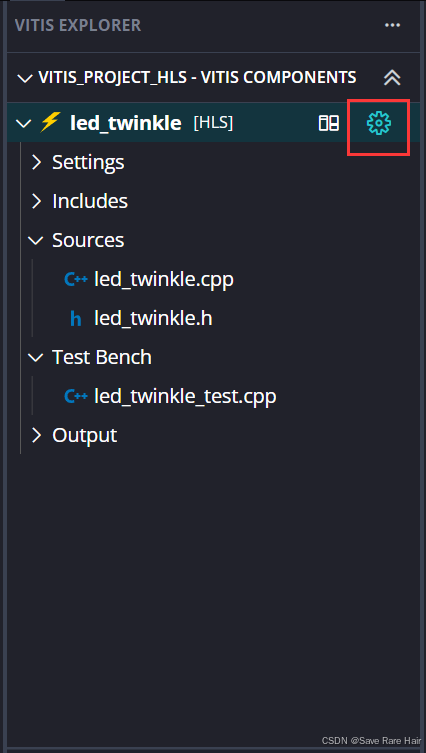

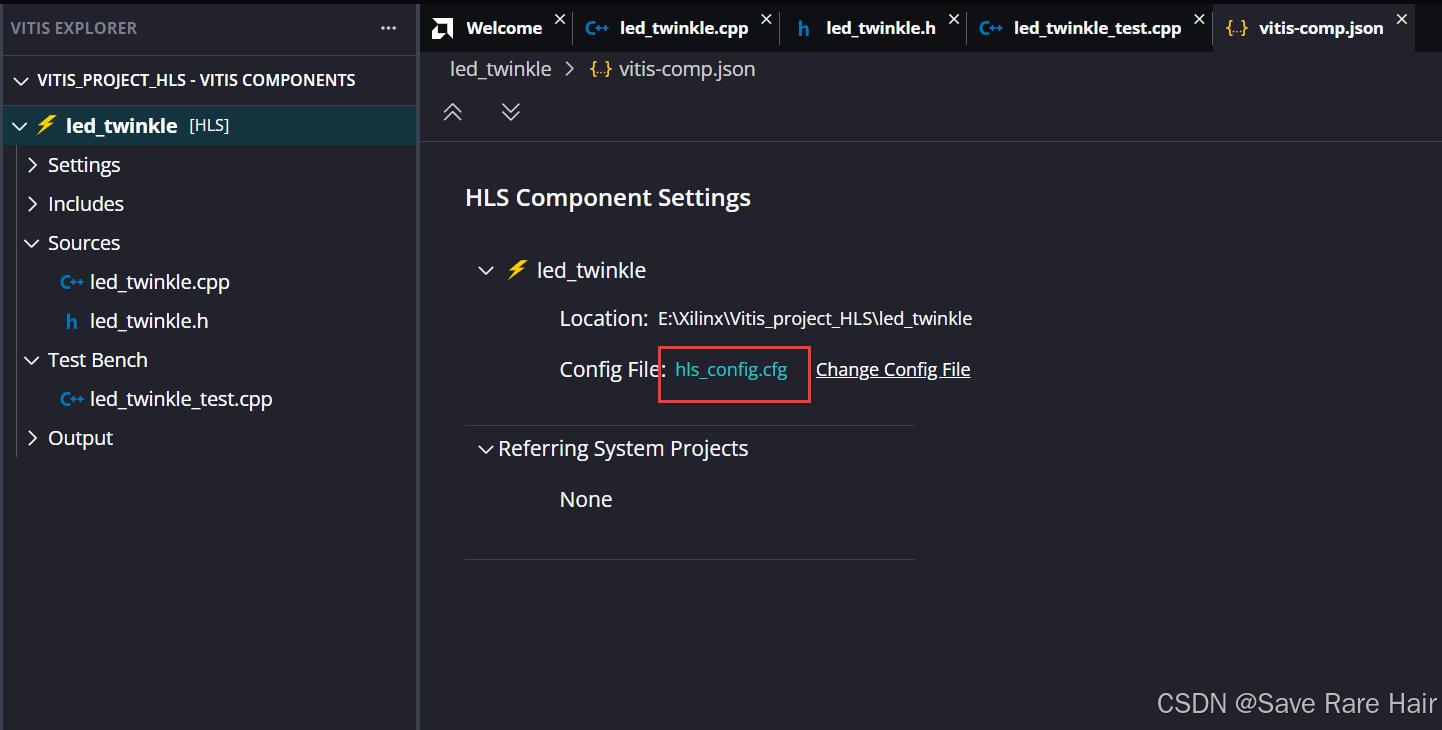

将所有文件保存,点击工程目录的设置按钮。

这里就是前面提到的可修改配置文件。

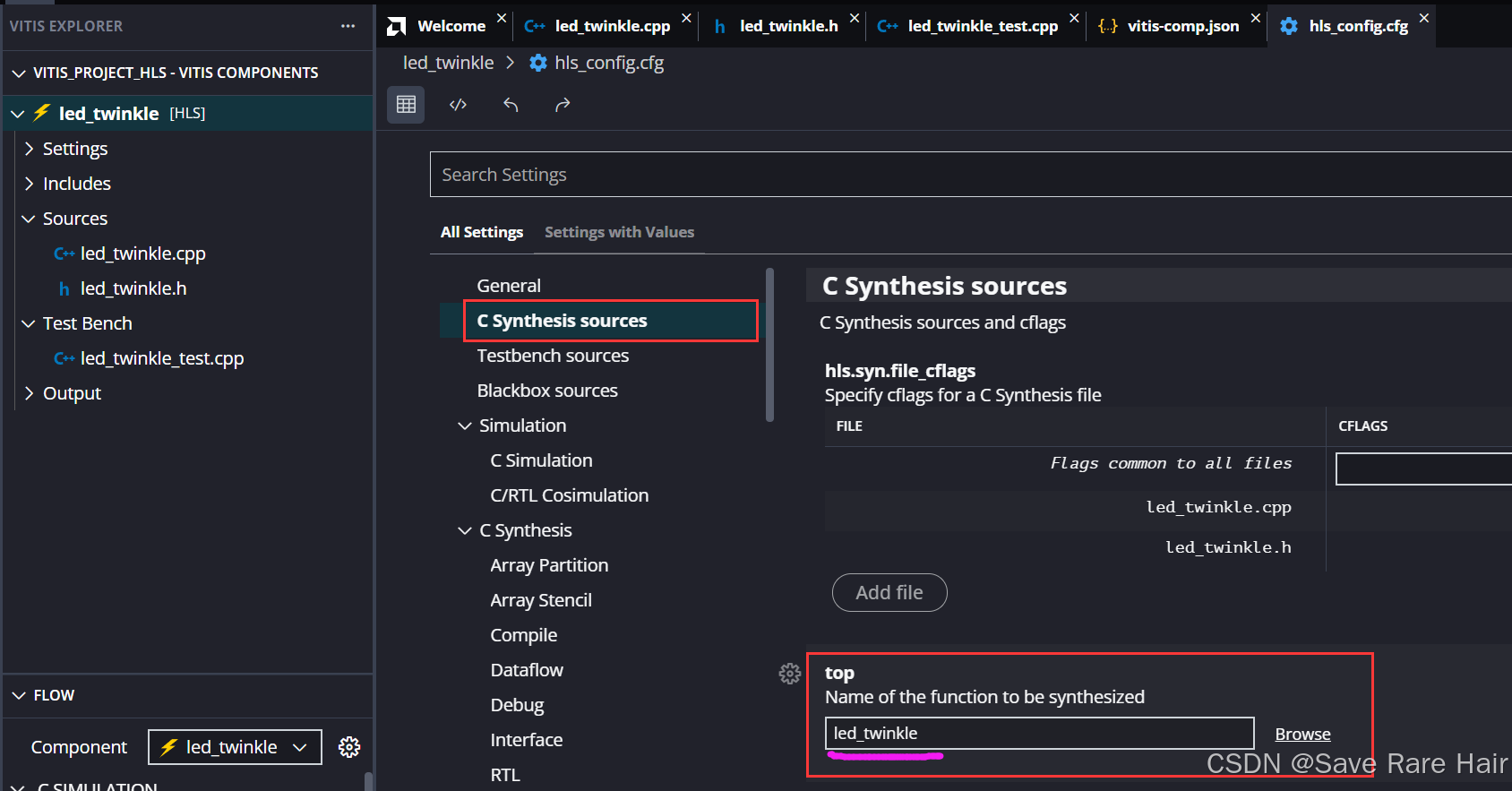

然后选中C Synthesis source,找到top一栏,把led_twinkle.cpp中的主函数名称复制到这里来,即led_twinkle。

这个是顶层模块,可以点击browse选择函数,或者直接输入,这里的主函数文件名字必须与文件内的函数名字一模一样。

至此,所有文件配置完成。

验证测试

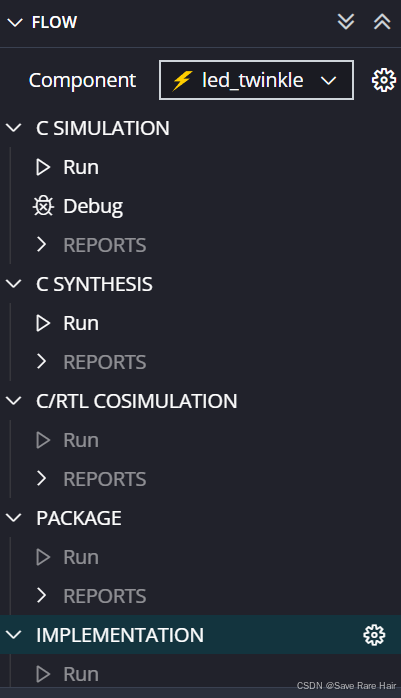

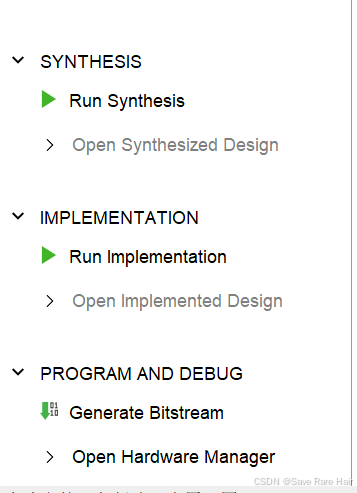

接下来进行测试,依次点击下面五个Run,所有验证通过,则会生成IP核。

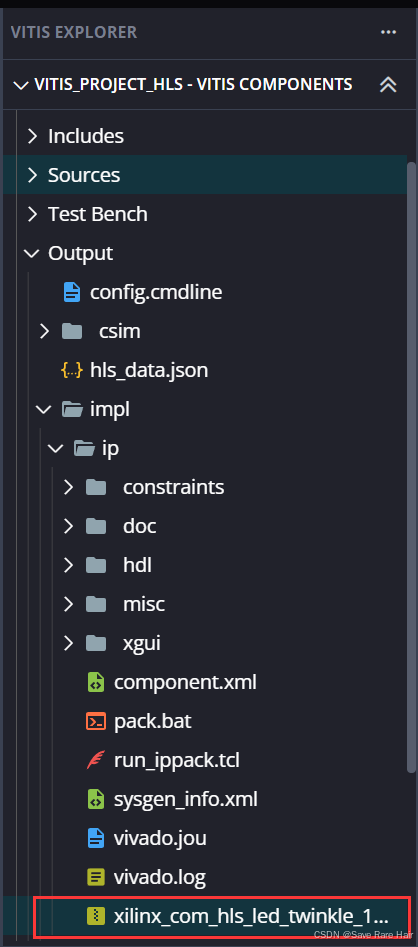

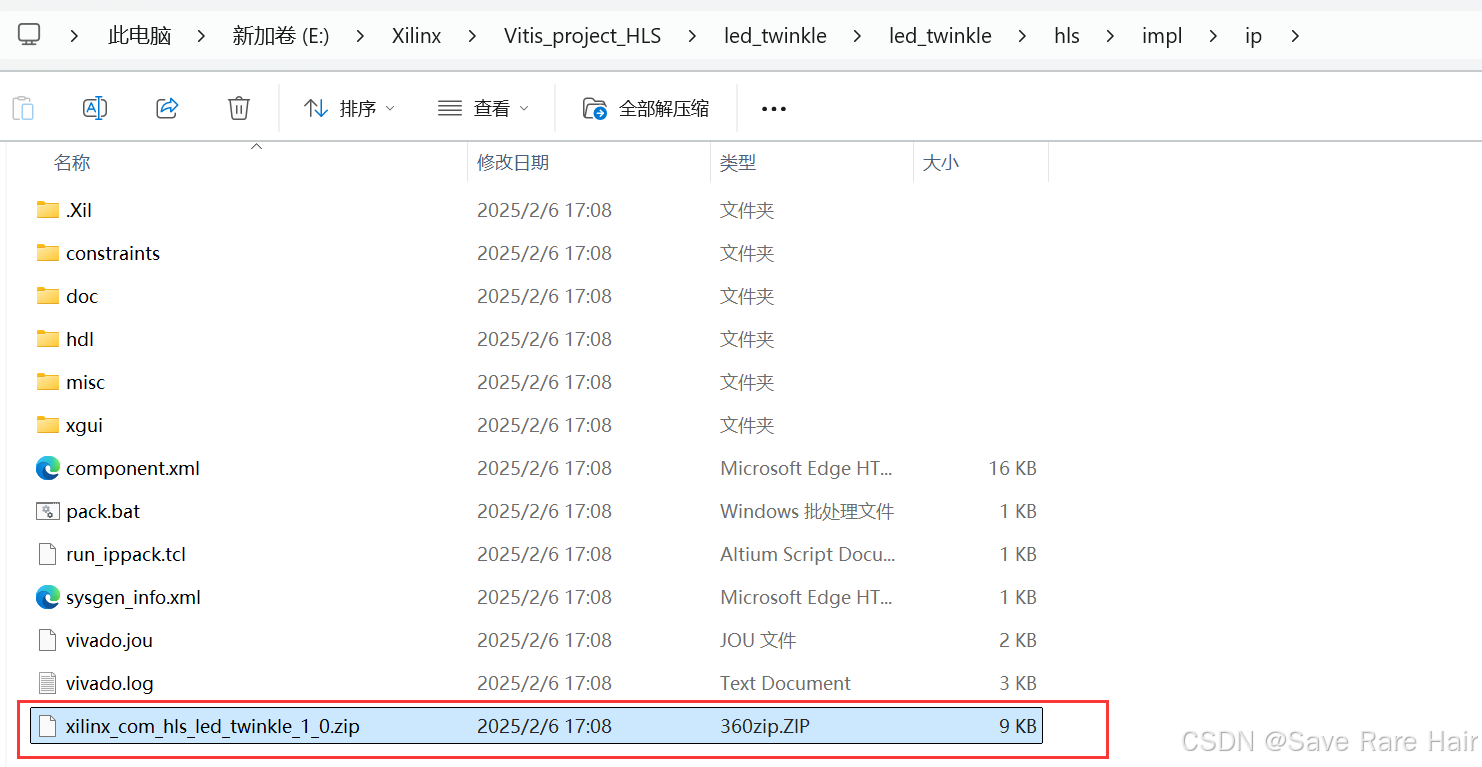

跑完5个Run都通过后,最后结果如图所示,这时候工程文件目录里会生成一个压缩包,这就是一个IP核。

也可以在工程的电脑文件夹目录里找到这个压缩包,记住这个路径,后面在Vivado中添加IP核时会用。

至此,Vitis HLS生成IP核就完成了。

————————————————这是一条分割线————————————————

接下来演示将上面生成的IP核添加到Vivado中进行下一步开发的设计。

Vivado验证IP核

创建工程

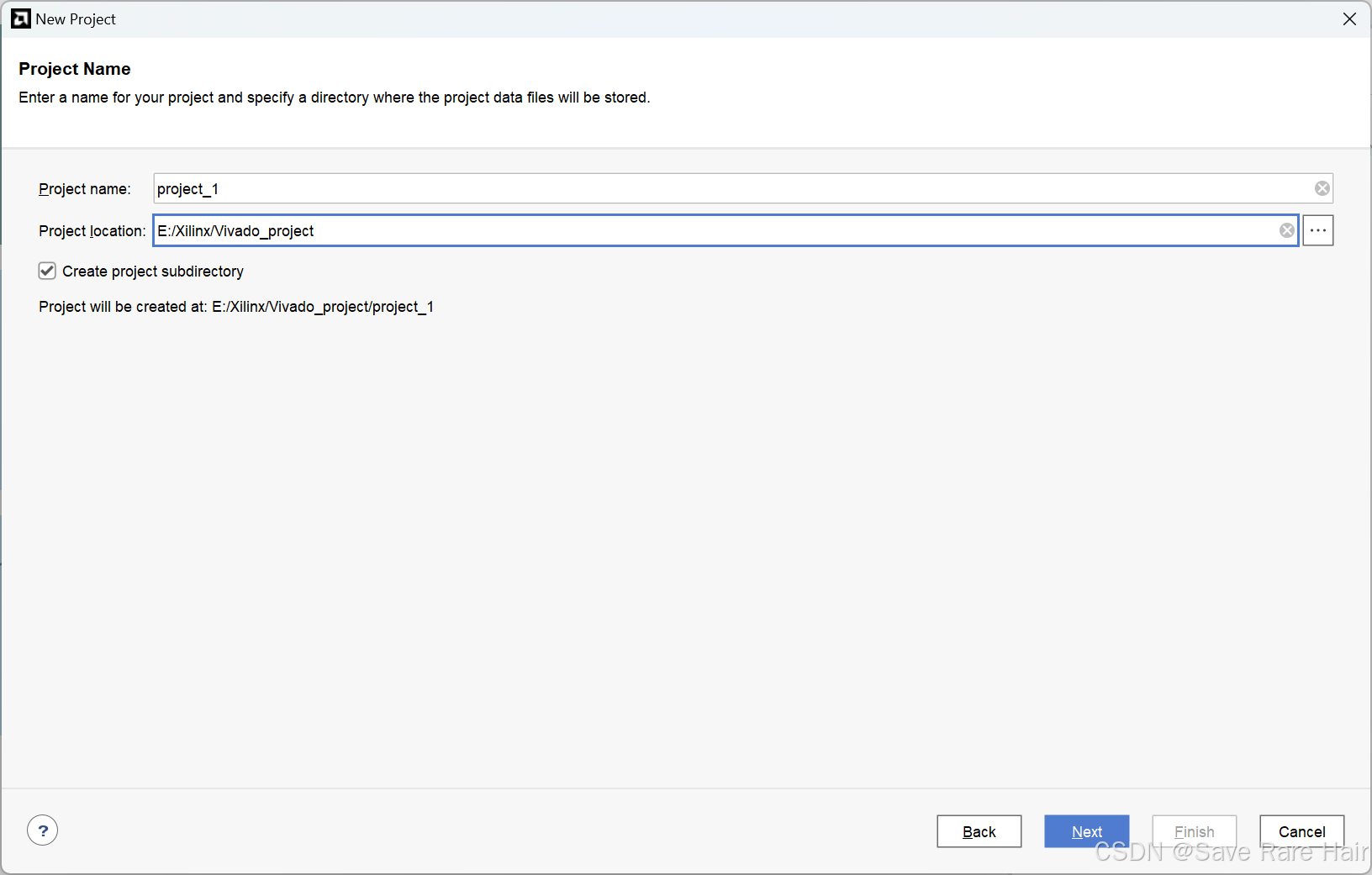

在Vivado中create project,修改工程名和工程目录。

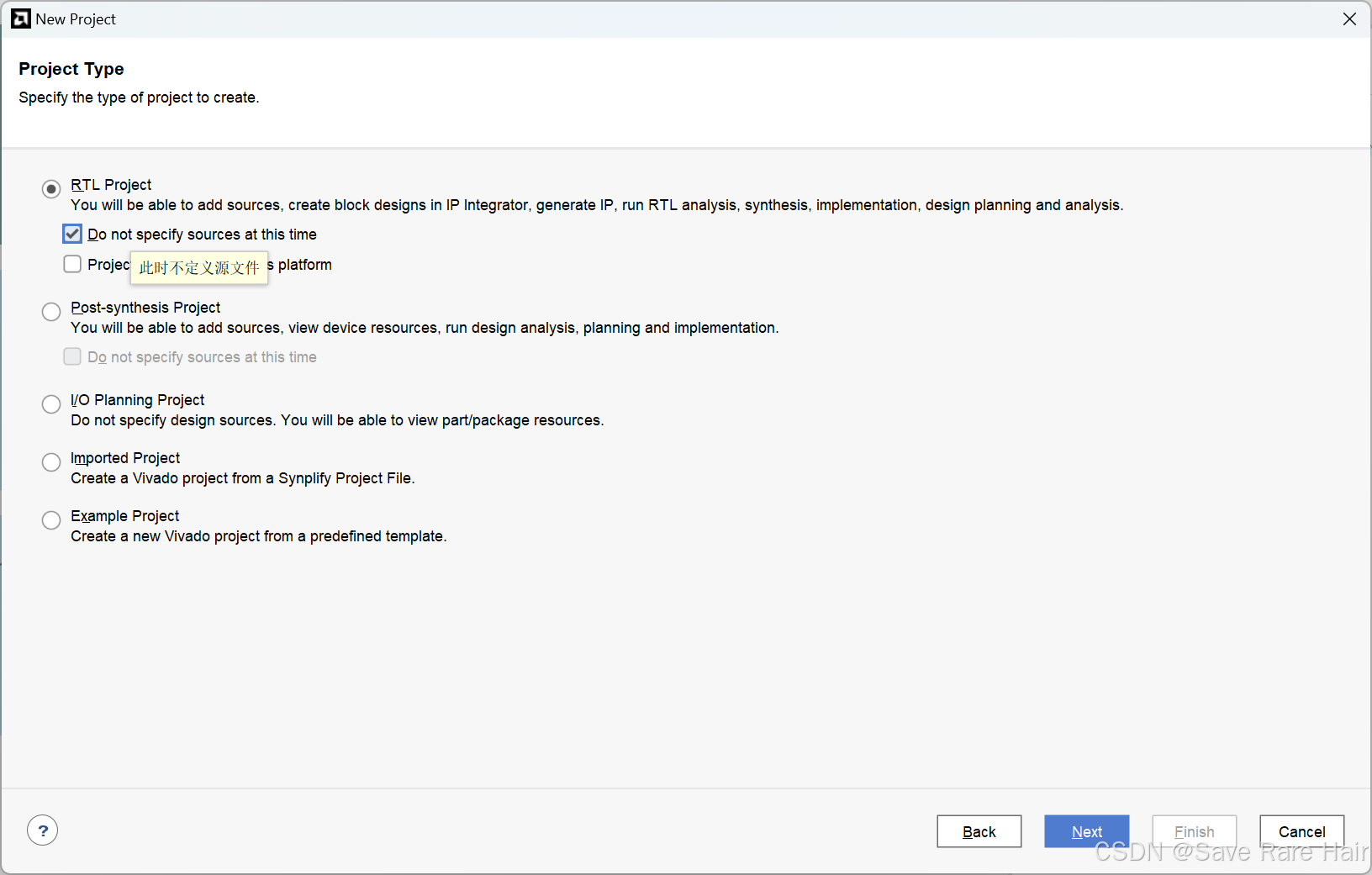

可以先选择不定义源文件,后面会使用IP核自动生成RTL代码。

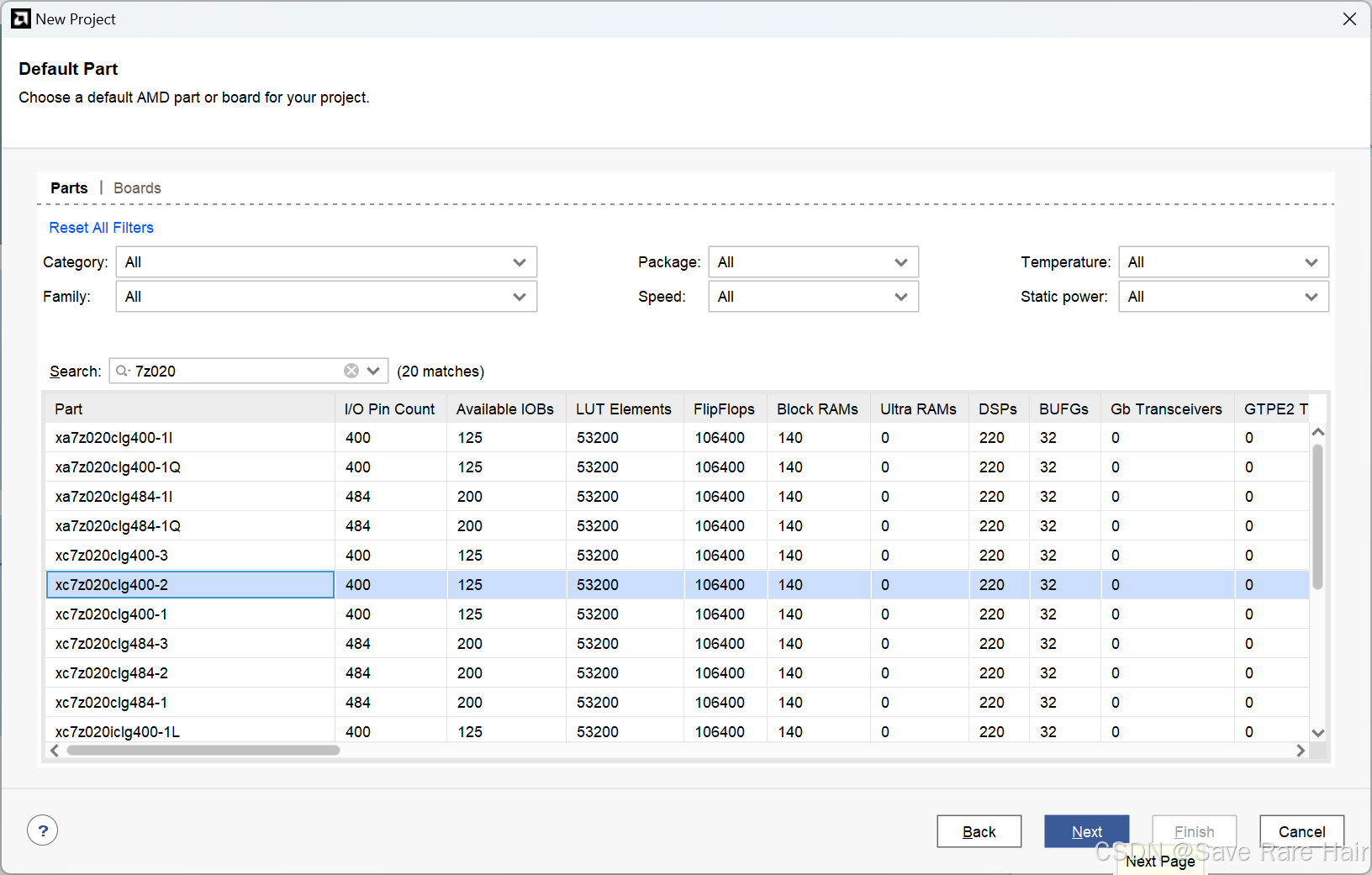

选择开发板型号后next,最后finish工程创建。

导入IP核

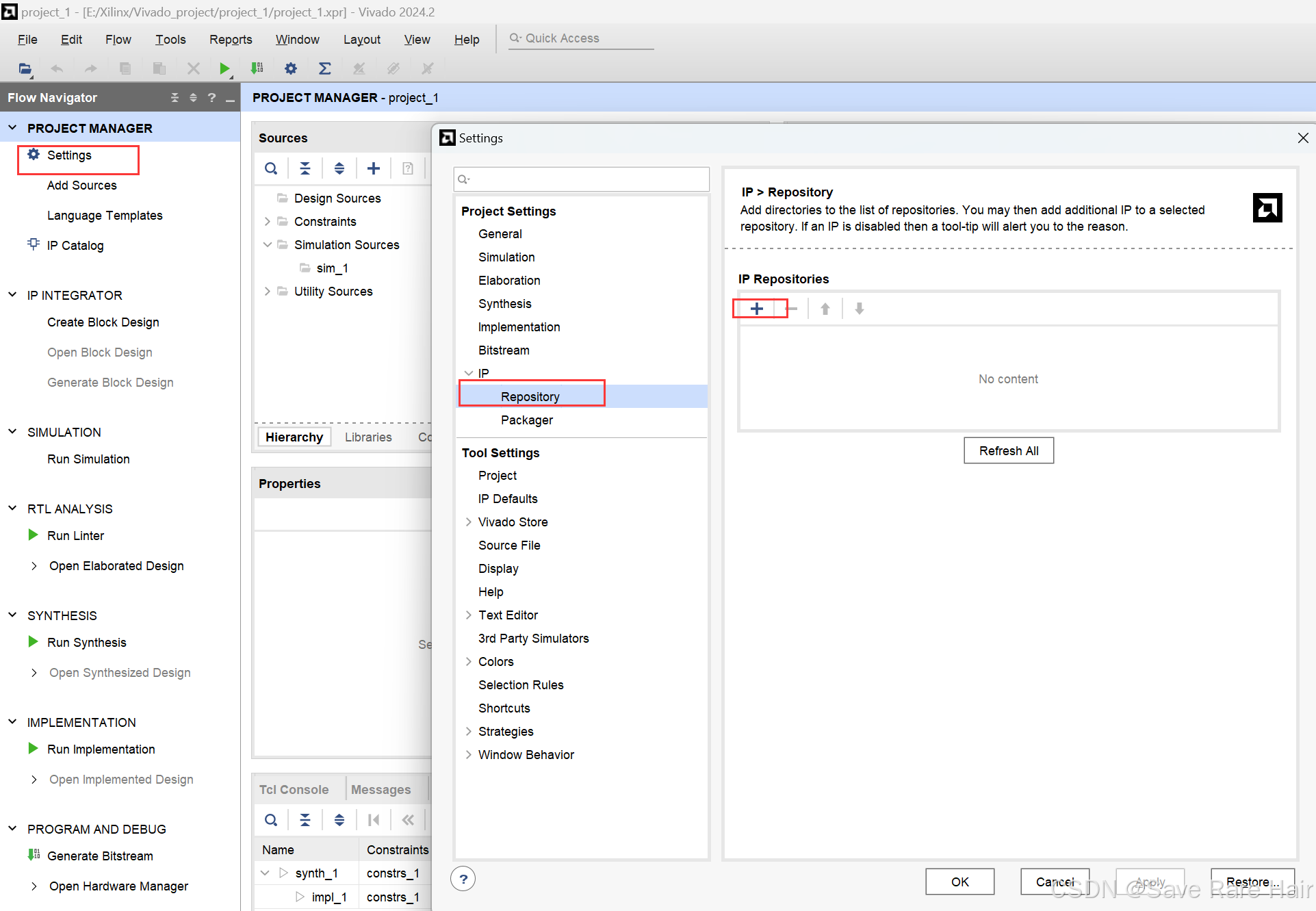

选择setting,按下图添加IP核。

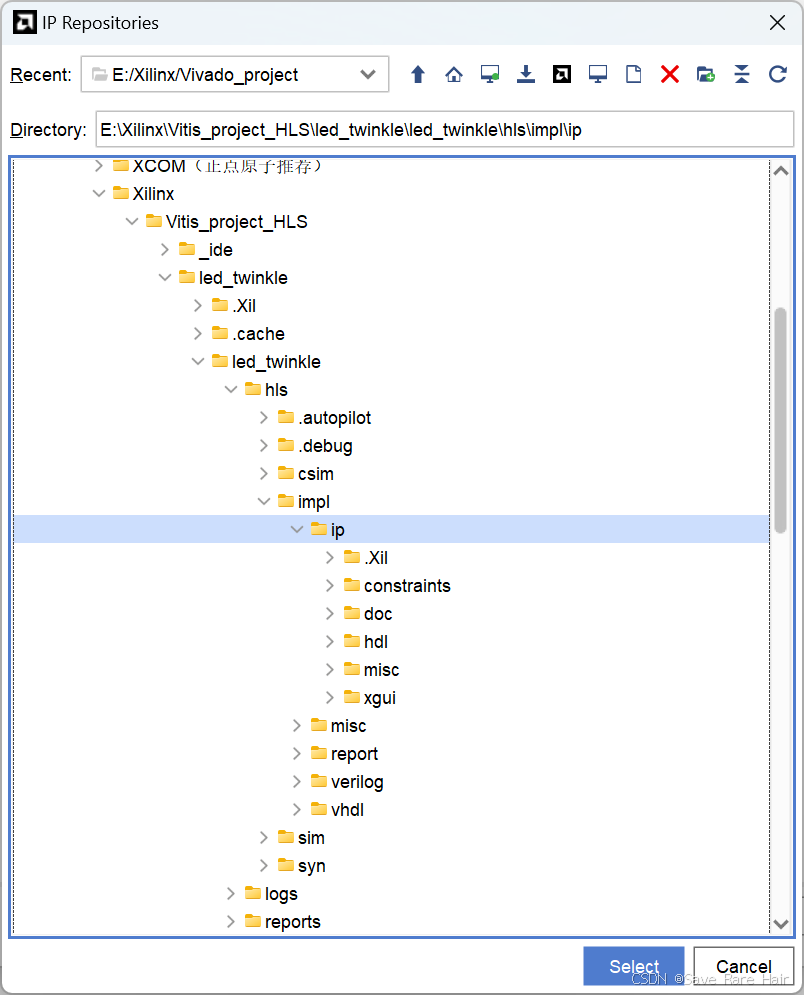

点击加号,找到上文生成的IP核所在目录,选中到ip那一级目录即可。

IP核验证

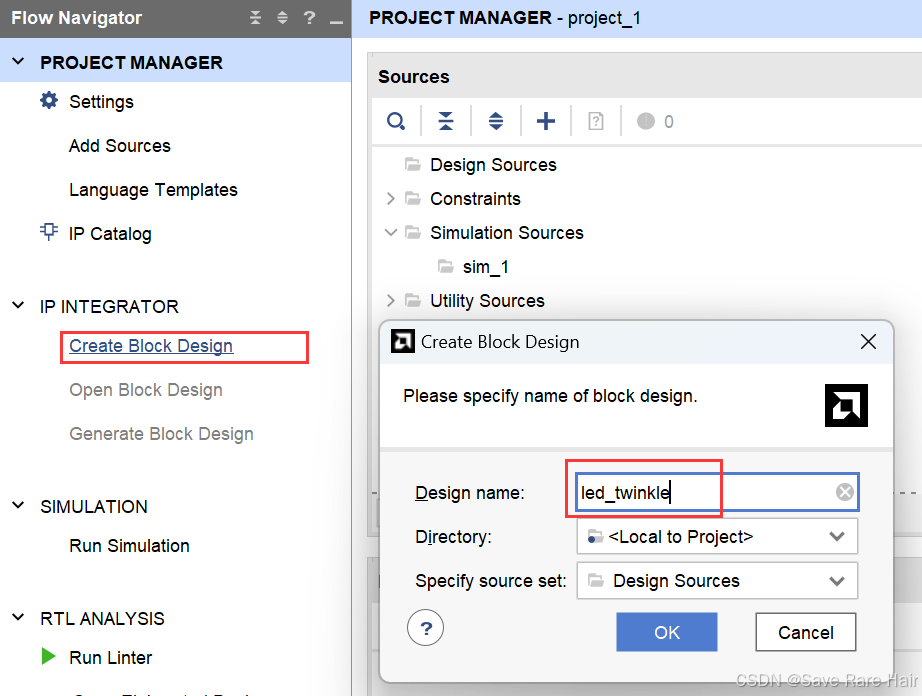

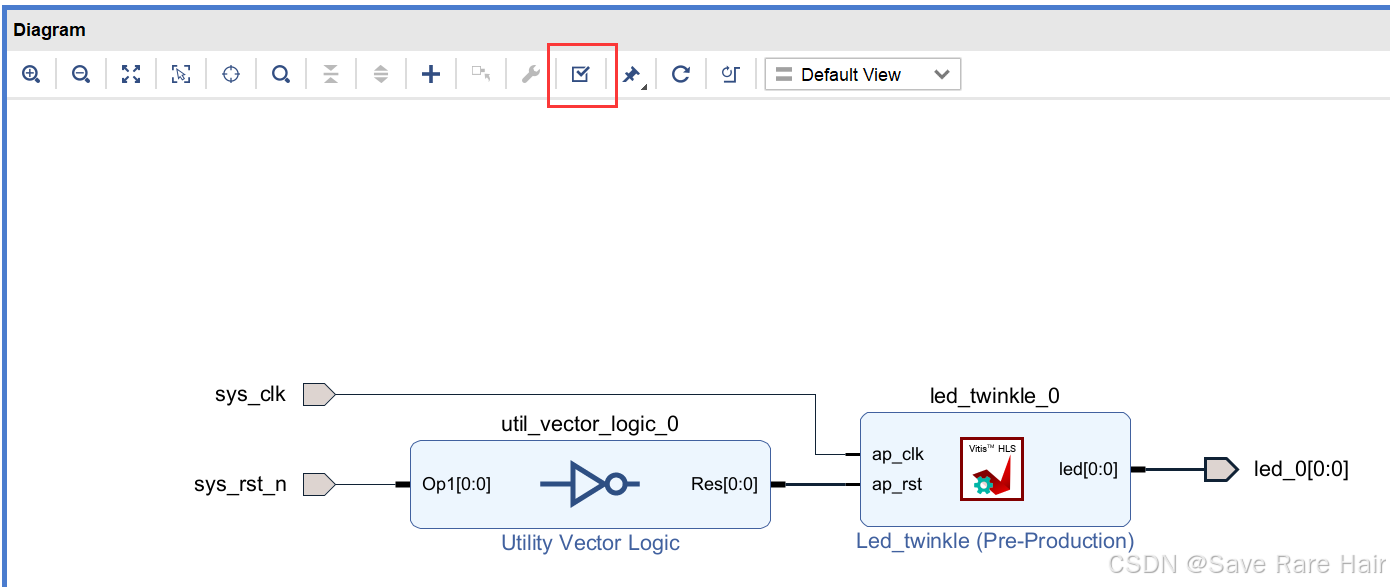

点击Create Block Design,修改文件名。

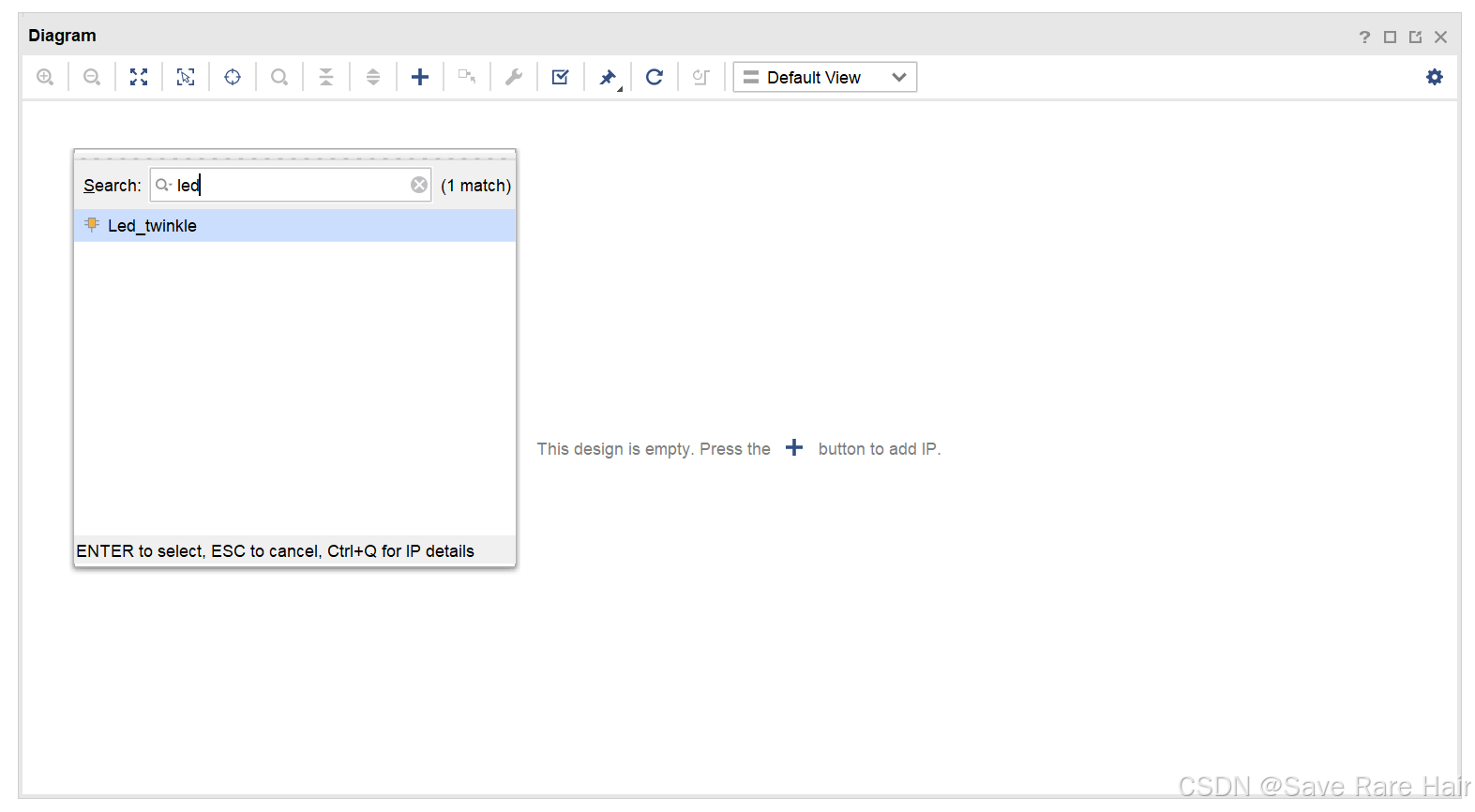

在新画布上添加上面生成的IP核,直接搜即可。

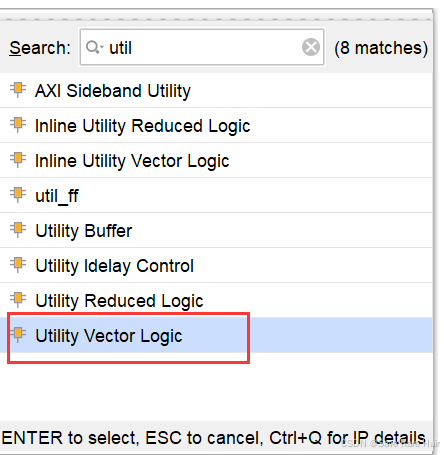

再添加一个门IP核,点击加号直接搜util。

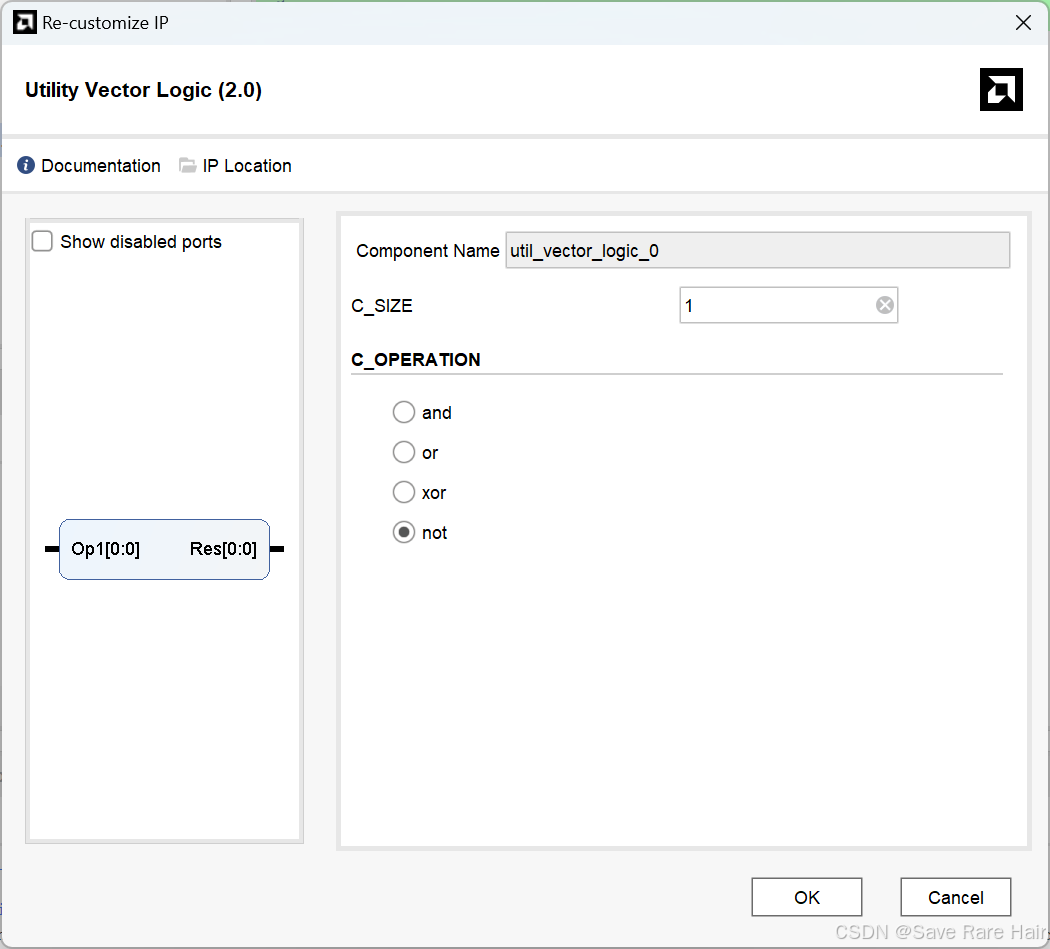

对这个IP进行配置,改成非门,位宽设置为1位。

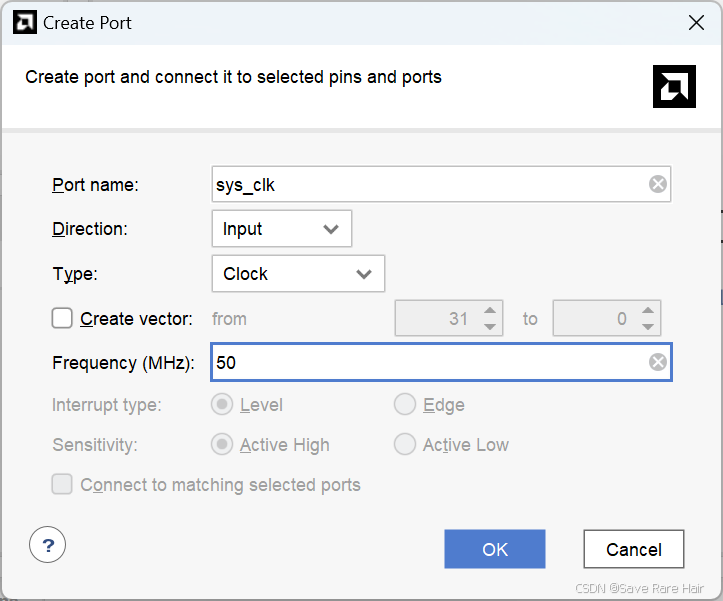

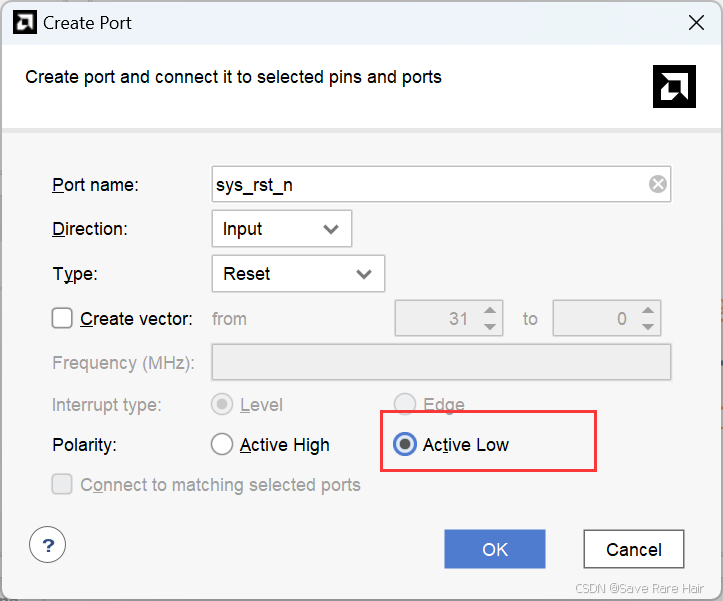

画布空白处右键,选择Create Port,添加时钟和复位端口。

右键led[0:0],选择Make External,添加一个输出端口。最后将几个器件连接起来,如下图。点击验证,检验是否有错误,提示successful即可进行下一步。

综合

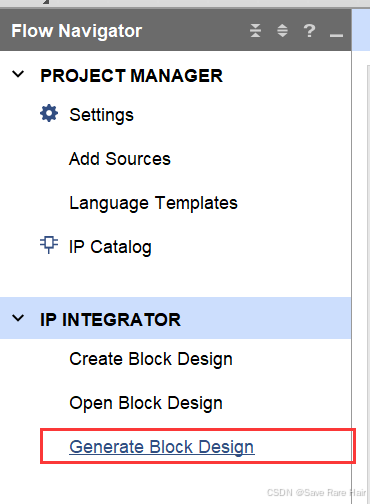

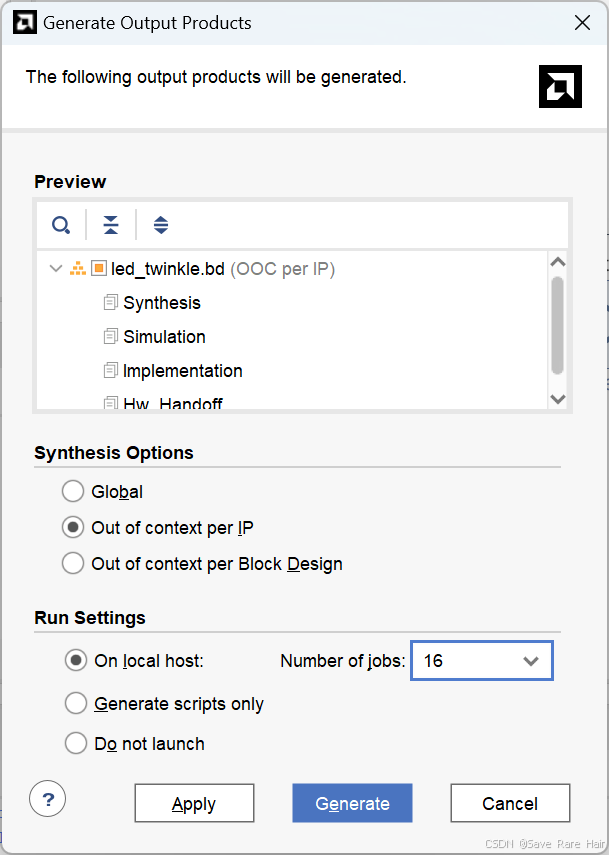

点击Generate Block Design

按照下图配置,Number of jobs是电脑的核数,选择的数越大应该会越快。

Out of Context per IP(OOC)允许为每个IP核单独生成综合结果(如DCP文件),而不是在每次综合时重新处理整个工程,在IP核未改变的情况下,Vivado不会重新综合这些IP核,从而显著减少综合的运行时间。

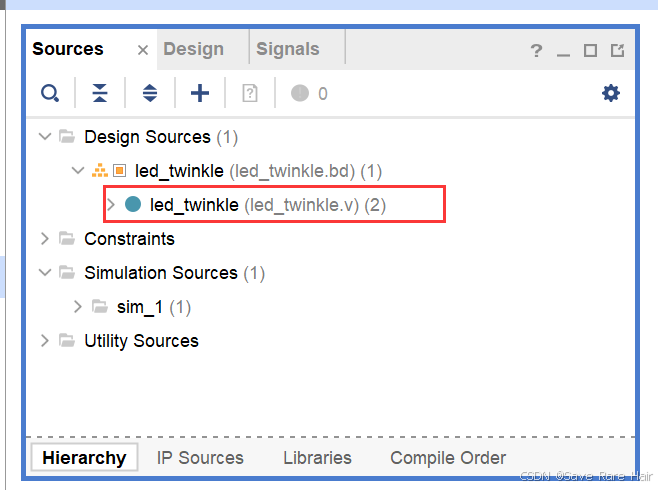

生成完后,在Sources目录里可以看到生成了源文件。不同于使用Verilog从头开始写代码,这种方法会自动生成代码。

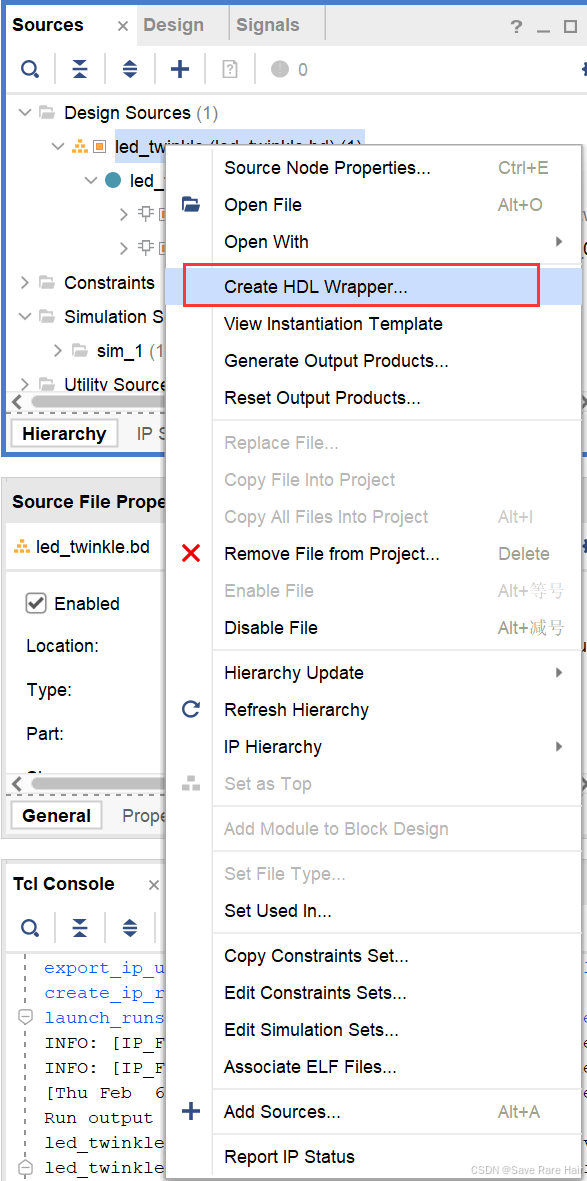

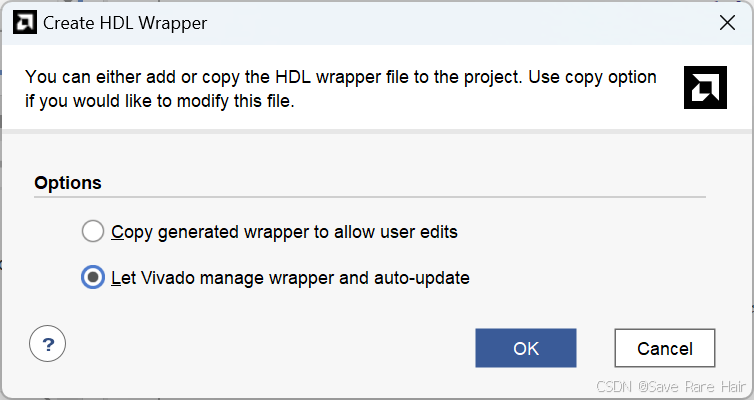

右键选择Create HDL Wrapper,下一个界面选择默认即可。

HDL Wrapper 是一个用于封装Block Design(块设计)的工具,它将Block Design转换为一个可综合的顶层HDL文件(通常是Verilog或VHDL)。这个顶层文件可以被Vivado工具读取,并用于后续的综合、实现和生成比特流文件

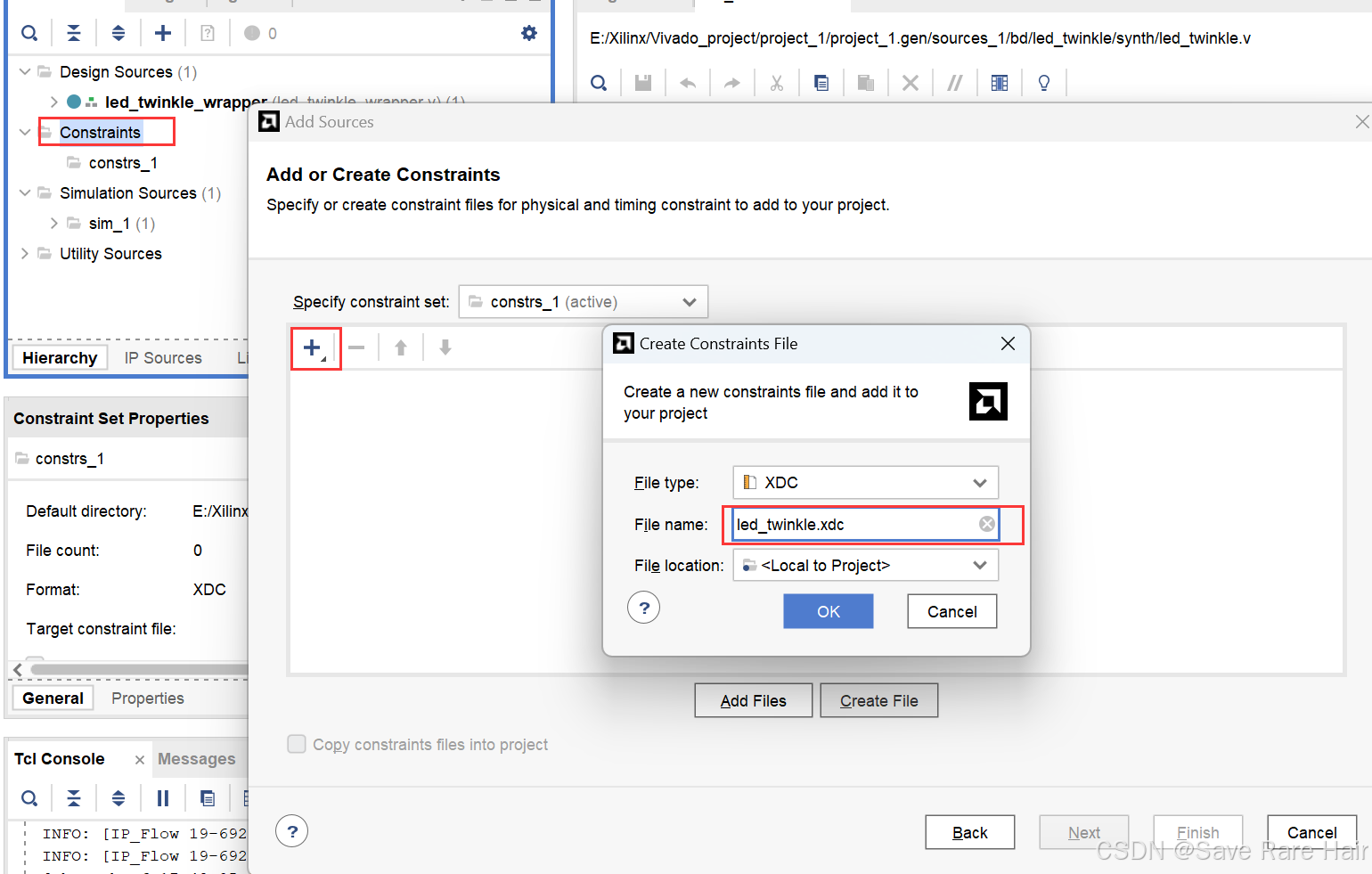

管脚约束

右键Constrains,添加一个约束文件。

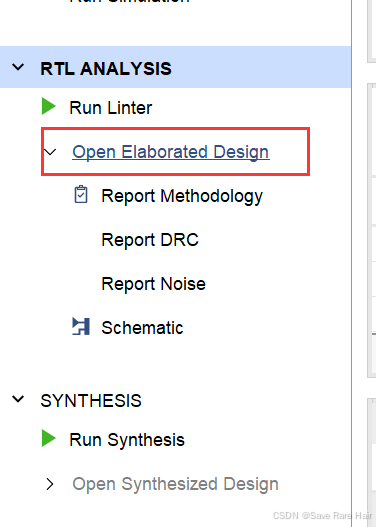

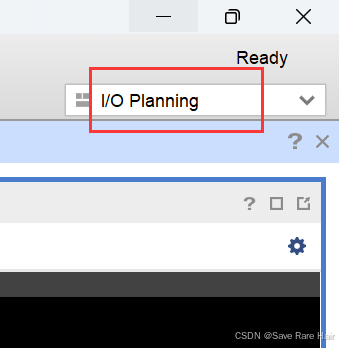

这里还有一种添加约束文件的方法,不需要自己写,只需要指定管脚,软件会自动生成。点击下图所示。

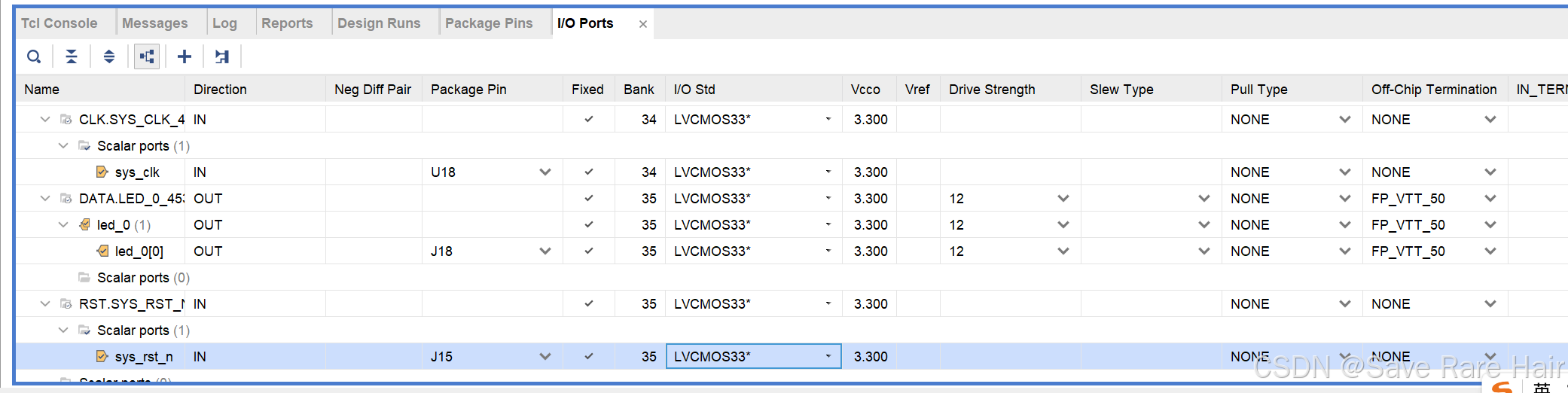

软件下方会有I/0 Ports窗口。如果没有这个窗口,就去软件右上角找到I/O Planning打开。

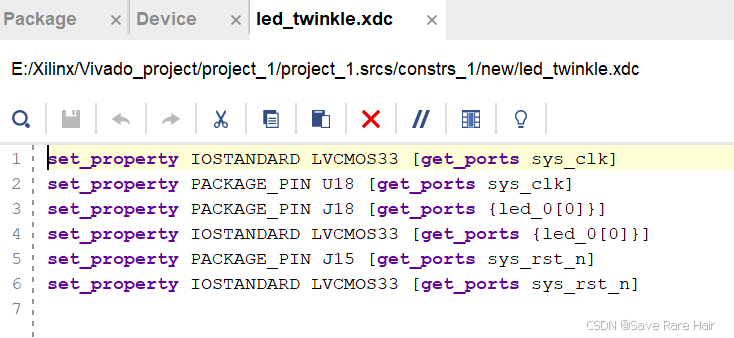

配置管脚和电平完成后如下图,Ctrl+S保存,XDC文件里会自动生成代码。

我的开发板是正点原子领航者V1,不同开发板约束管脚和电平不一样,要去查自己板子的原理图。

至此,所有配置完成,接下来进行仿真和综合。

综合和实现

依次点击综合和实现,最后生成比特流,下载到开发板验证。

最终可以看到开发板的led0闪烁。

led闪烁

此实验只是打通了从Vitis HLS到Vivado BD设计的流程,其中的实验代码以及一些配置的含义并不清楚,后续会继续学习HLS开发的内容,自己编写较为复杂的HLS代码,还要学习Vitis软件开发ZYNQ。

参考博客

Vitis HLS 构建项目并生成IP核(Vivado HLS)-菜鸡渣渣一个 https://blog.csdn.net/weixin_44115643/article/details/124216930?fromshare=blogdetail&sharetype=blogdetail&sharerId=124216930&sharerefer=PC&sharesource=qq_52033578&sharefrom=qq(想看更多?下载CSDN APP:https://www.csdn.net/apps/download/)

Vivado验证Vitis HLS生成的IP核-菜鸡渣渣一个 https://blog.csdn.net/weixin_44115643/article/details/124232562?fromshare=blogdetail&sharetype=blogdetail&sharerId=124232562&sharerefer=PC&sharesource=qq_52033578&sharefrom=qq(想看更多?下载CSDN APP:https://www.csdn.net/apps/download/)

高效的VIVADO BlockDesign设计方法:将自己设计的模块信号以总线形式聚合-FPGA从入门到跑路 https://blog.csdn.net/xxqlover/article/details/139426981?fromshare=blogdetail&sharetype=blogdetail&sharerId=139426981&sharerefer=PC&sharesource=qq_52033578&sharefrom=qq(想看更多?下载CSDN APP:https://www.csdn.net/apps/download/)

FPGA学习笔记#4 Vitis HLS 入门的第一个工程-绅士羊OuO https://blog.csdn.net/qq_38876396/article/details/143645004?fromshare=blogdetail&sharetype=blogdetail&sharerId=143645004&sharerefer=PC&sharesource=qq_52033578&sharefrom=qq(想看更多?下载CSDN APP:https://www.csdn.net/apps/download/)

2731

2731

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?