Vitis_HLS 2024使用教程

注:本教程只教学vitis HLS的高层次汇编rtl语言,而非嵌入式开发vitis

使用资料:1.xilinx ug1399文档(解释软件各种功能和使用) 运行实现 • Vitis 高层次综合用户指南 (UG1399) • 阅读器 • AMD 技术信息门户网站

- xilinx ug1400文档 “Debug”视图 • Vitis 统一软件平台文档 嵌入式软件开发 (UG1400) • 阅读器 • AMD 技术信息门户网站

- 正点原子教程,在文件夹内1号文件

安装:安装参考1399文档内安装流程,特别注意:一定要申请xilinx vitis_hls的使用License

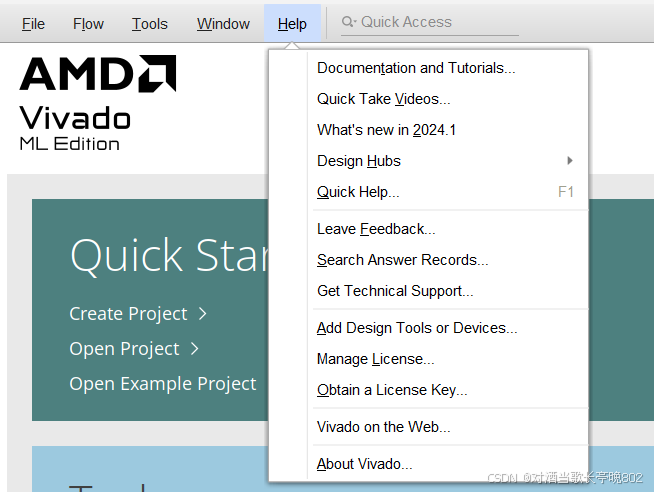

License导入教程:1.打开vivado2024

2.点击help内的manage License

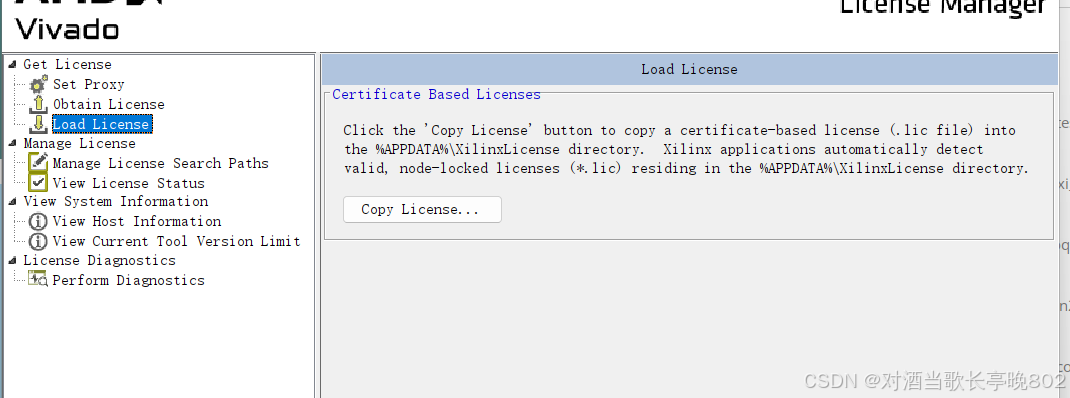

3点击 load

点击copy license 把你申请到的许可证放进去(注:此许可证只给了 vitis hls的使用权限,vivado的上网自己搜)

Vitis HLS 2024 使用教程(以xilinx实例库的向量加法器为例)

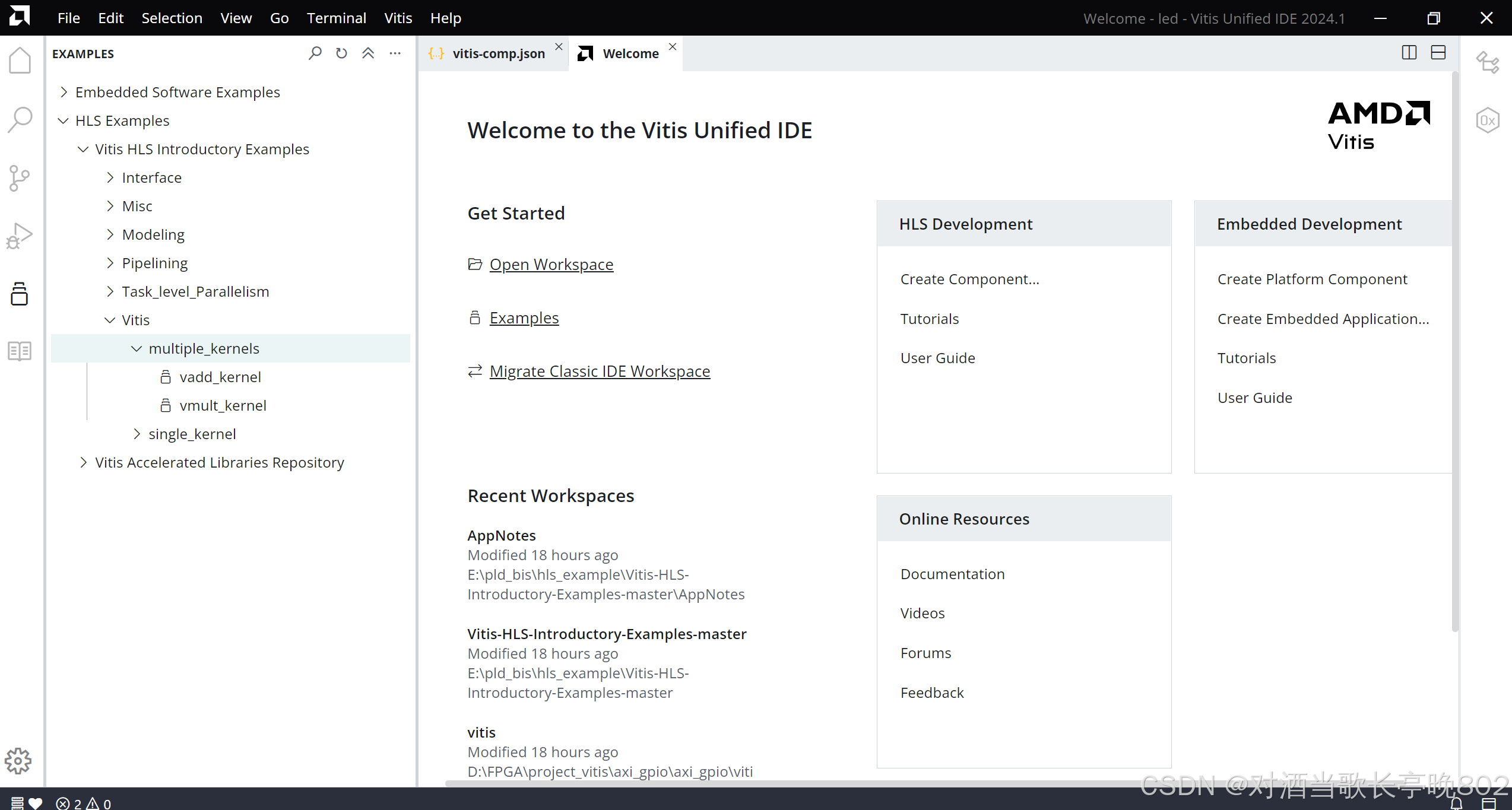

- 打开软件

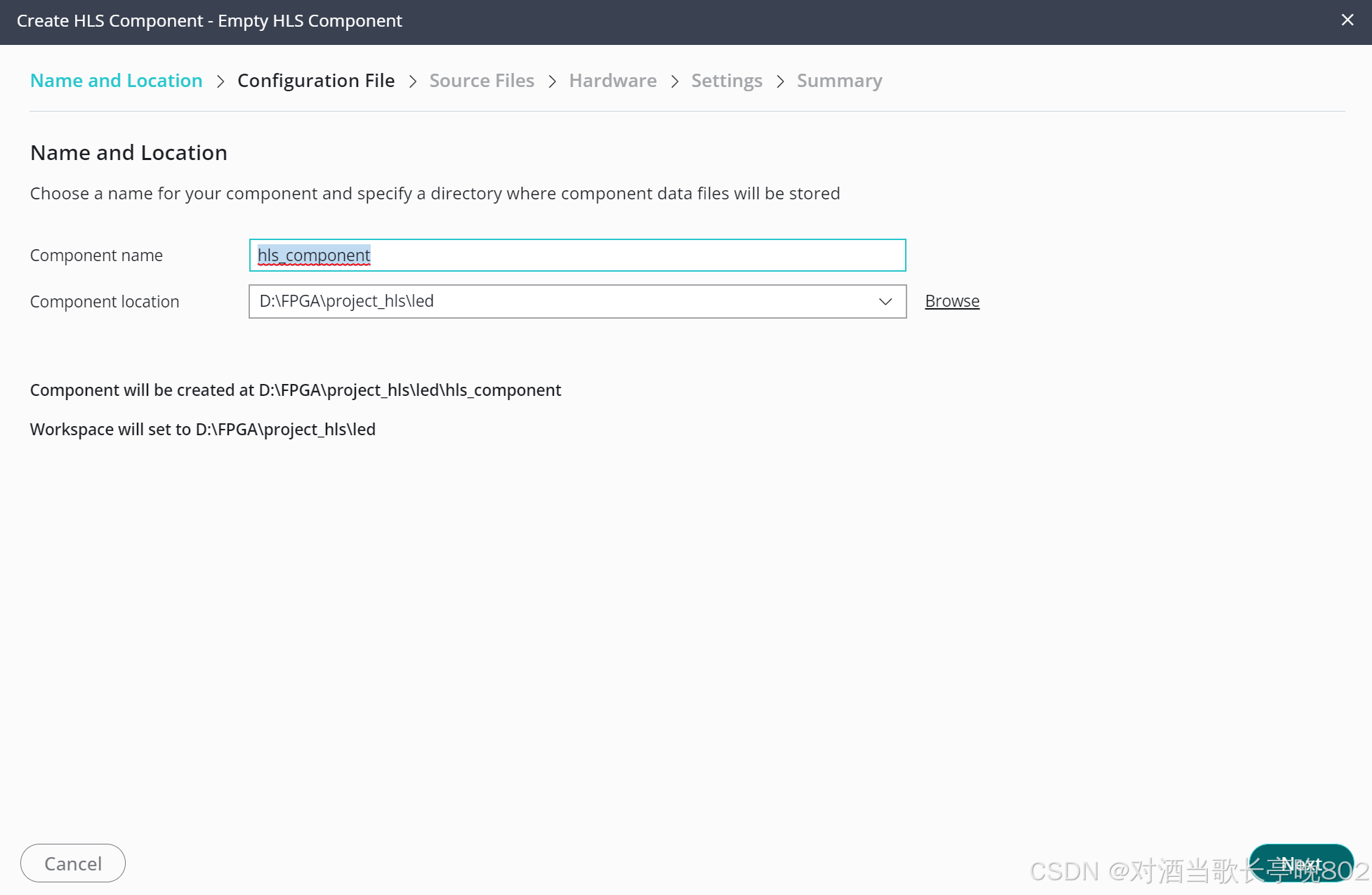

点击create component中的

![]()

|

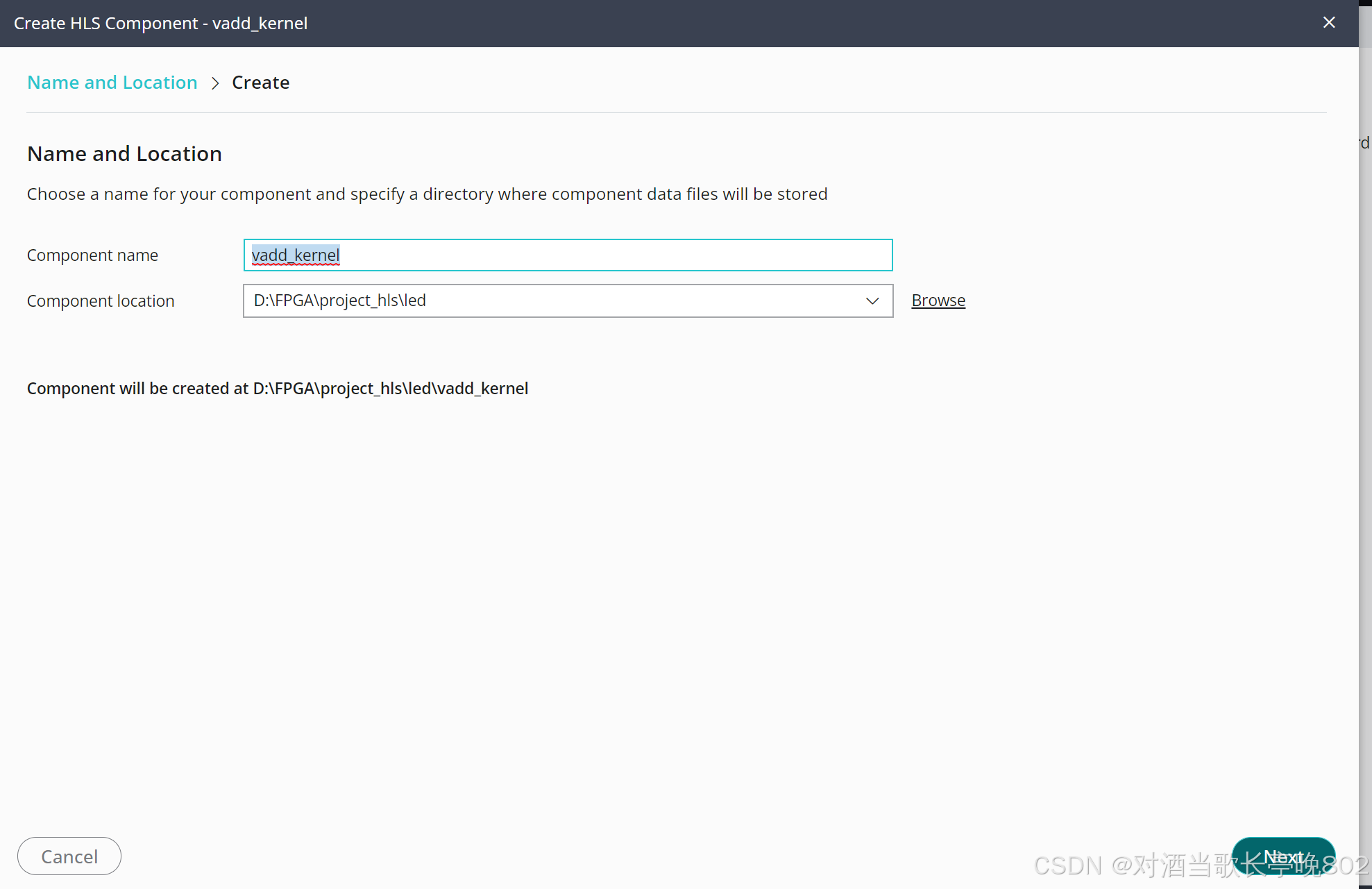

选一个存放地址,要求全英文 |

|

这个地方起你工程的名字 |

进入界面

点击next

|

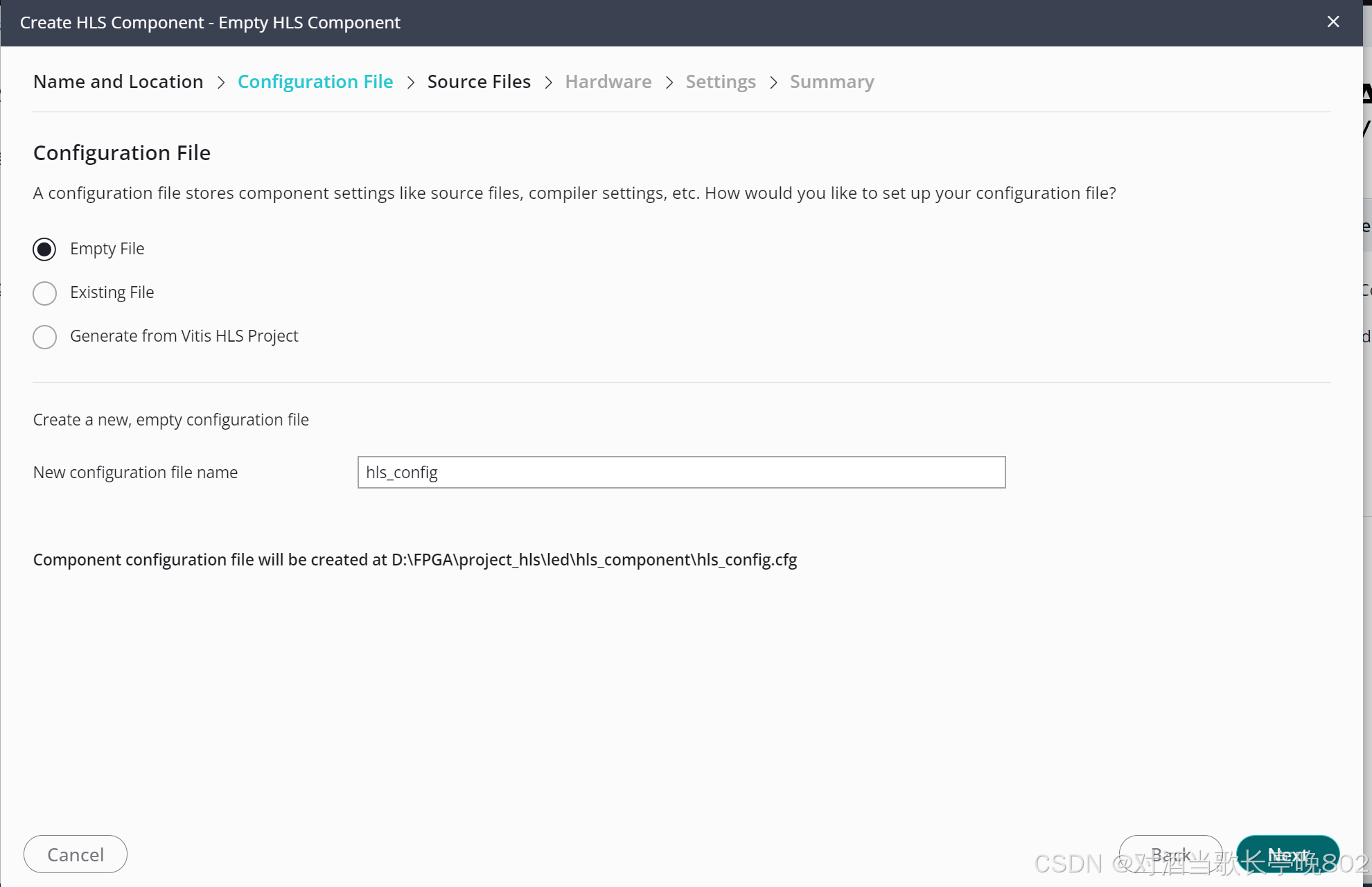

选择你的配置文件名字,一般可以跟工程文件一样 |

点next

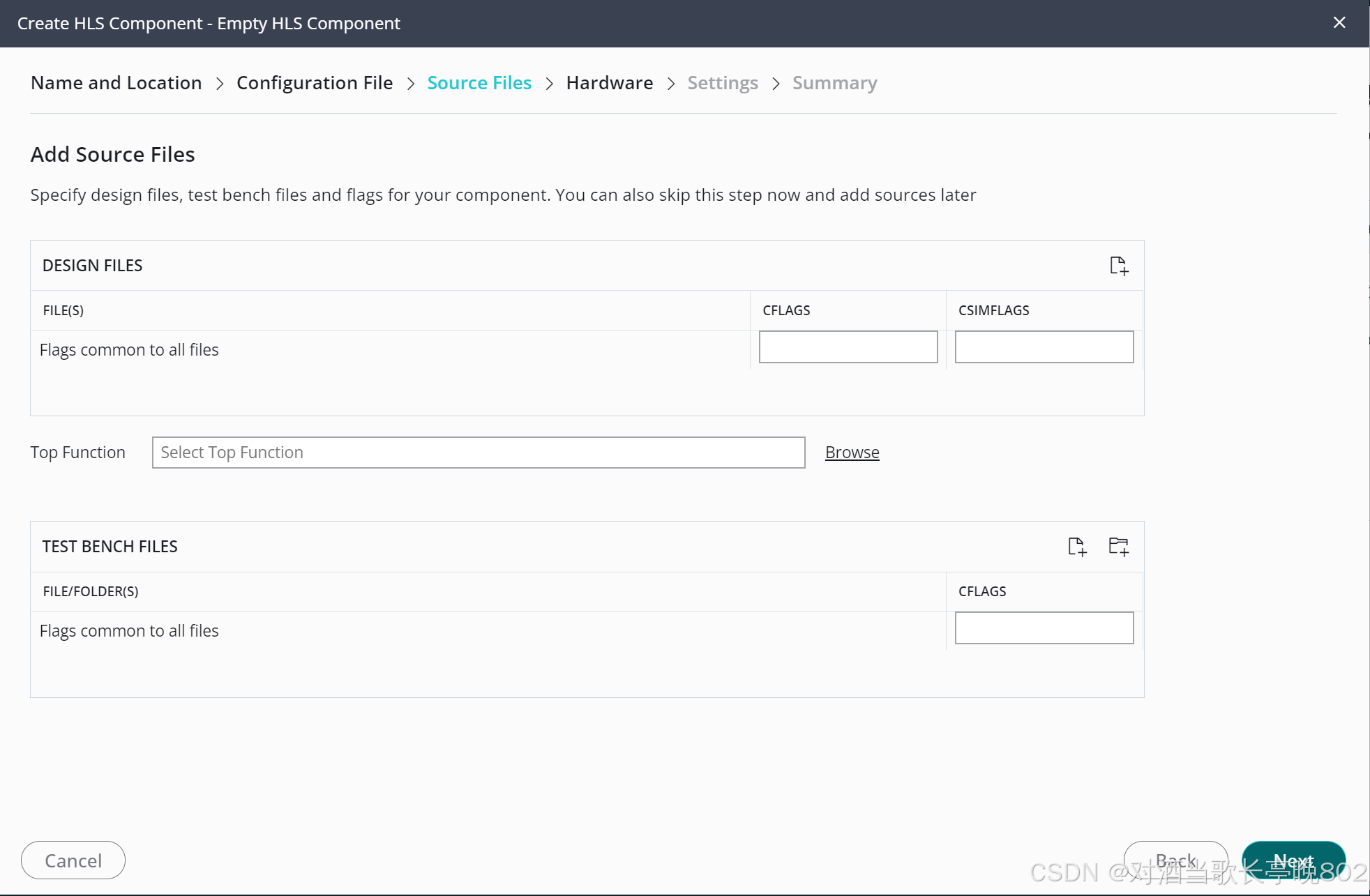

该界面用来加设计文件,可以直接next

|

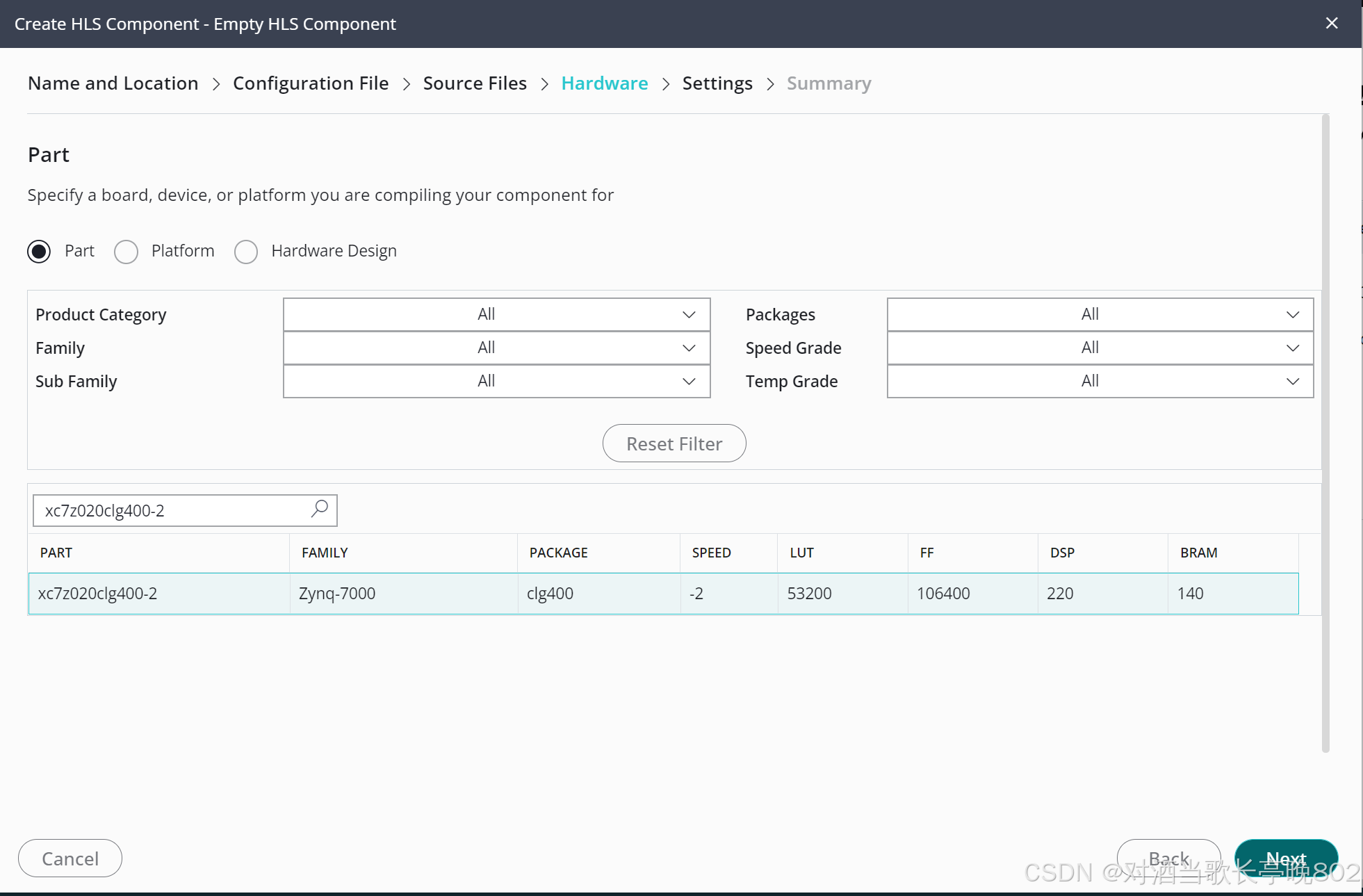

像使用vivado一样输入你的芯片型号,本文以zynq7020为例 |

点next

|

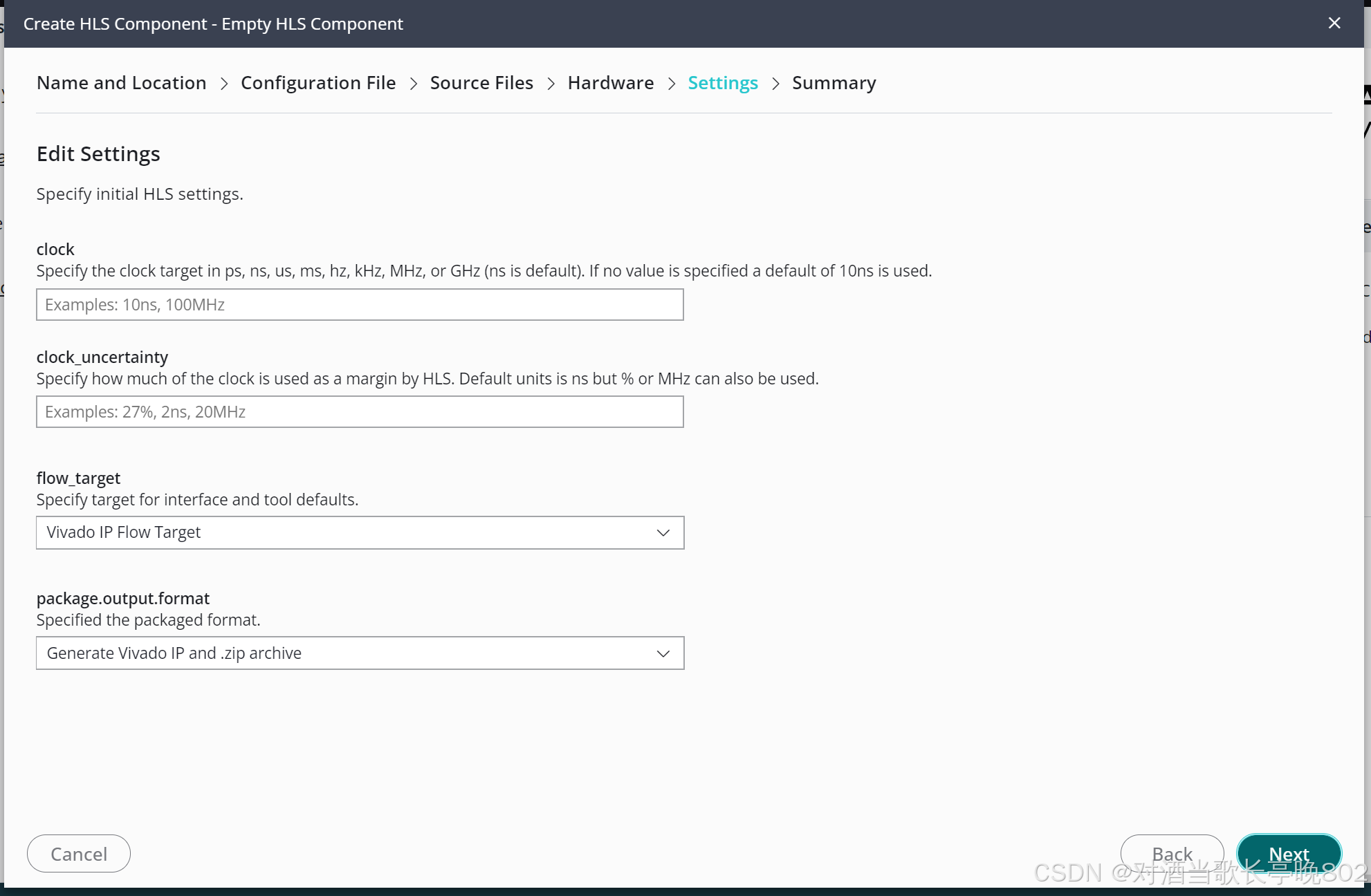

这里写20ns,因为7020板子时钟频率50Mhz |

该界面可以设置时钟频率之类的选项,剩下的可以默认,想要了解可以参考正点原子教程

Next,点finish

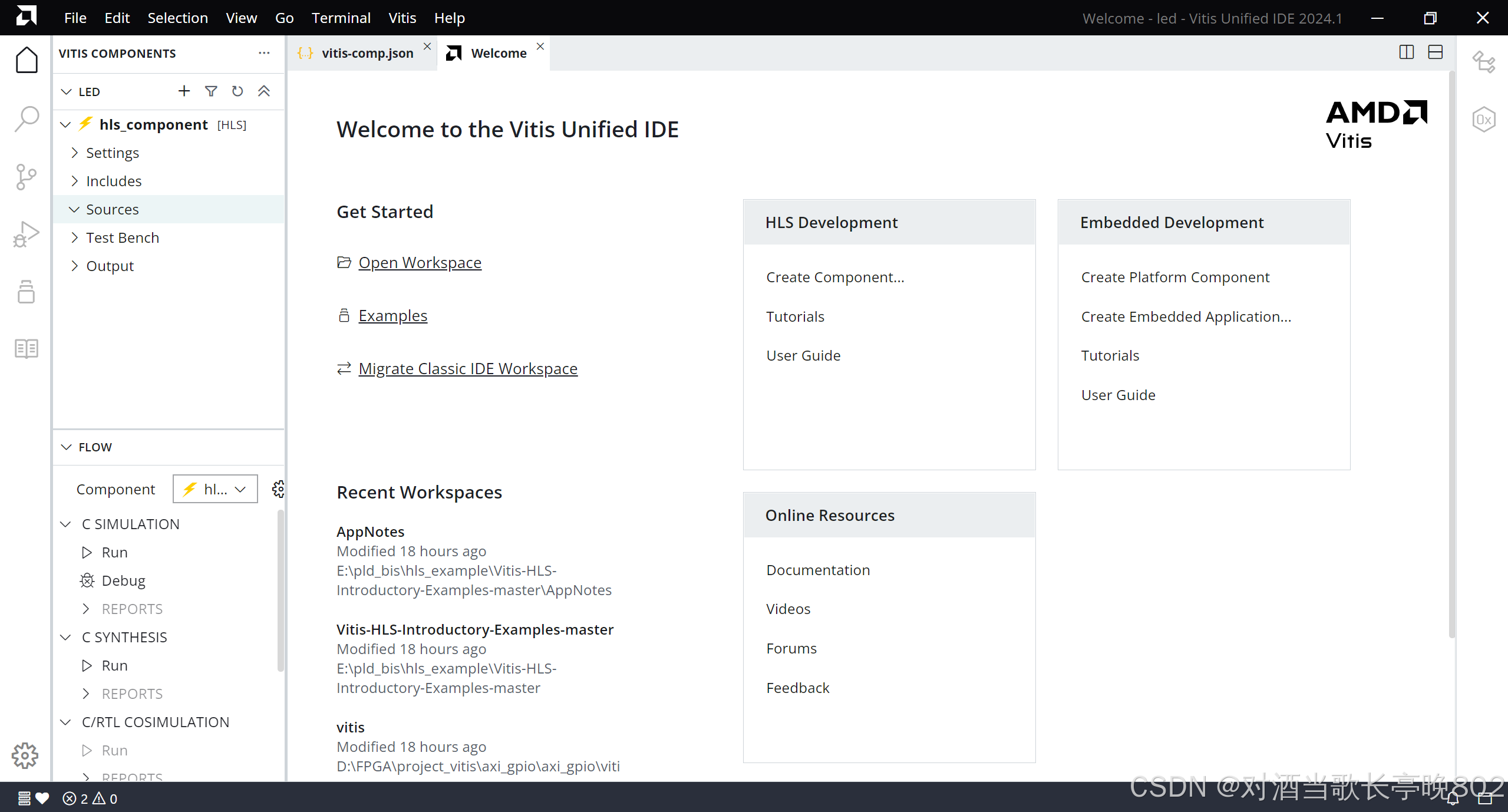

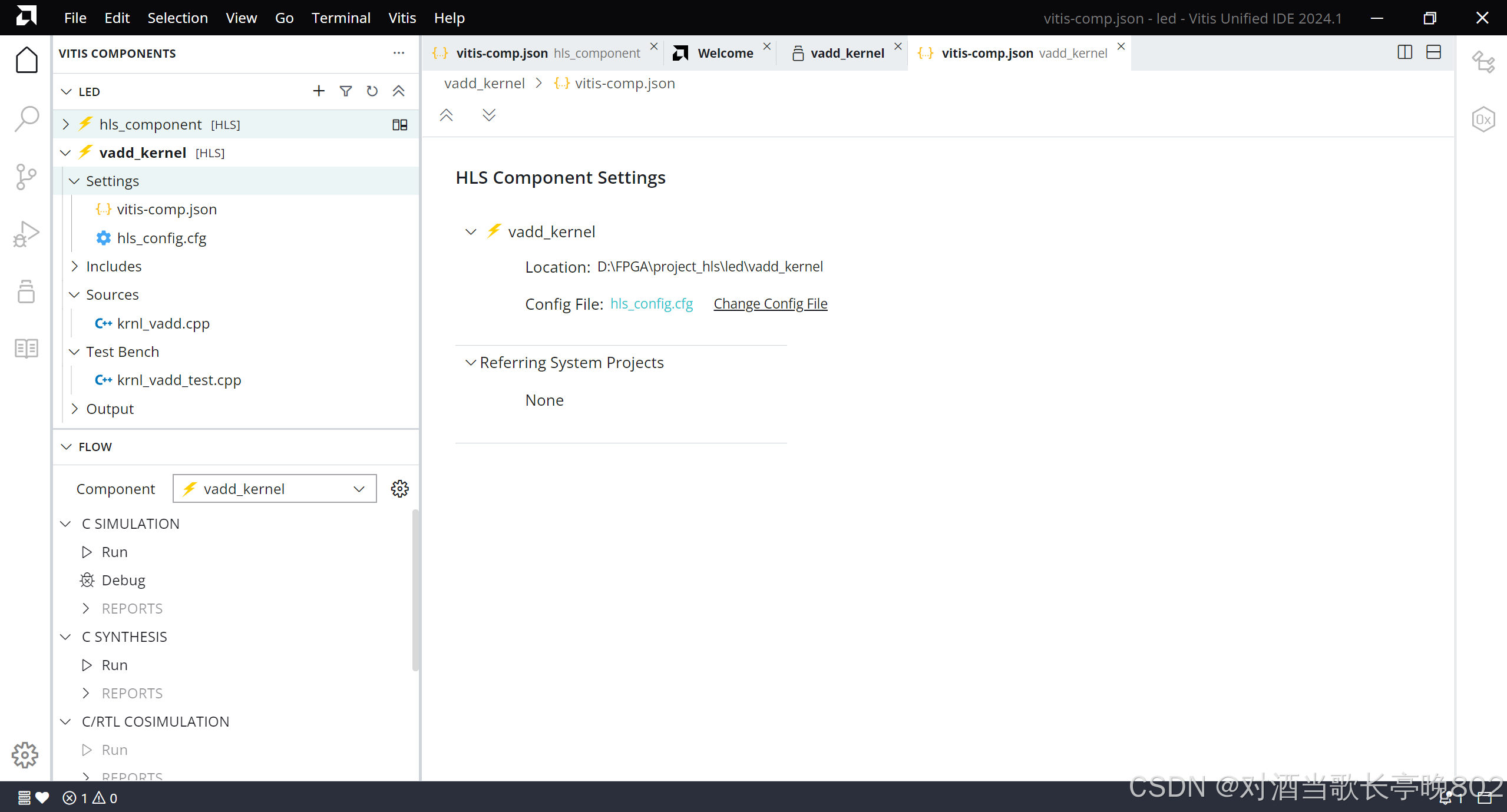

进入该界面,

|

点 |

这个部分可以理解为c++的工程文件夹

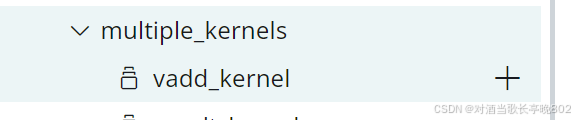

点example打开例程,

点开vadd_kernel,

点+号

点next然后finish

此时我们发现source中有一个文件,点开krnl_vadd.cpp

有一些代码,简略来说实现了c=a+b

我们直接跑分析走流程

首先先点开hls_config.cfg

|

这个是顶层模块,可以点击browse选择函数,或者直接输入,注意:我们需要source内的主函数文件名字与文件内的函数名字一模一样,这样不会有bug |

重中之重:

接下来点击

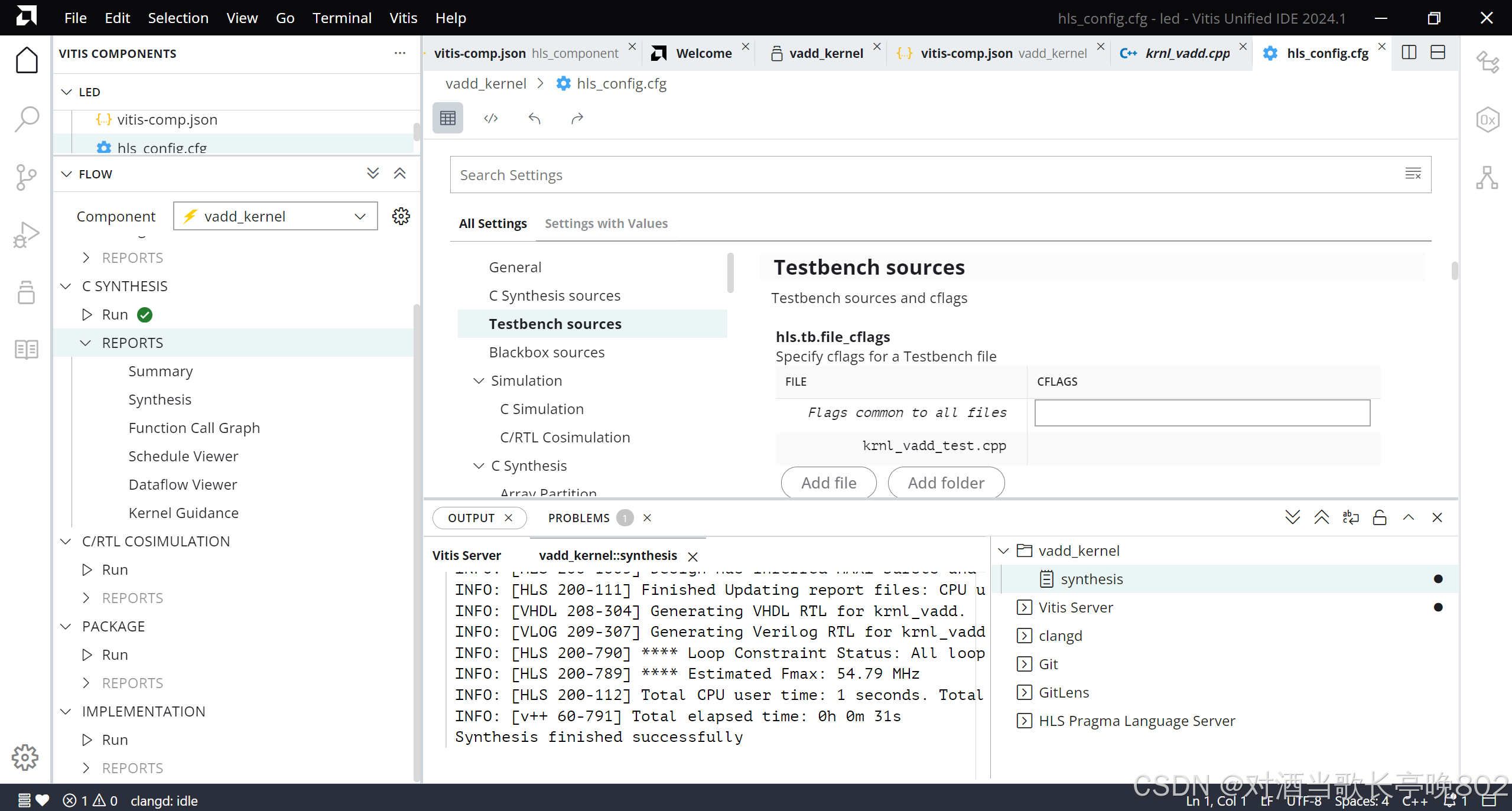

点击C SYNTHESIS内的run进行代码编译,

编译成功后点击

点击package的run,编译成功后即可把该模块变成一个vivado可以使用的IP核

点击

Summary即可看见文件位置,进行使用

本文档完

注:语法使用可以参照示例,仿真文件如何使用可以参照example,具体别的部分有什么用法可以参考本文开头例出的三个参考材料

1568

1568

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?