前言

Vitis HLS,可以通过它,用C和C++建立和封装一个IP核,从Vivado 2021的版本开始内置,用于替代Vivado HLS。

在上一篇文章中(可以点击下面的链接),记录了使用Vitis HLS 构建项目并生成IP核。本文将记录用Vivado验证此IP核。

Vitis HLS 构建项目并生成IP核(Vivado HLS)

新建工程

建立工程

打开软件后,新建一个工程。

设置好项目名和目录。

按照下面的选择。

先不添加源文件,点下一步。

这里添加一个文件。

新建一个XDC文件。

选择器件,我这里使用的是xc7z020clg400-2。

导入IP

到了主界面,选择Setting。

选择前面项目生成的IP核,默认目录下,选到IP这个目录即可,不需要选择zip包。

验证过程

设计文件

添加一个设计文件。

设置好文件名。

添加一个IP核。

搜索后,选择刚刚导入的IP核。

成功添加IP核。

同样的,再添加一个系统自带的IP核,用来做复位设置。

对这个逻辑门设置成一位,同时设置成非门。

设置好的结果。

给LED输出脚添加一个端口。

添加好后。

对它们进行连线,同时添加剩下的端口,重命名成自己想要的名字。

在设计界面右键,验证这个设计。

这个设计没有错误,就可以进行剩下的操作了。

综合设计

选择综合设计。

默认设置即可。

在刚刚的设计文件下,生成了对应的代码文件。

在设计文件上右键,生成HDL Wrapper。

生成后的文件目录,可以自己对照一下看看缺什么,漏了哪一步。

设置XDC

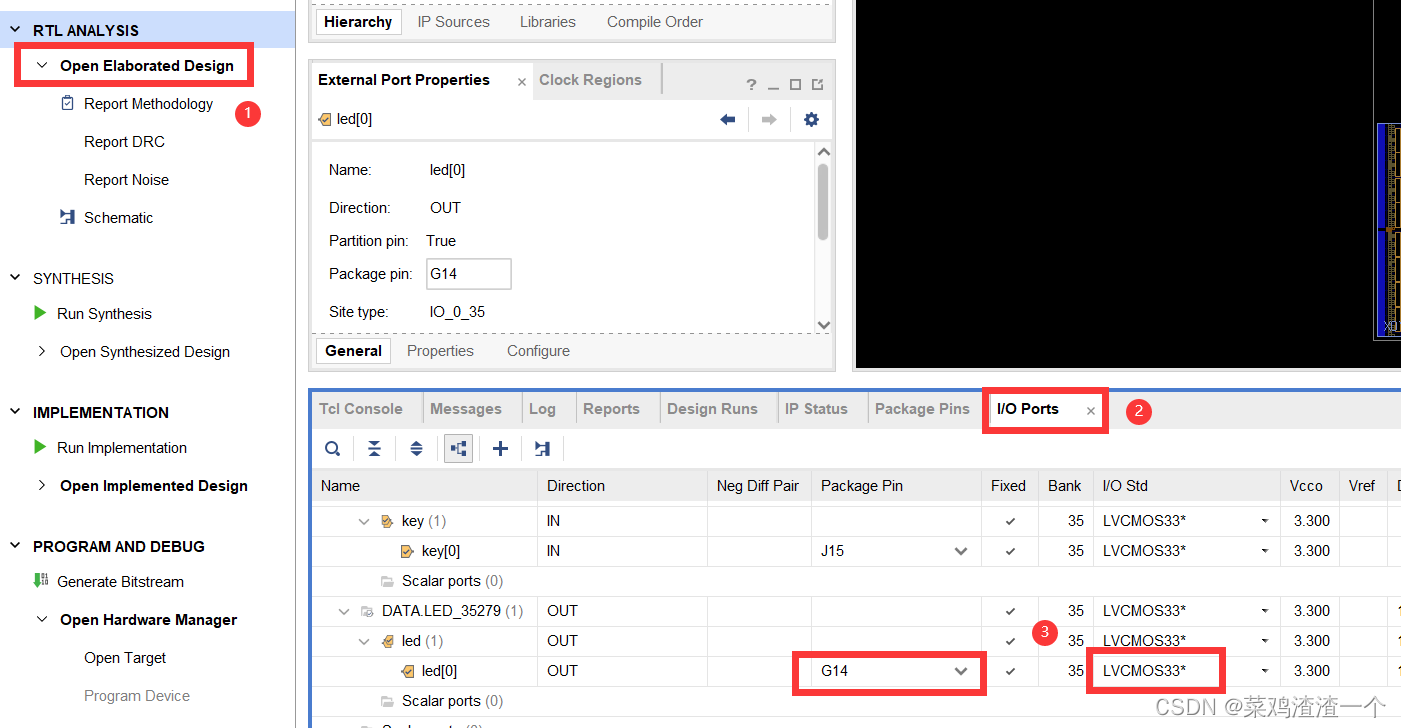

设置XDC,绑定管脚。

对应代码如下。

set_property -dict {PACKAGE_PIN U18 IOSTANDARD LVCMOS33} [get_ports sys_clk]

set_property -dict {PACKAGE_PIN J15 IOSTANDARD LVCMOS33} [get_ports sys_rst_n]

set_property -dict {PACKAGE_PIN G14 IOSTANDARD LVCMOS33} [get_ports {led[0]}]

也可以按下图的顺序,打开"I/O Ports",设置好了后会自动把代码更新到XDC文件中。现在的版本已经没有"I/O Planning"窗口了。

仿真和下载

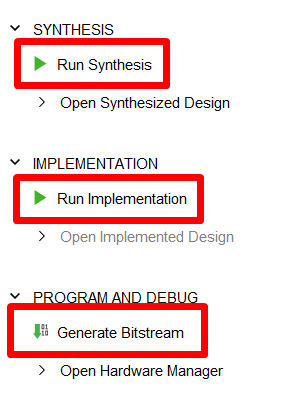

生成比特文件

这里略过波形仿真过程,直接生成比特文件。按顺序运行这三个操作,每一个操作都需要等一段时间才能结束。

下载程序

生成好比特文件后,连接好开发板,按下图的顺序选择,即可将程序下载到开发板中。

最终结果

开发板上的LED灯在闪烁。

2531

2531

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?