设备:zynq7100;

开发环境:window;

vivado版本:2021.1;

一、XDMA ip 简介

XDMA IP(Xilinx Direct Memory Access IP)是赛灵思提供的一款硬件加速器,专为实现高效的直接内存访问(DMA)操作而设计,广泛应用于需要高速数据传输的场合,特别是在FPGA与主机之间或FPGA内部不同模块之间的内存传输。它能够通过PCIe接口进行数据的高速读写,支持多个DMA通道,并提供灵活的数据传输模式,如内存到内存、设备到内存、内存到设备等,可以适应不同的系统架构需求。XDMA具有低延迟和高吞吐量的特点,能够有效提高数据传输效率,减少对主机CPU的依赖,特别适用于实时数据处理、视频处理、数据采集以及云计算和数据中心等应用。通过Xilinx的开发工具如Vivado,开发者可以根据具体需求进行灵活配置,优化传输大小、队列深度等参数,从而提升系统性能和资源利用效率。XDMA IP不仅能加速数据交换,还能支持多种接口,如PCIe和AXI,确保与多种主机系统的兼容,广泛应用于视频、科学计算、机器学习和嵌入式系统等领域。

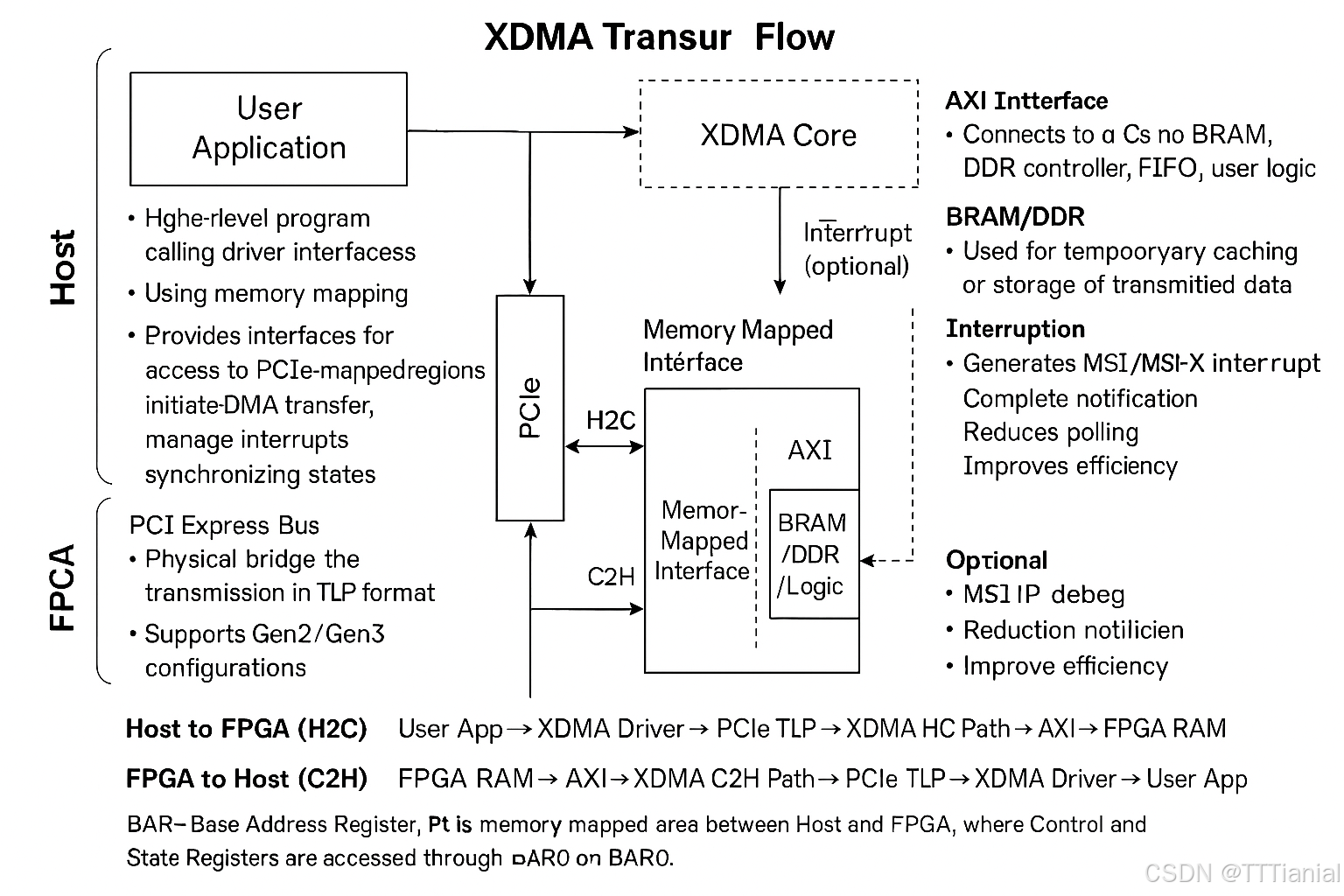

二、传输流程图

这张流程图展示了主机与 Zynq-7100 FPGA 之间通过 XDMA 进行 Memory Mapped 模式下的双向数据传输过程。图中从左到右依次为主机、PCIe 接口和 FPGA 内部三部分。主机端包含用户应用程序和 XDMA 驱动,用户程序通过驱动发起 H2C(主机到卡)或 C2H(卡到主机)数据传输请求。数据通过 PCIe 总线传输至 FPGA,进入 XDMA Core,该核心通过 AXI 总线与 FPGA 内部逻辑(如 BRAM、DDR 或用户模块)连接,实现数据的存取。在传输过程中,可使用中断机制向主机通知传输完成,从而实现高效的数据交互。整张图以清晰的箭头标示了数据流方向,便于理解整个传输链路。

理论知识可以去网上搜索一下,这里不详细介绍了。

三、ip核的配置

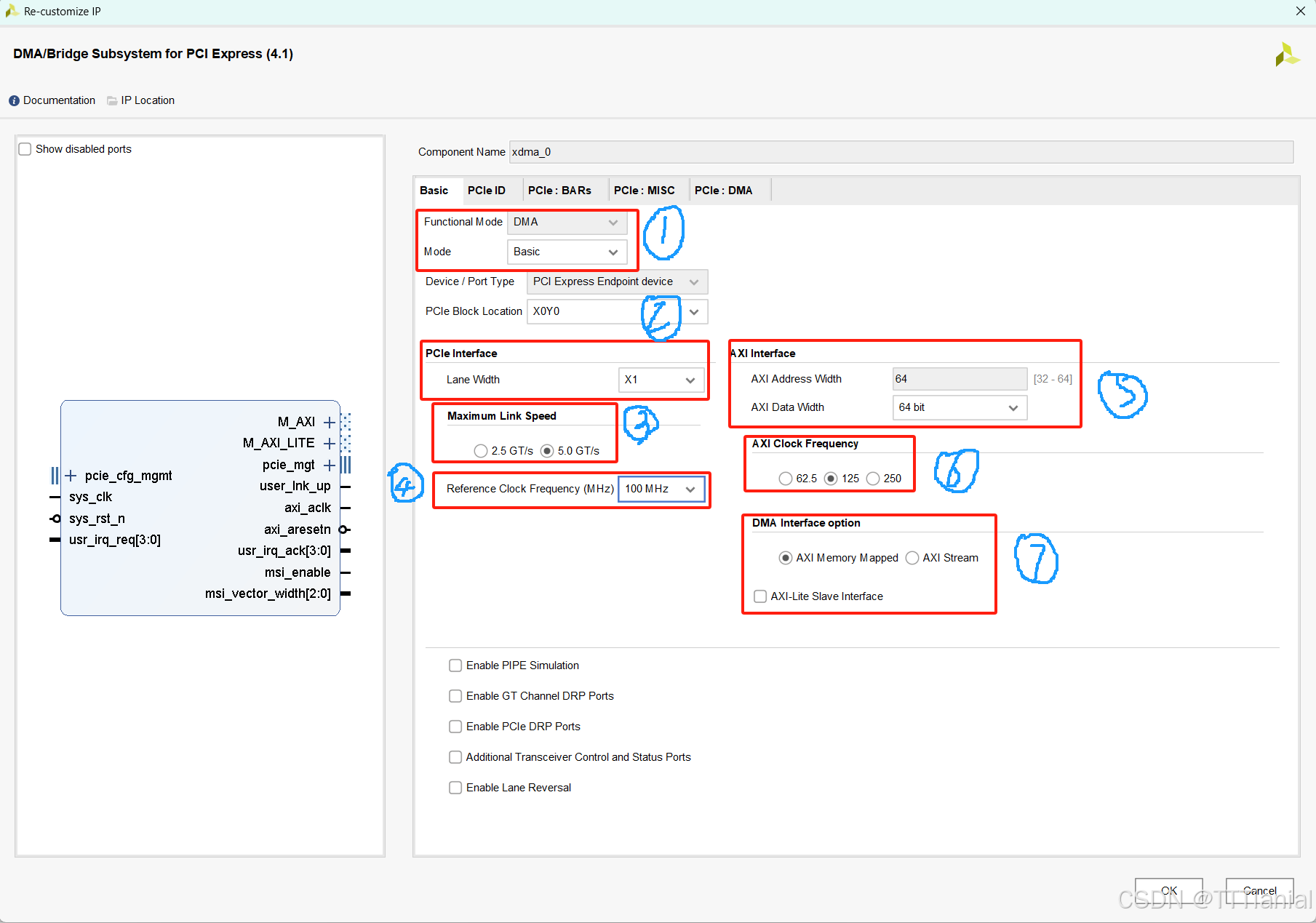

3.1 第一页

1.

Functional Mode(功能模式):即DMA模式。

Mode(模式):basic即可,basic与advanced的区别在于advanced模式开放更多的可选选项与功能,basic的话为默认。

2.

Lane Width(通道宽度):通道宽度,根据硬件接口进行选择,这里我的板子是zynq7100,我只用了一个通道所以我选的X1。

3.

Maximum Link Speed(最大链路速度):子系统需要选择 PCIe Gen 速度。我这里选择的5.0GT/s。

4.

Reference Clock Frequency(参考时钟频率):默认值为 100 MHz,但也支持125 MHz 和 250 MHz。保持默认就好。

5.

AXI Data Width(AXI 数据宽度):选择 64、128、256 位或 512 位,我这里选择的是64位。

6.

AXI Clock Frequency(AXI 时钟频率):根据通道宽度/速度,可选择 62.5 MHz、125 MHz 或 250 MHz。

这里我选择的是125Mhz

7.

DMA Interface Option(DMA 接口选项):选择 AXI4 存储器映射或 AXI4-Stream。

其余为默认就好了(有兴趣可以研究一下)

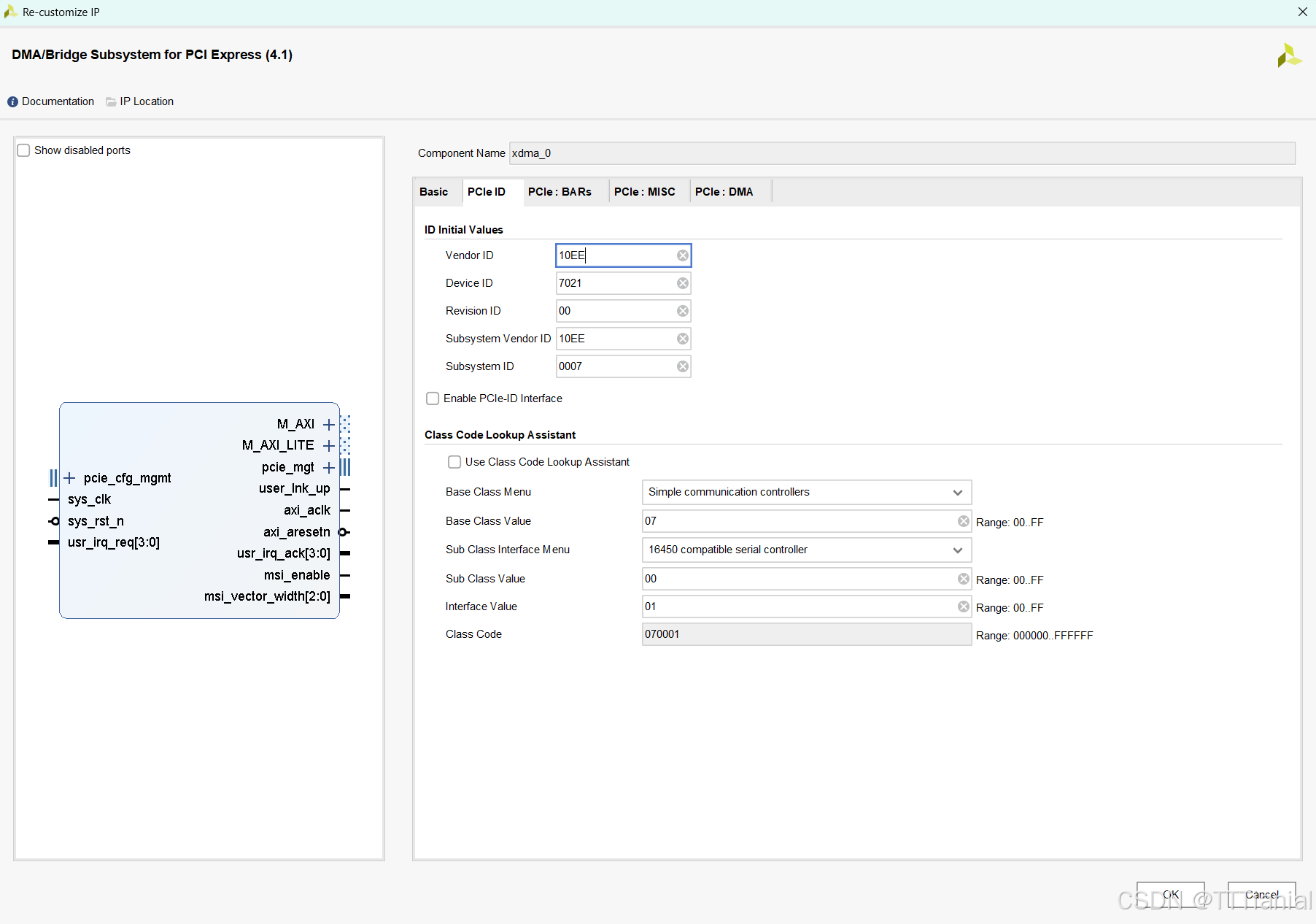

3.2 第二页

这一页一般保持默认。

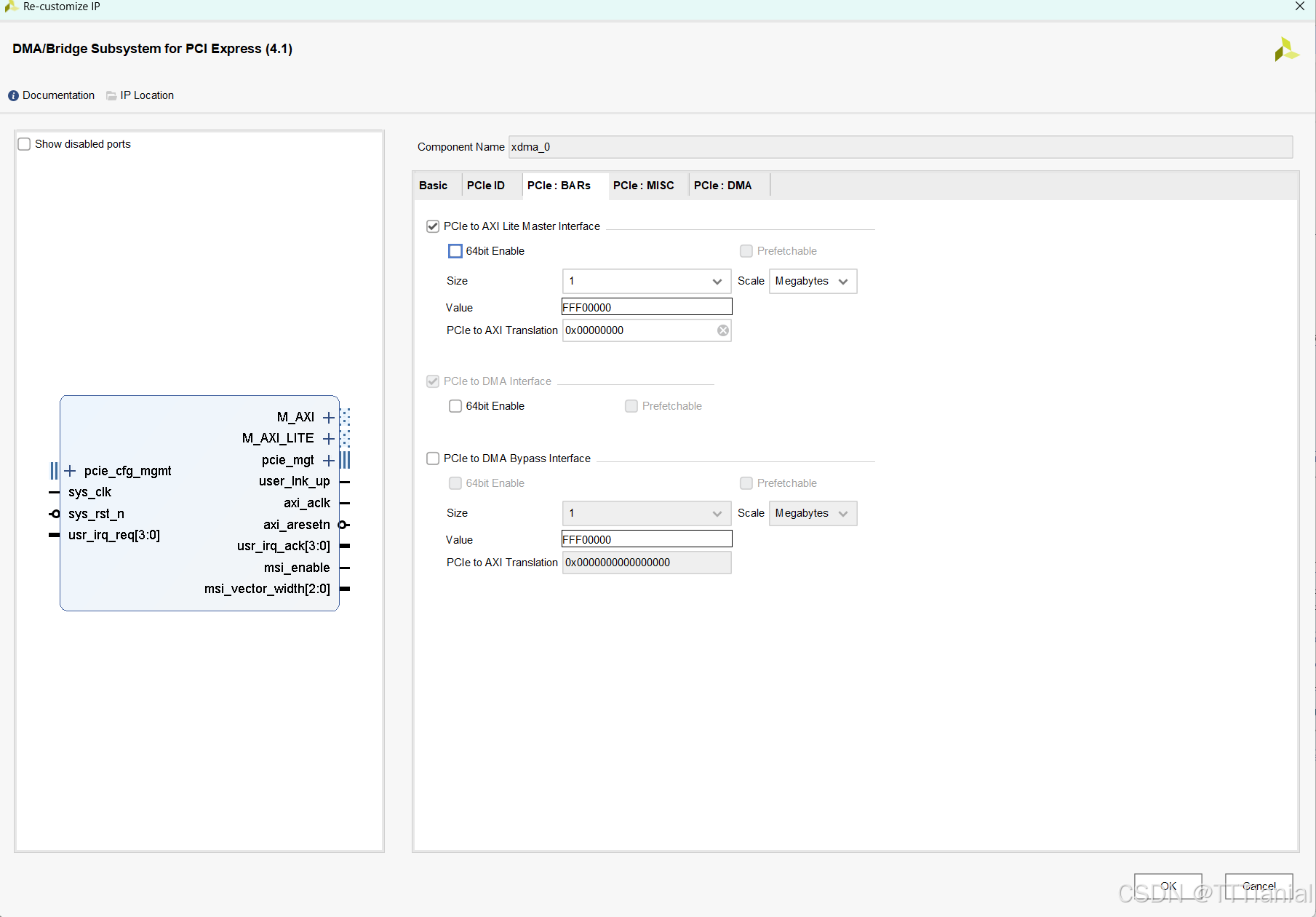

3.3 第三页

📂 页面标题:

PCIe : BARs

用于配置主机通过 PCIe 访问 FPGA 的内存区域(BAR 区域),以及这些区域映射到 AXI 总线的哪部分。

🔘 选项详解:

✅ PCIe to AXI Lite Master Interface(已勾选)

表示启用 AXI Lite Master 接口,通常用于寄存器读写、状态控制等。主机通过此接口访问 FPGA 内部的寄存器空间。

子选项:

64bit Enable(未勾选)

启用时代表 BAR 是 64-bit 地址;未启用就是 32-bit 地址,兼容性更好。

Size:1 Megabytes

指 BAR 的大小是 1MB,也就是主机能通过该 BAR 访问 1MB 的 AXI 地址空间。

Value:FFF00000

是 Vivado 内部用于生成 BAR 地址掩码的参数,不需要手动修改。

PCIe to AXI Translation:0x0000000000000000

表示 PCIe 地址空间的起始地址会被映射到 AXI Lite 的地址 0x0 处。

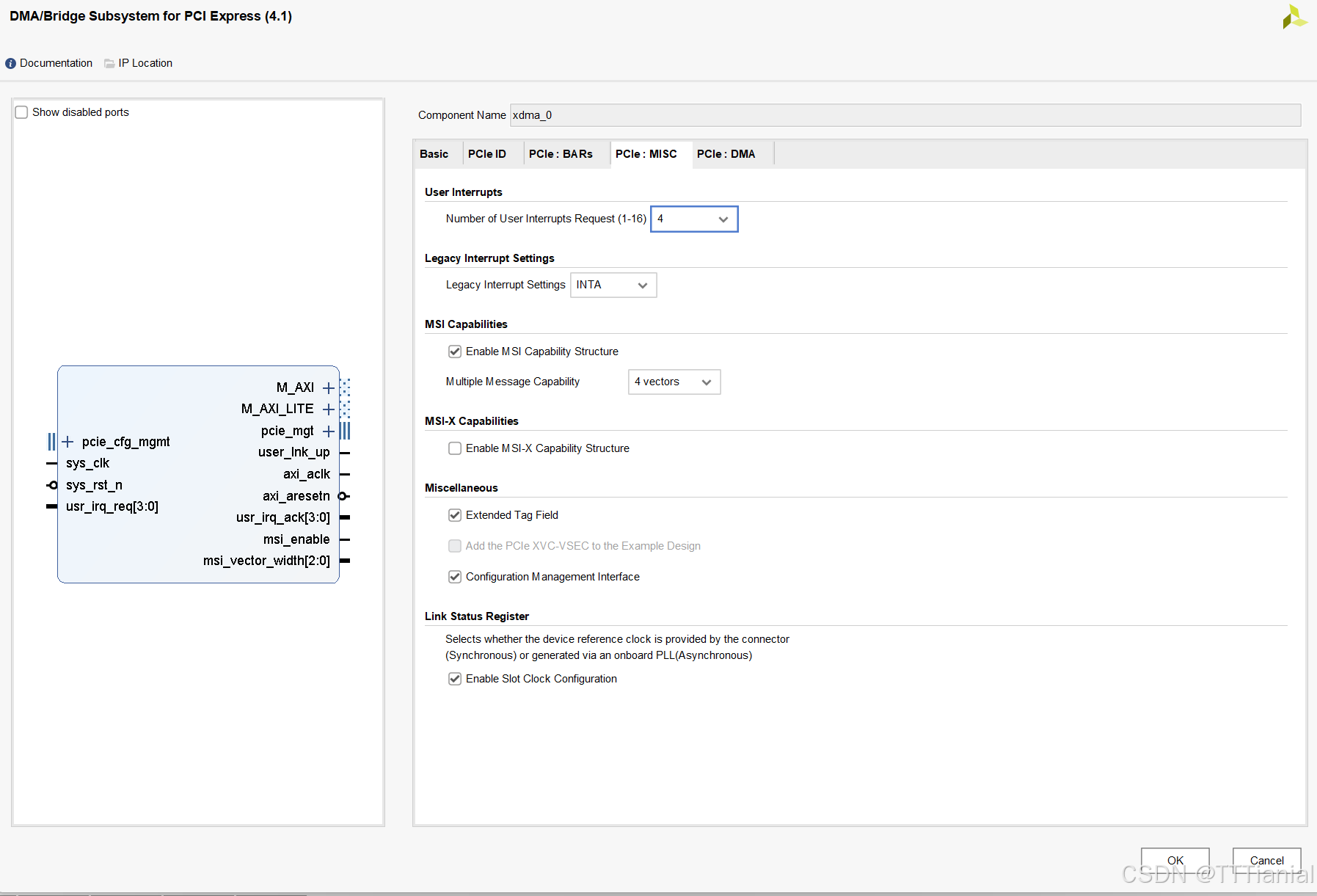

3.4 第四页

🧩 User Interrupts(用户中断)

Number of User Interrupts Request (1–16): 4

配置用户可用的中断数量,这里设置为 4 路中断,对应信号为 usr_irq_req[3:0] 和 usr_irq_ack[3:0]。

这些中断用于在 FPGA 中的逻辑向主机通知某些事件(如:DMA 传输完成、缓冲区就绪等)。

🔔 Legacy Interrupt Settings(传统中断设置)

Legacy Interrupt Settings: INTA

表示启用传统 PCIe 中断方式(INTA#),一般较旧,延迟较高,现在常用 MSI 或 MSI-X 替代。

⚡ MSI Capabilities(Message Signaled Interrupt,中断消息能力)

✅ Enable MSI Capability Structure(启用 MSI)

勾选后启用 PCIe 的 MSI(消息信号中断) 机制,较传统中断方式更快且支持多个中断向量。

Multiple Message Capability: 4 vectors

表示主机驱动可以识别最多 4 个不同的中断向量,与前面设置的 4 路用户中断一致。

主机可以根据不同的中断号作出不同处理,比如:分别处理 C2H、H2C、错误标志、状态通知等。

💡 MSI-X Capabilities(可扩展消息中断)

⬜ Enable MSI-X Capability Structure

当前未启用。MSI-X 是 MSI 的扩展,支持更多向量(最多 2048),更灵活但配置更复杂。通常 MSI 就已足够。

🧰 Miscellaneous(杂项功能)

✅ Extended Tag Field(扩展标签字段)

允许 PCIe 使用更多 tag(通常是从 32 增加到 256),提高系统在高并发时的性能,建议启用。

⬜ Add the PCIe XVC-VSEC to the Example Design

这是给调试工具用的,添加 Xilinx 虚拟扩展配置(VSEC),一般不启用,除非调试需要。

⬜ Configuration Management Interface

如果你需要在运行时动态配置 PCIe(比如读取或写入配置空间),可以勾选,默认不开。

🕒 Link Status Register(链路时钟配置)

✅ Enable Slot Clock Configuration(启用槽时钟配置)

允许设备使用 PCIe 插槽提供的参考时钟进行同步,这是标准的同步 PCIe 时钟使用方式,推荐保持勾选。

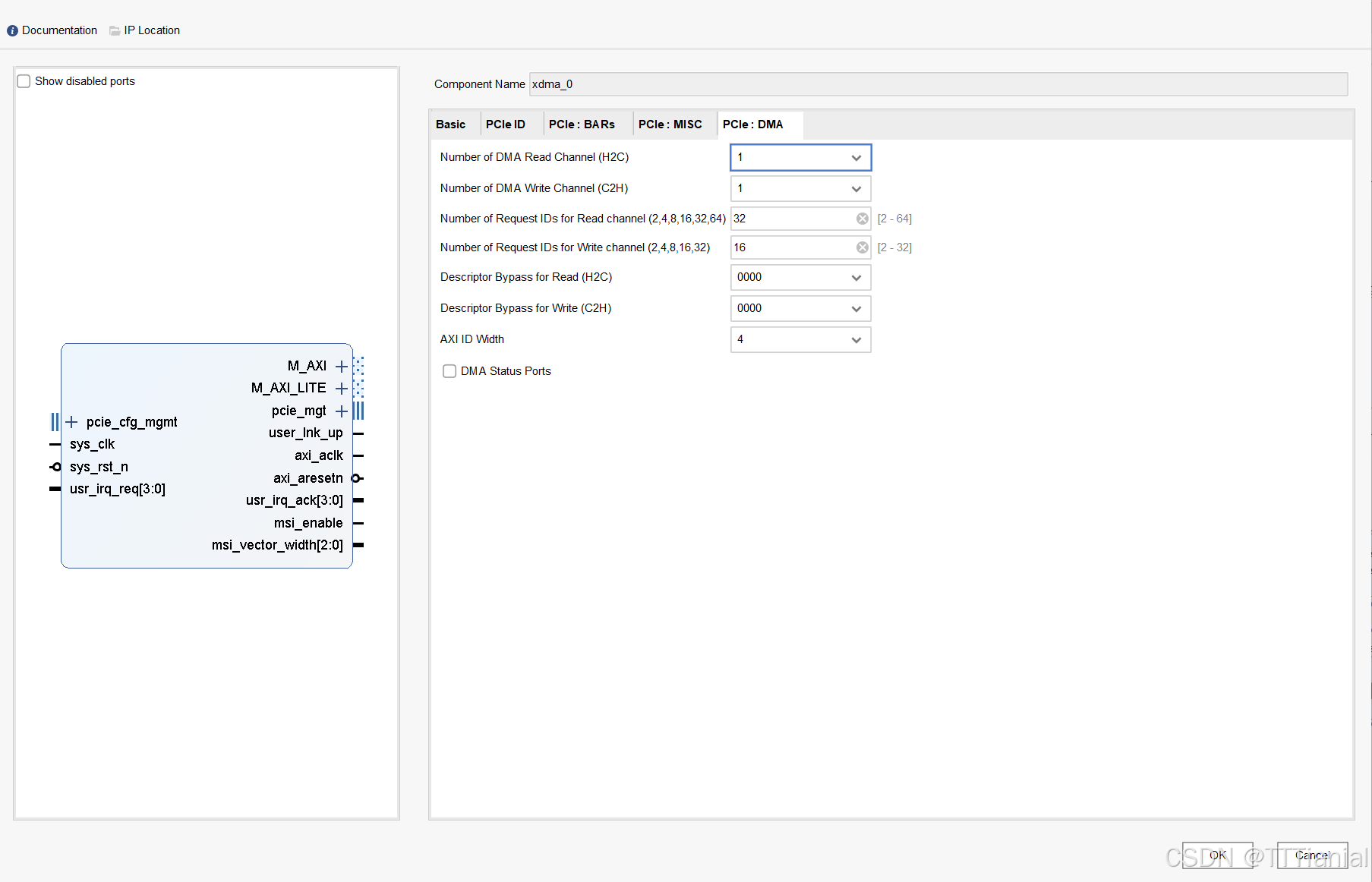

3.5 第五页

🔁 Number of DMA Read Channel (H2C)

设置为 1:表示主机(Host)到卡(Card)的 DMA 读通道数量为 1 个。

H2C:Host to Card,也就是主机将数据通过 PCIe 发送给 FPGA。

🔂 Number of DMA Write Channel (C2H)

设置为 1:表示从卡(FPGA)到主机的 DMA 写通道为 1 个。

C2H:Card to Host,通常用于将采集/计算结果回传给 PC。

🧮 Number of Request IDs for Read Channel (2–64)

固定为 32(不可修改):这是 AXI Master 通道向主机发起读取请求时的 tag 数量(Outstanding requests)。

理解:可以看作同时在飞的读请求个数,多有利于流水线性能。

🧮 Number of Request IDs for Write Channel (2–32)

设置为 16:表示最多同时进行的写请求数量。

建议:对数据写回 PC 有帮助,越高越能提升带宽利用率,但也会占用更多资源。

⚙️ Descriptor Bypass for Read (H2C) / Write (C2H)

都是 0000(默认值):

含义是 是否启用描述符旁路(Bypass)模式。此模式允许你直接在 FPGA 端控制 DMA 的地址和长度,而不是用软件控制。

默认关闭,使用标准的描述符链表控制方式。

✅ 使用建议:

若你要自己控制 DMA 启动、地址、长度(即“旁路模式”),这里需要启用特定位。

若你使用标准 Linux 驱动或 Xilinx 提供的 XDMA 驱动,保留 0000 即可。

📌 AXI ID Width

设置为 4:AXI 总线的事务 ID 位宽(通常为 4/5/6 位)。

影响 AXI 多事务并发能力。

建议:保留默认 4 即可,除非你自己写了高并发的 AXI 从属设备。

📊 DMA Status Ports

⬜ 未勾选:表示不启用额外的 DMA 状态端口。

若勾选,会多出一组端口用于表示当前 DMA 状态,比如忙/空闲/完成等。

建议:

如你需要在 FPGA 内部判断 DMA 是否完成、处于空闲等状态,可以勾选;

否则不勾选,逻辑更简单。

至此XDMA的配置已经完成,下面我们配置ddr的。

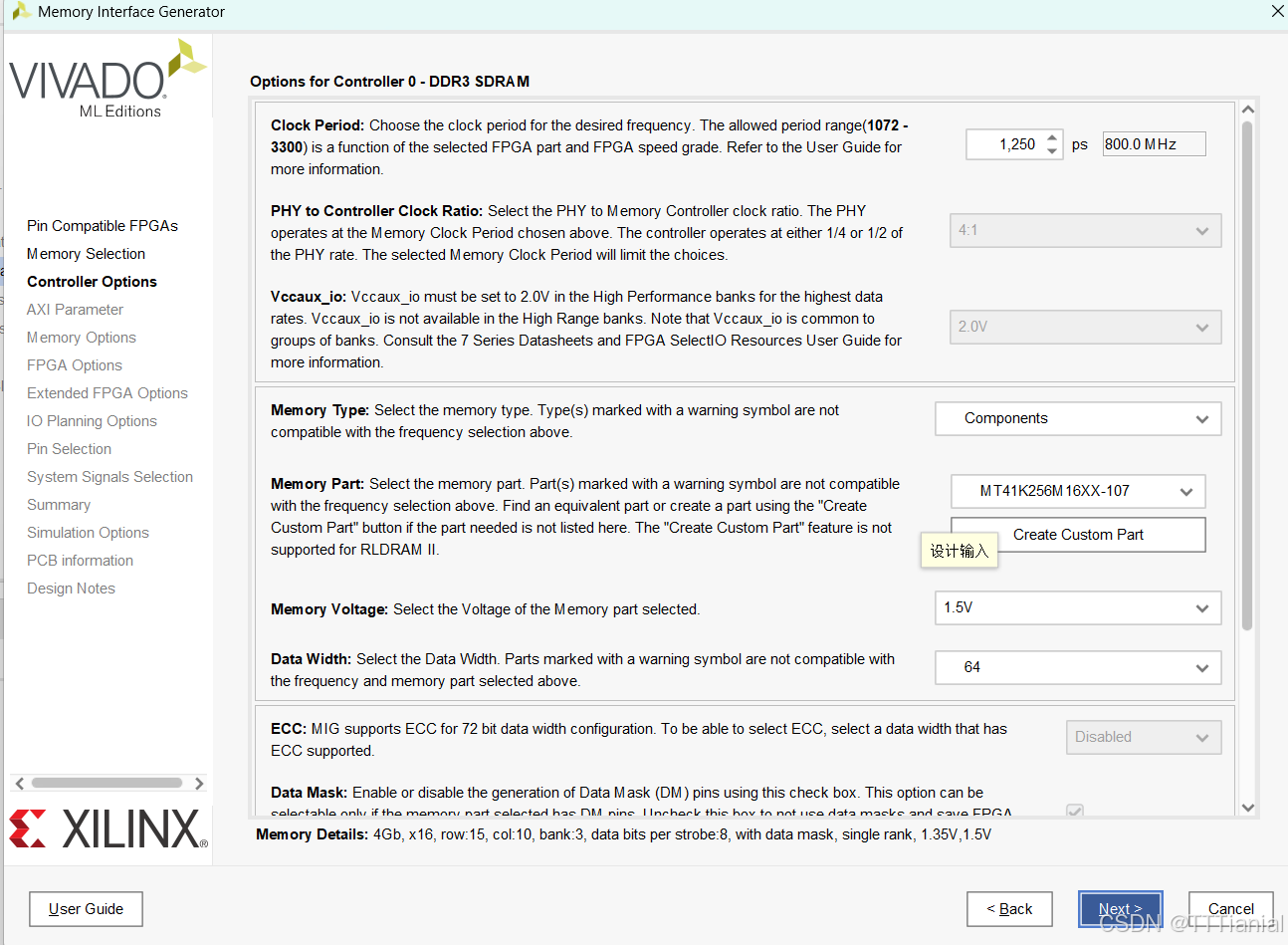

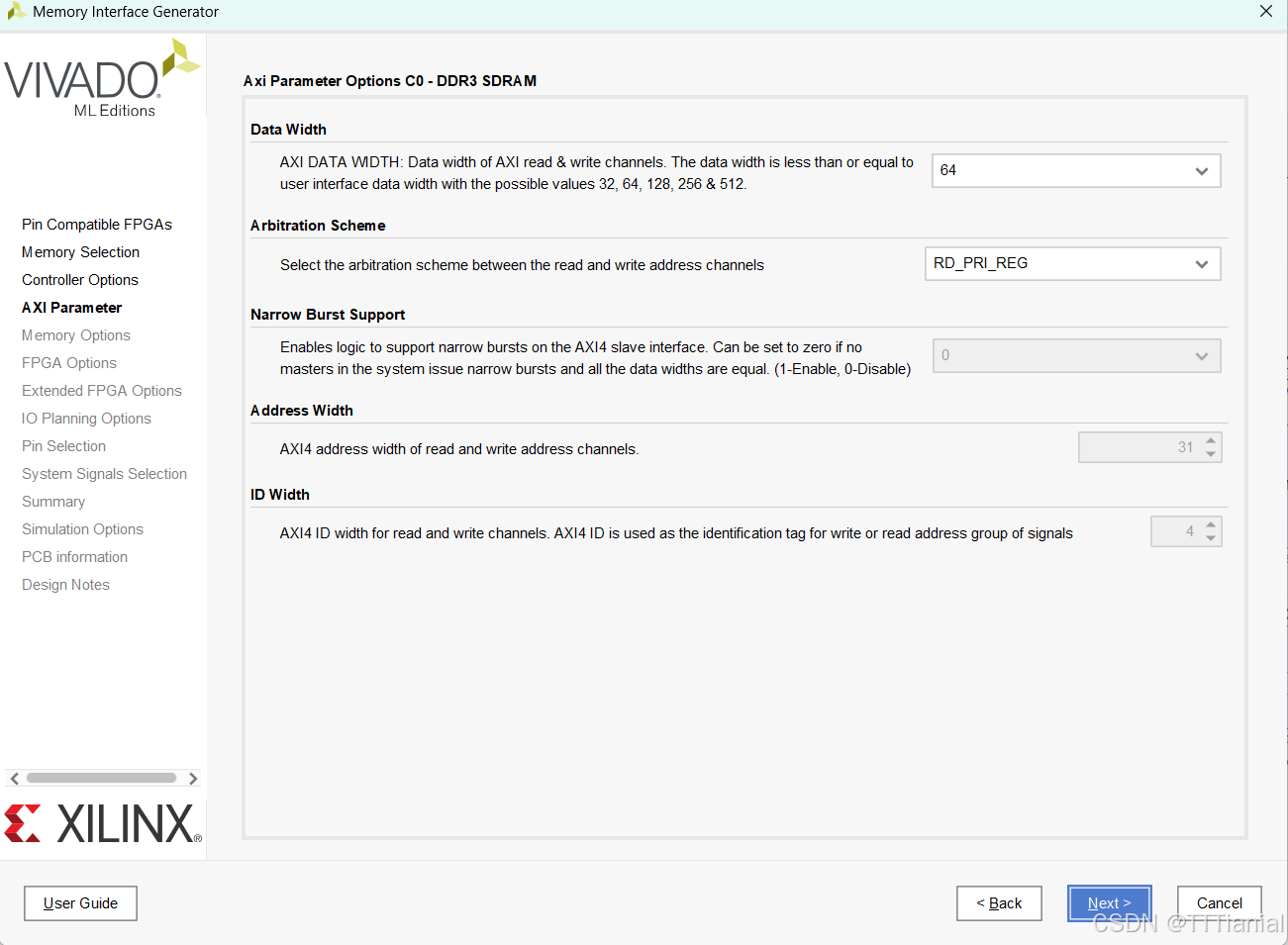

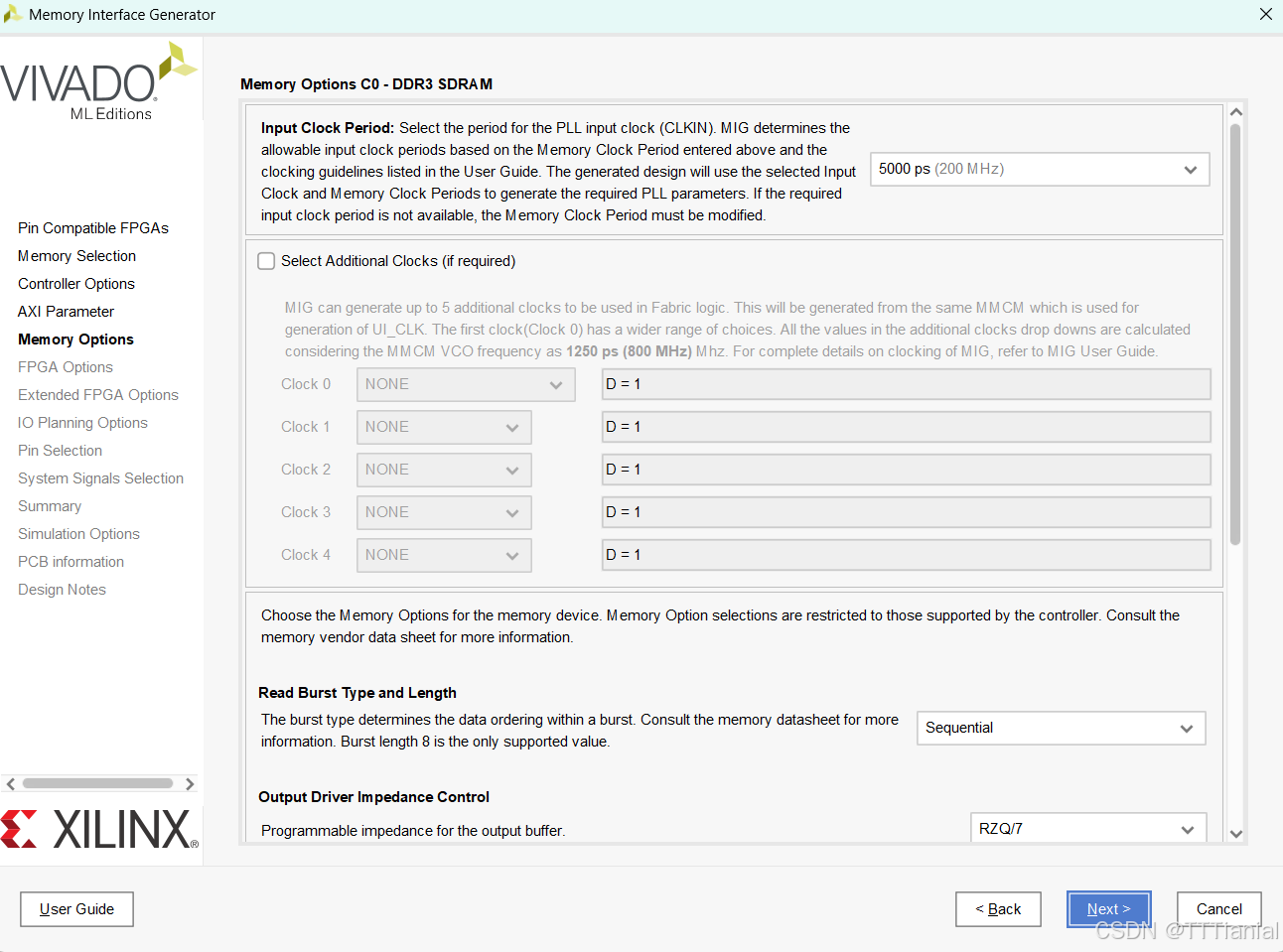

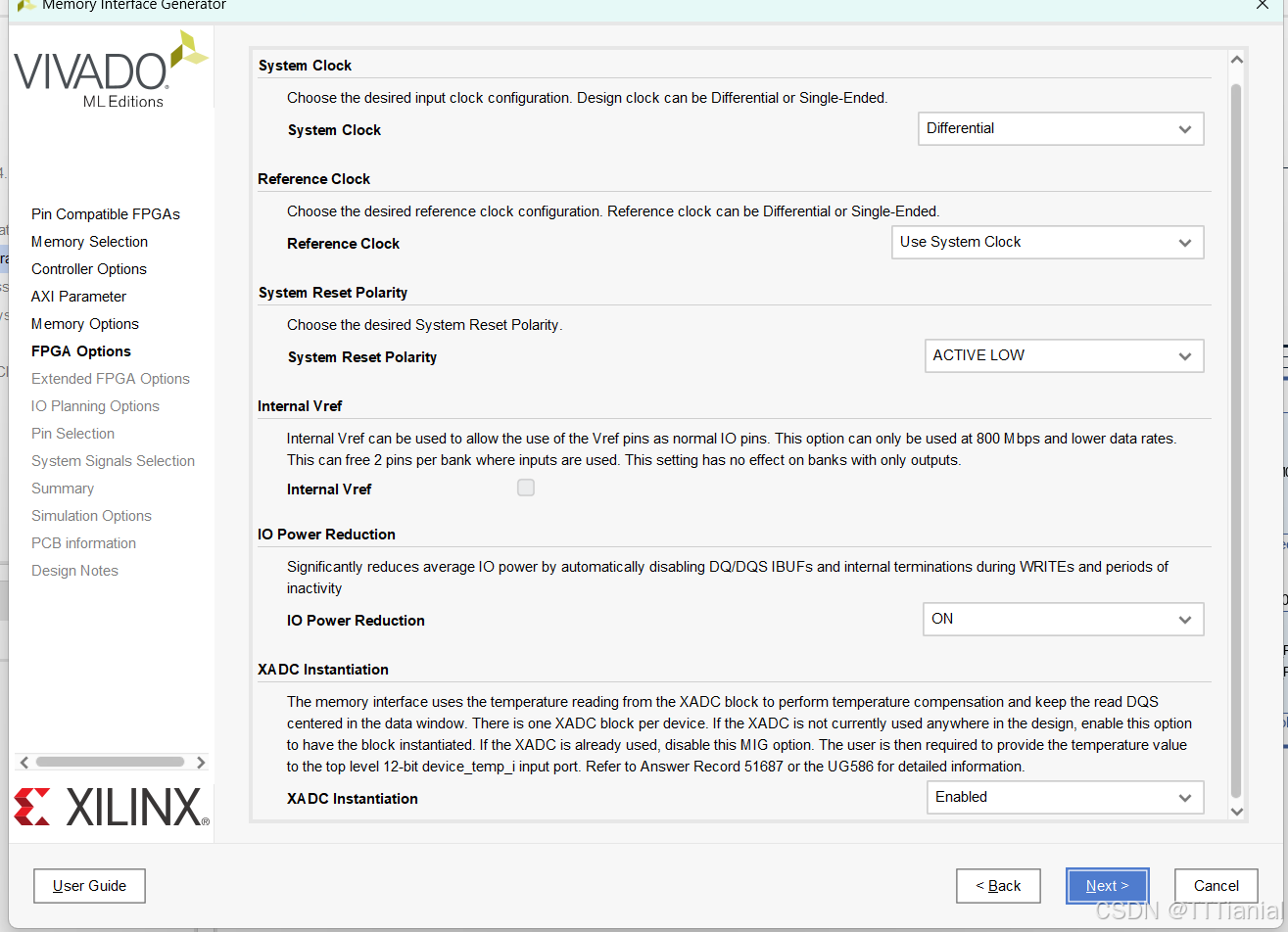

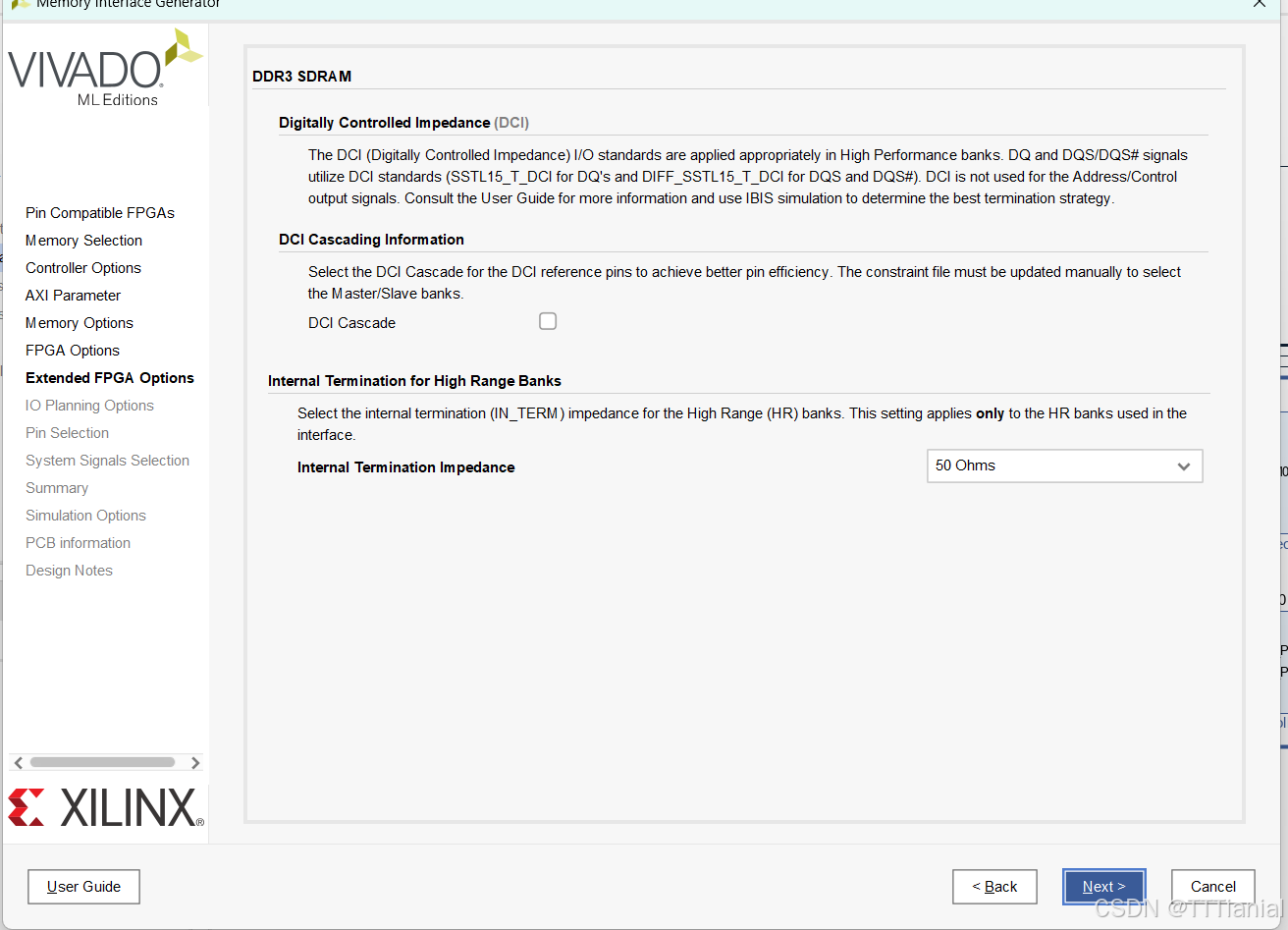

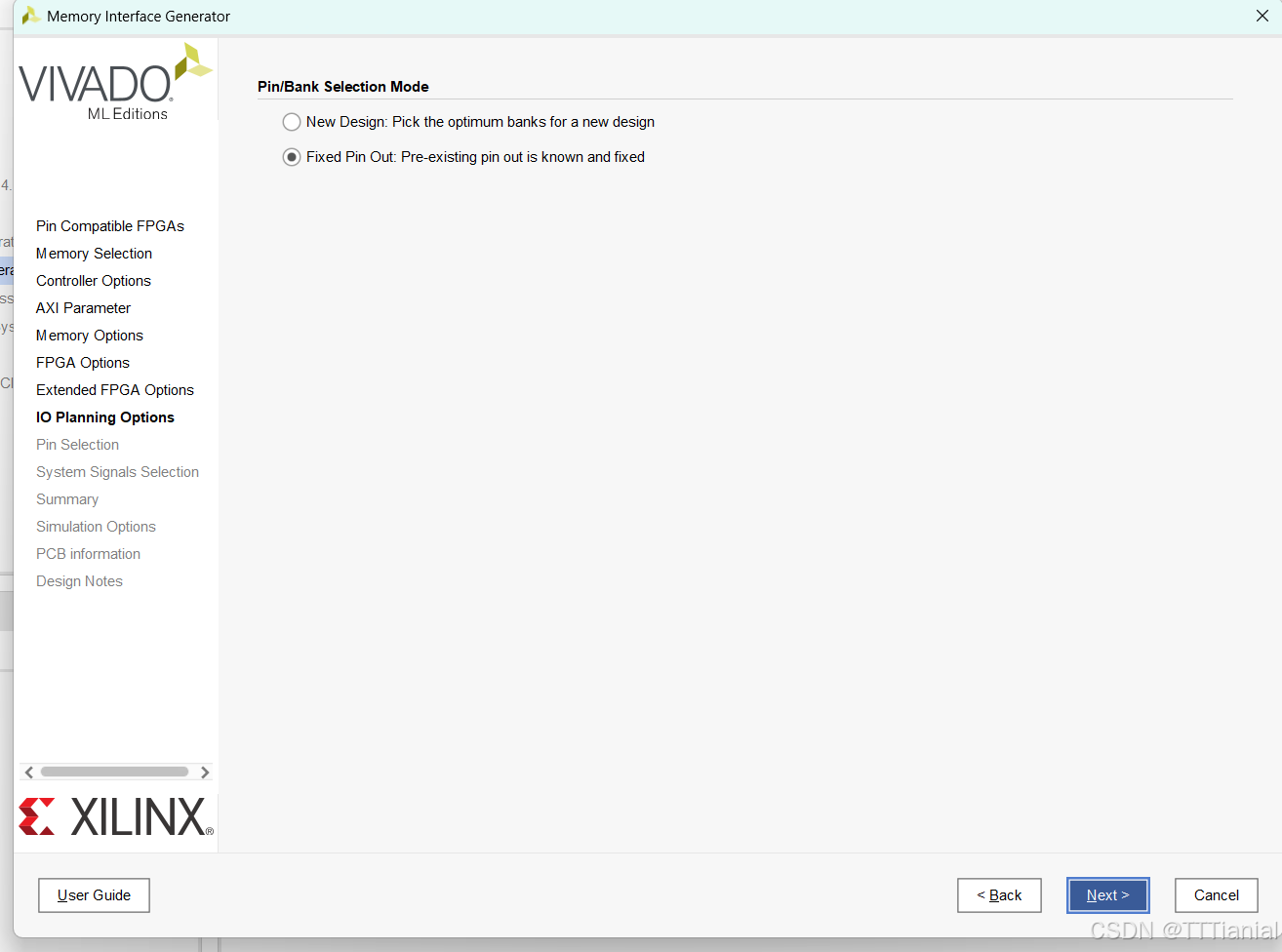

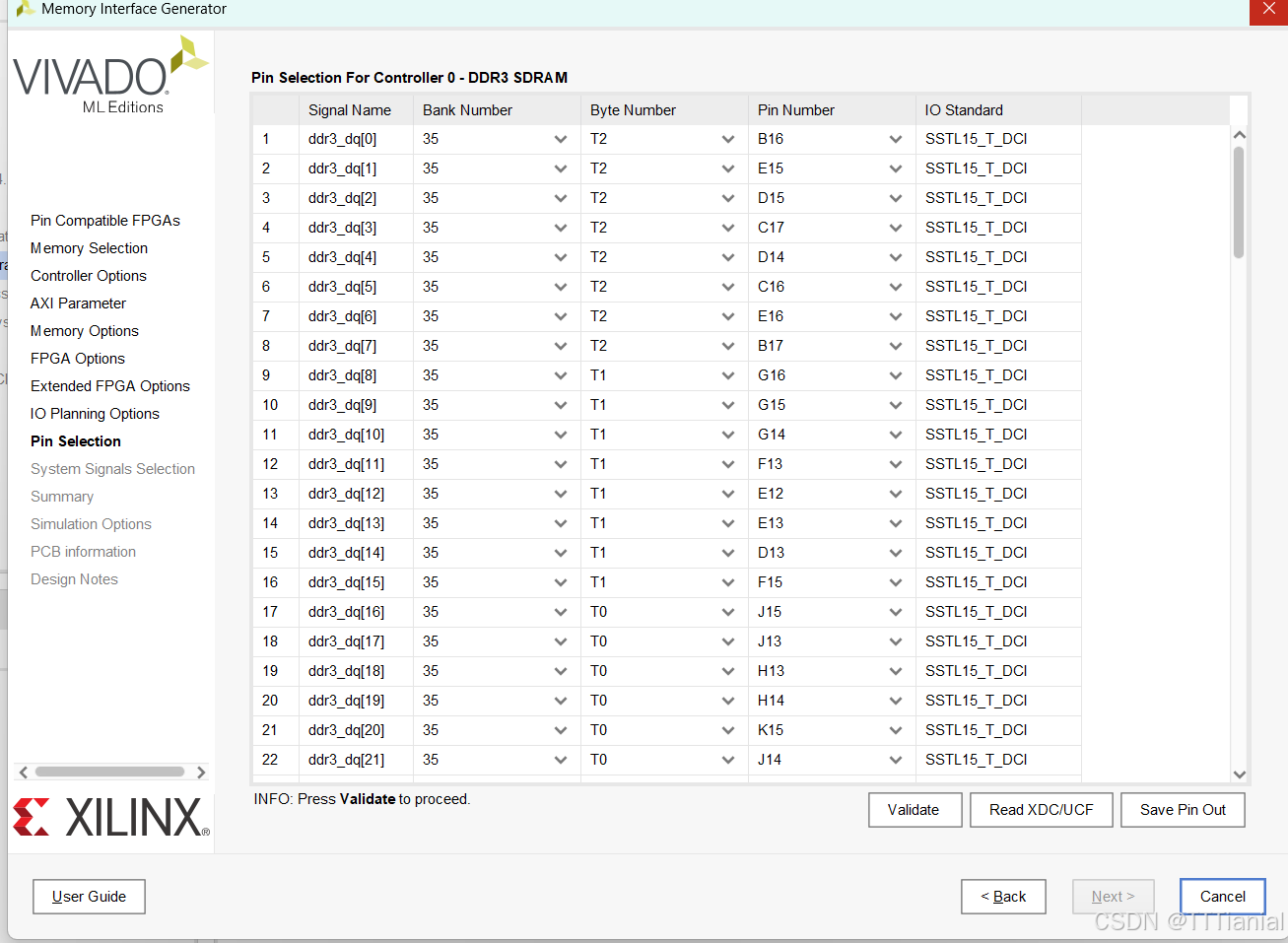

四、DDR的配置。

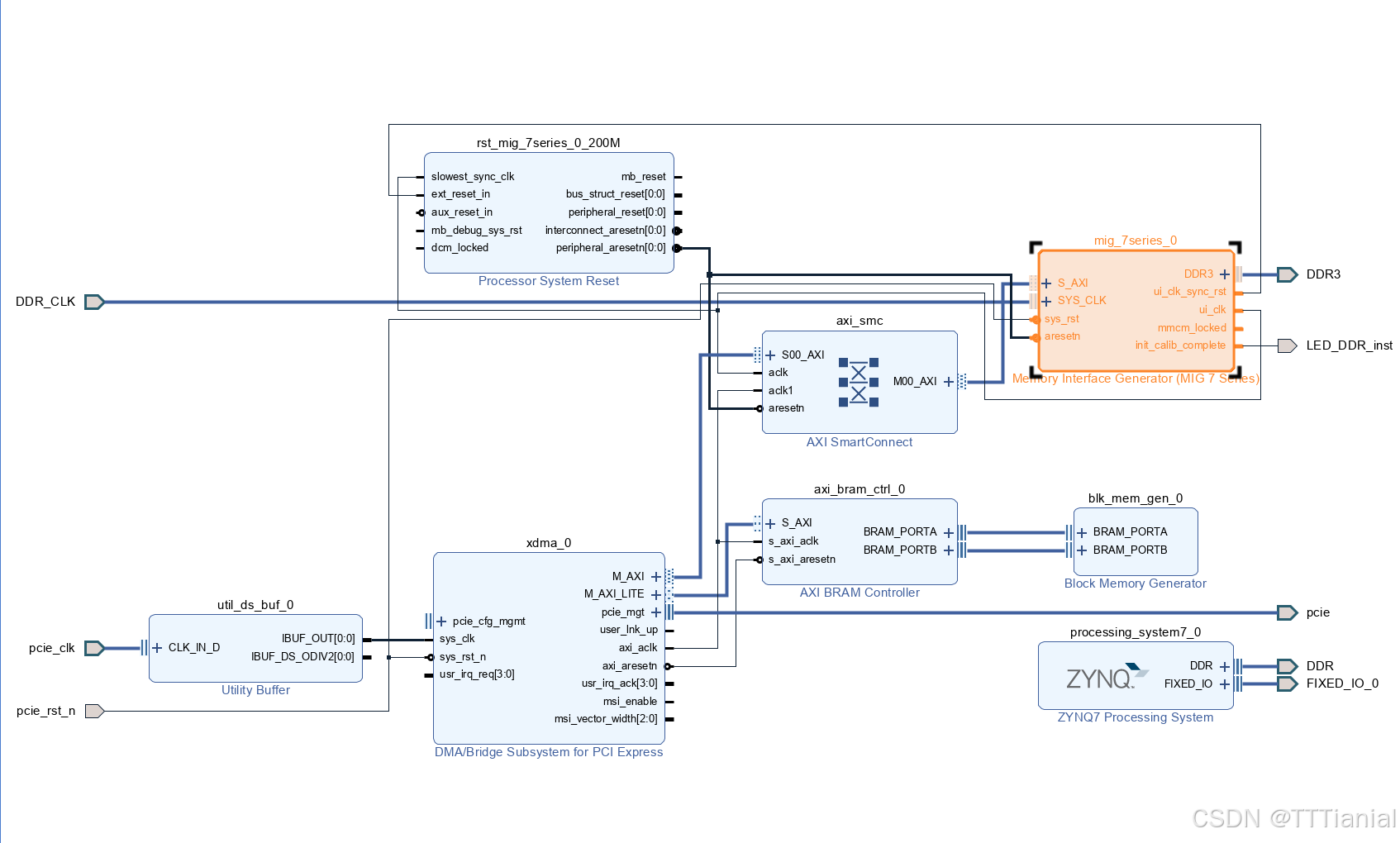

五、bd图

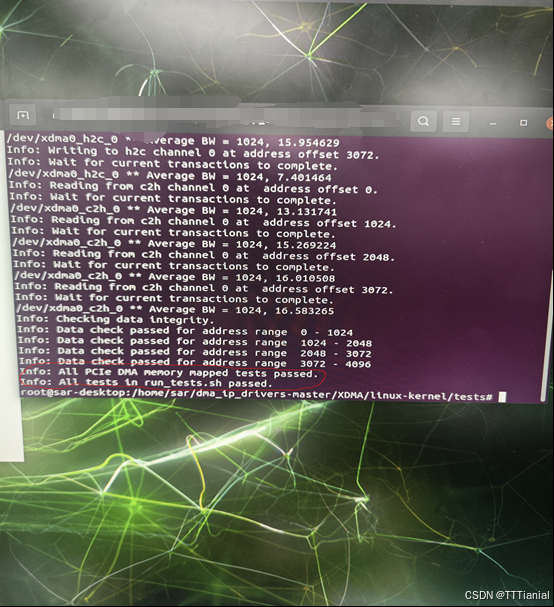

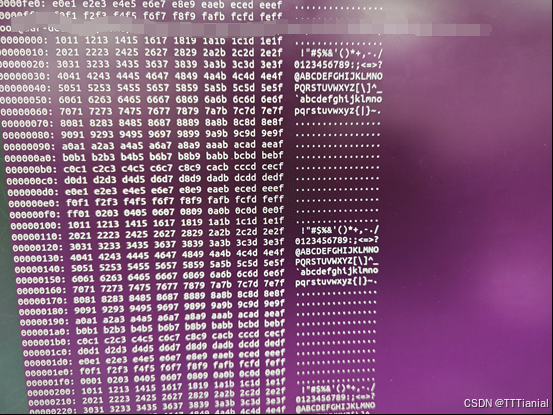

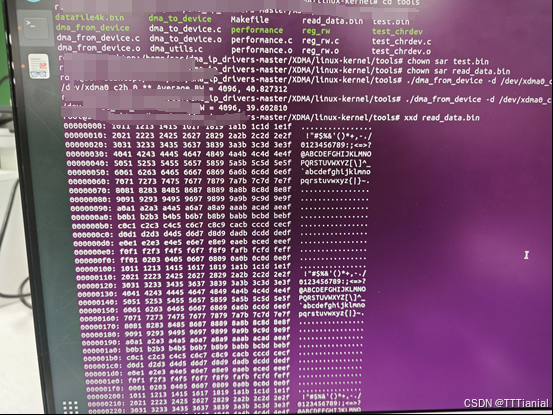

这里我取巧了,我只在Linux上运行的test文件。

六、最终结果

1万+

1万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?