亚稳态的概念

要理解亚稳态的产生原理先得清楚什么是亚稳态。

亚稳态:由于某些原因导致触发器的状态不稳定从而输出不稳定的现象。

这里要清楚,亚稳态是针对触发器的一个概念,指触发器不在稳态(0或1)的一个状态。

亚稳态的产生原理

这里默认读者已经学过数电,了解触发器的工作原理。

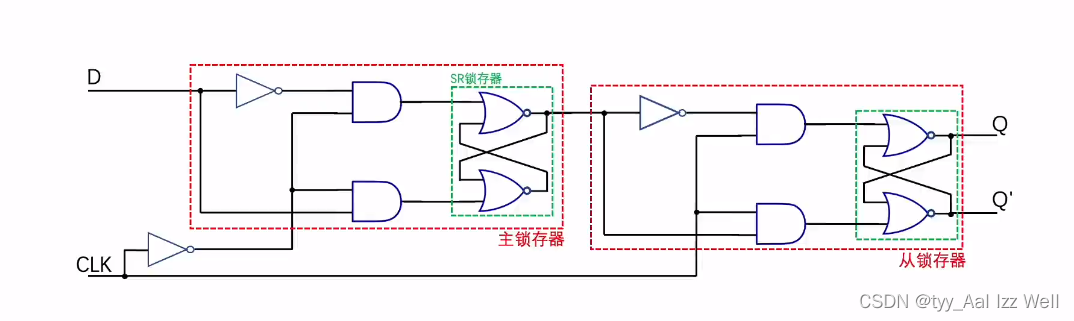

我们以一个经典的主从触发器为例:

如图是一个经典的主从触发器,稍作分析我们可以知道,CLK为低电平时主锁存器中的两个与门开启,将输入信号D读入;CLK为高电平时,从锁存器的两个与门开启,从而将主锁存器中的D传到输出Q。

那么亚稳态如何产生的呢?我们还需要知道两个概念,触发器的建立时间和保持时间。

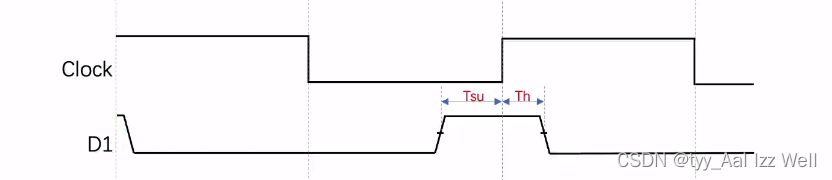

我们考虑一下实际电路中的传输延时,我们可以看到主锁存器中D到达与非门之前需要经过一个反相器,其必然会有一定的延时,然后接着传到SR锁存器后还需要或非门的输出到输入反馈一下主锁存器的状态才能彻底稳定,这段时间称为触发器的建立时间即下图中的Tsu。

还是在主锁存器中,考虑在CLK由0变为1之后需要经过导线和一个反相器到达与门从而将主锁存器“关掉”,这个过程会有一个延时,这个延时称为保持时间即下图中的Th。

(注意:这里对建立和保持时间的定义并不严谨(如没考虑导线延时),只是为了便于解释,意思是对的,想要知道精确的定义还需查看相关的资料)

接下来我们可以想象一下,如果在这两个时间段内,输入D1发生了变化会产生怎么样的结果。

如果在Tsu内发生了变化,那么就会导致变化后的输入信号在时钟沿到来时,其还没有稳定的存在主锁存器中,主锁存器就关闭了(时钟将与门关闭,导致与门输入给SR锁存器的信号可能变化),那么这个时候,SR锁存器的反馈可能会在短时间内难以建立,我们将无法判断主锁存器的状态,即进入亚稳态。

如果在Th内输入信号发生了变化,相当于是时钟的上升沿还没有传入主锁存器(即还没有关闭)

忽然改变了输入,这个输入会传入主锁存器改变SR锁存器的状态,而在SR锁存器反馈稳定之前,下降沿传到与门将主锁存器关闭,同上,此时SR锁存器的反馈可能会在一段时间内较难建立,从而产生亚稳态。

总结

触发器的亚稳态产生的根本原因是信号在电路传输过程中存在延时。

当在触发器的建立和保持时间内输入信号发生变化就有可能产生亚稳态。

1523

1523

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?