前言

目录

前言

芯片设计流程中的仿真验证,就是检验编码设计的正确性,仿真验证工具Mentor公司的Modelsim,Synopsys的VCS,还有Cadence的NC-Verilog均可以对RTL级的代码进行设计验证。(使用Cadence或Modelsim或Synopsys的VCS等软件),本文主要针对使用modelsim验证时,提供高工作效率的方法总结,本人还是菜鸟,如有错误还望指出。

当年,前同事教我仿真的时候,只教了用GUI图形界面,(猜测,他来的时候也是就学了这个,一脉相承啊)即传统的在modelsim软件内新建工程,写测试文件,加设计,导入元件库,用鼠标点来点去。每次更新迭代了测试文件或电路设计,整个仿真流程又要重新来一遍,重复的步骤,空耗时光。很长一段时间内,我都是使用这种方法。直到有一次去外地出差学习,接触到另一位前辈,当时在旁边看他跑仿真,就敲了几行代码,回车一下,编译仿真加波型信号,仿真结果就出来了。对于初出茅庐的小菜鸟来说,虽然还看不懂,但内心大感震撼。大佬就是大佬,同样是仿真,人家可以搞这么简单这么快。

在我的虚心求教下,虽然没有每一行命令都讲解,但是知道了自动化的基础流程。还不会自己写,但参照着他的脚本文件改改,脚本可以跑起来。(也不是说什么留一手的,大佬确实忙,是好几个项目的负责人,能抽空给我讲解一下用法,已经是很难得了)回来后,自己专研总结了这里面的道道。自动化仿真,有点东西,但不多,只要掌握了方法就不难。万变不离其宗,两种方法仿真流程可能不一样,但都可以得到同一个结果,都是通过观察波形,来判断信号逻辑是否正常,设计的电路功能是否实现。之所以推荐使用自动化仿真,是因为它可以完成很多内容重复的工作,帮助我们从重复仿真过程中解脱出来,从而只需要关心与芯片功能相关的仿真结果,提高工作效率。

当然自动化仿真也不是万能的,在执行之前,该准备的文件和和使用图形界面一样要提前写好。仿真过程需要准备tb_test.v;设计的电路生成的.v,对应的底层元件库文件.v,各种功能ip的.v

一、Modelsim是什么?

ModelSim是Model Technology(Mentor Graphics的子公司)的HDL硬件描述语言的仿真软件,该软件可以用来实现对设计的VHDL、Verilog HDL 或是两种语言混合的程序进行仿真,同时也支持IEEE常见的各种硬件描述语言标准。

简单的介绍一下modelsim的仿真过程

完成一次最基础的仿真需要以下步骤:

1建库,2映射,3编译,4启动仿真,5添加信号到波形窗口,6设置仿真时间,7最后进行工程调试,通过观察波形窗口,实际波形逻辑是否和预期一致,来判断设计的电路,功能是否正常。若出现波形异常,就要返回修改电路设计->再仿真检查逻辑->再修改->再仿真…… 迭代这一过程,直至功能完全正常。这个过程是很耗费时间和精力的,大部分的内容是重复,将导致工作效率低下。

对于初学者来说,使用软件的GUI图形界面,来完成设计验证工作。没问题,完全没问题,慢就慢一点,多操作,可以快速的熟悉软件操作和验证流程,积攒工作经验。我是说老鸟,哦,不,是有一定经验的你。可以选择使用tcl脚本,进行自动化测试,解放双手,在摸鱼的同时,高效的完成工作。

二、TCL脚本语言简介

• TCL( Tool Command Language) 是一种解释执行的脚本语言( Scripting Language) ,它提供了通用的编程能力:支持变量、过程和控制结构;同时TCL还拥有一个功能强大的固有的核心命令集。TCL经常被用于快速原型开发,脚本编程,GUI和测试等方面。

什么是DO文件

DO文件是一次执行多条命令的脚本。这个脚本可以像带有相关参数的一系列ModelSim命令一样简单,或者是带有变量,执行条件等等的Tcl程序。可在GUI里或系统命令提示符后执行Do文件。

如何创建DO文件

方式很多,简单的使用记事本就可以,保存时,将文件的扩展名改为.do即可,例:创建一个名为top.do 的脚本文件。

• modelsim 软件能识别脚本内的各命令并顺序执行,从而达到自动执行仿真的功能,用户可以使用TCL脚本来控制仿真环境、运行仿真、管理项目、处理结果等。例如,实际使用中,通过编写TCL脚本来自动化测试程序的执行,收集和分析仿真结果,甚至修改仿真参数并重新运行仿真,从而实现自动化的验证流程。

如上所述一次简单仿真需要的6个流程,在tcl脚本中编写相关命令,这样每次仿真只需要执行脚本,就可以自动完成设计的验证工作。

三、实际操作

上来就写脚本吗,

不不不,

先介绍怎么用,

还不会爬,

你让我先跑,

是的。

我们是站在巨人的肩膀上,自己不会写,ctrl+c ctrl+v 会吧。学习啊,就是要脸皮厚一点,多向同事请教,多参考别人的文件,先用起来,在使用的过程中搞懂其中的原理。

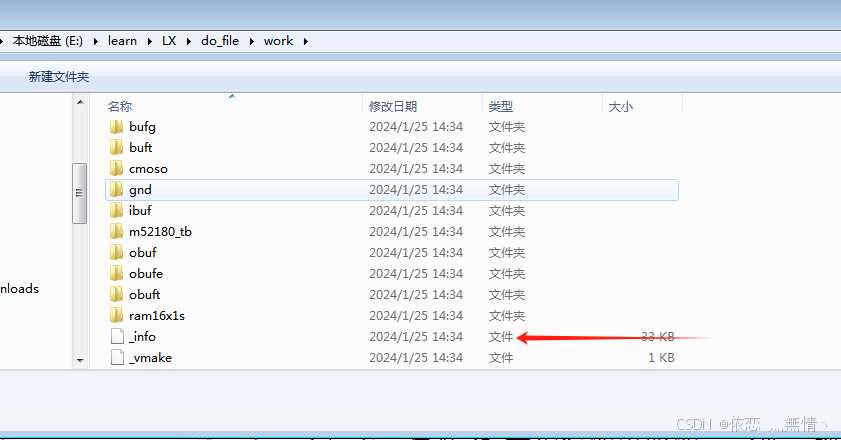

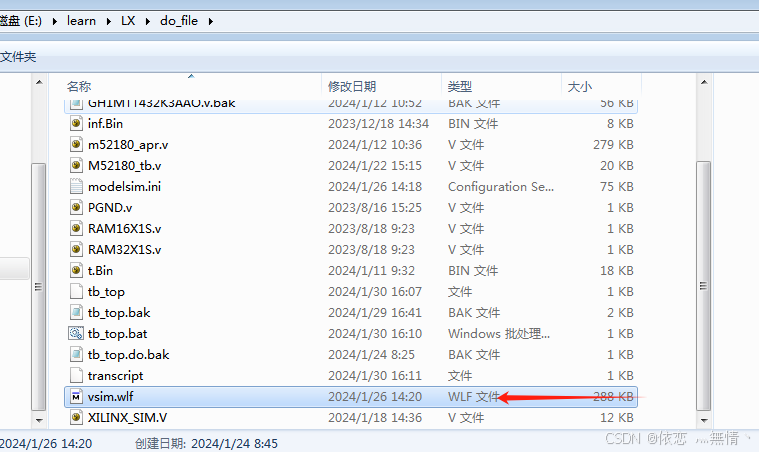

加载工程文件目录:

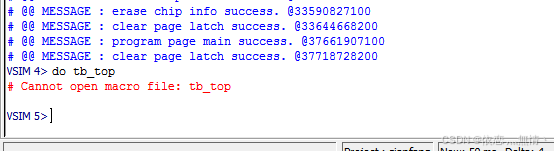

使用do批量处理命令仿真的第一步,,首先要做的是加载更改工程文件目录,不做这一步,你敲do命令执行脚本命令,也是找不到你的批处理文件的,如图1

设置工作目录的路径有两种方法:

1、在软件上方的选项栏中,找到 file => change directory => 选择.do文件所在文件夹

2、在Transcript窗口,VSIM4> 光标后 ,敲cd命令,空一格,盘符,c盘或d盘,加冒号加斜杠,命令行上方有对应文件提示

VSIM4> cd E:/learn/LX/do_file

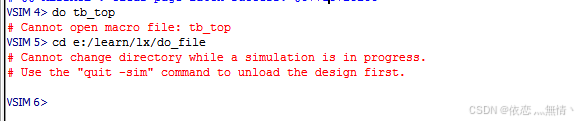

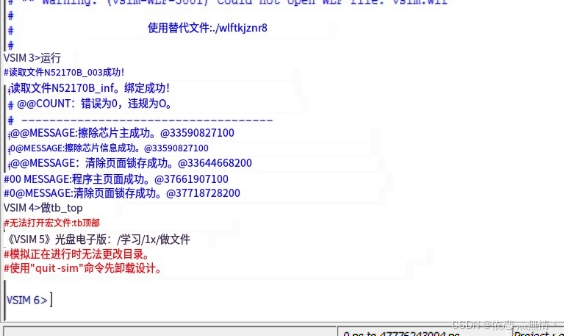

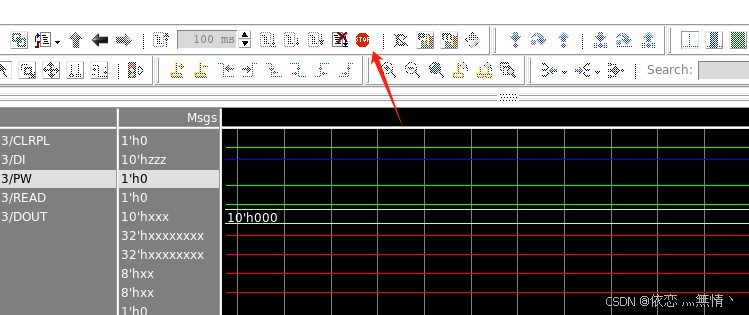

注意:在更改文件路径时,需要退出仿真状态。如下图操作会报错

因还未退出仿真,故加载文件目录报错

执行do命令:

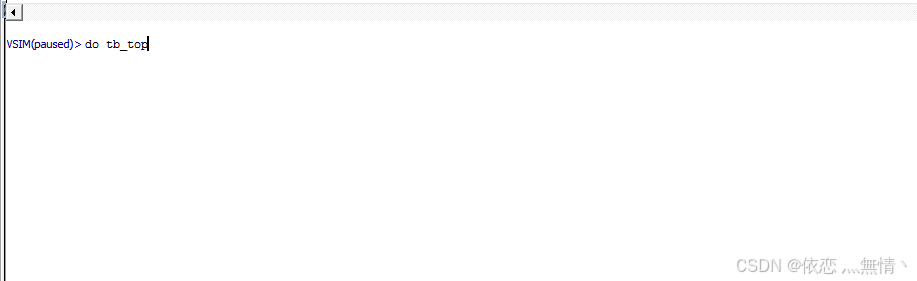

在将路径更改到do文件所在目录后,还是在Transcript窗口(若这个窗口意外关掉了,可以在view栏内,选中Transcrip若选中有打勾标识,即可恢复),VSIM4> 光标后 ,敲do命令

加脚本文件名 do tb_top.do,回车后modelsim se软件会按顺序执行批处理文件内的脚本命令。相当于DOS中的.bat文件,注意 #井号后面的是注释内容,do命令不会执行。

啥,实际敲完后的结果,你敲完就知道了。

水完了,下面上干货。

四、Do文件详解:

完成一次仿真过程,需要的基础命令:

1.首先是

vlib work命令,此命令会在tb_top文件同一个目录下,建立一个work目录,注意不要用操作系统自己建一个work文件夹,因为用操作系统建立的work文件,并没有modelsim SE 自动生成的_info文件, “_info”是运行的一些信息,和work文件是配套的,一般情况下不会用到这个文件,当然没事也不要去改它。

2.映射(将目前的逻辑工作库和时间工作库映射对应)

vmap work work

(此文件夹必须用vlib命令事先定义好,才能被引用)

后一个work表示,在modelsim的library窗口,创建一个名为work的库文件夹(逻辑目录),其对应的物理目录,是vlib命令创建好的名为work的文件夹

创建work文件夹的目的,是为了后续编译的文件都可以存放在这个文件夹下,modelsim的work library里可以看到编译文件名称,而这些编译文件实际是存放在vlib创建的work文件

3. vlog编译命令

vlog*.vvlog是编译命令,

*星号是通配符,例:{./*.v},表示编译do文件所在目录下的所有.v文件,并将其添加进工作库(work)中,包括IP或你设计的电路的.v文件,test_tb.v,库文件等都需要编译。当然不在同一个目录也可以单独进行编译,需要添加文件所在路。

编译单个文件:

#vlog -reportprogress 300 -work work {./test_1.v}

./一个点加斜杠号,

表示与do文件同层的文件夹内,编译test_1.v。

#vlog -reportprogress 300 -work work {../../demo/rev_1/n52170.v}

../两点加斜杠,

表示在do文件夹的上一层,上几层就重复../几次,以上表示do文件所在目录上两层的文件,选择demo文件对其编译

4.vsim

vsim -novopt work.m52180_tb vsim 启动modulsim仿真命令

“work.”固定用法,后面接上测试模块的模块名m52180_tb

vsim -voptargs=+acc work.tb_top

-voptargs=+acc 是固定命令脚本,表示优化部分参数

设计优化功能是用来提高仿真速度的,对于小工程,选择不优化或者选择优化其实对仿真速度的影响微乎其微,根本感觉不到:有三种优化方式

不优化(命令 -novopt):完全不进行设计优化,所有信号可见,但仿真速度较慢。

优化(命令-vopt):进行设计优化,但信号不可见,速度最快。调试完全依赖于testench的打印输出,无法正常看到中间信号。在不是非常高度自动化的进行测试,并且需要观察中间调试信号的情况下,一般不推荐该模式

vsim -novopt work.m52180_tb

部分优化(命令 -voptargs=+acc):进行部分设计优化,但又保证所有信号可见,速度较快,调试常用

vsim -l M52180_rtl.log –Lf D:/EE095LPT5_LIB -novopt +maxdelays work.m52180_tb

此处-Lf D:/EE095LPT5_LIB 这是电路设计所用到的编译过的底层元件库,在仿真之前,新建一个文件夹,将编译后的底层元件库放在这里,启动仿真时,调用这个库文件来仿真

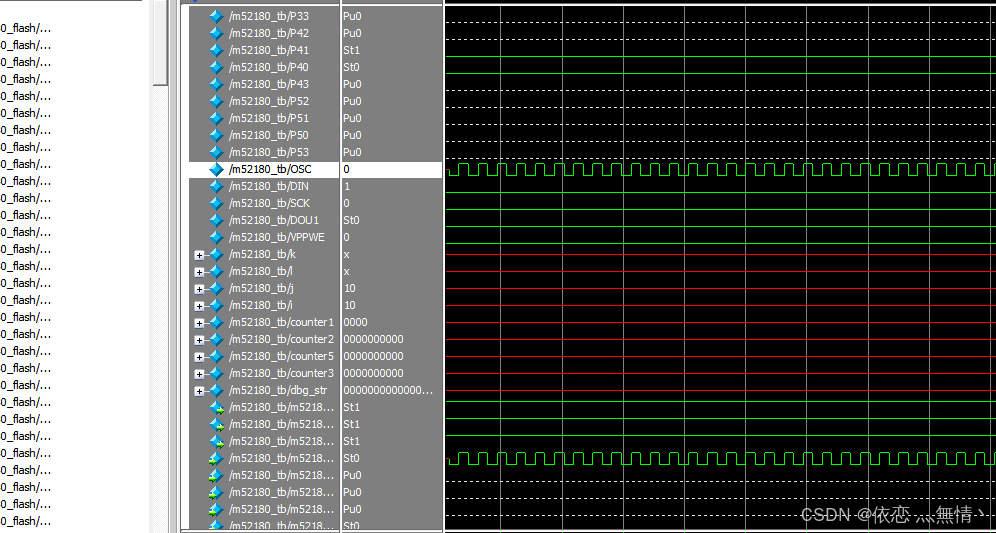

5. add wave

add wave –r /*, /*此命令表示添加所有信号到波形窗口,注意:斜杠前还有一个空格

add wave /m52180_tb/m52180_u/* 需要观察哪个模块的信号,就添加哪个模块的实例名,/*

add wave /m52180_tb/m52180_u/APR52170/*

(这里要注意,和编译命令不同,只需要一个单斜杠再加模块实例化名就可以)

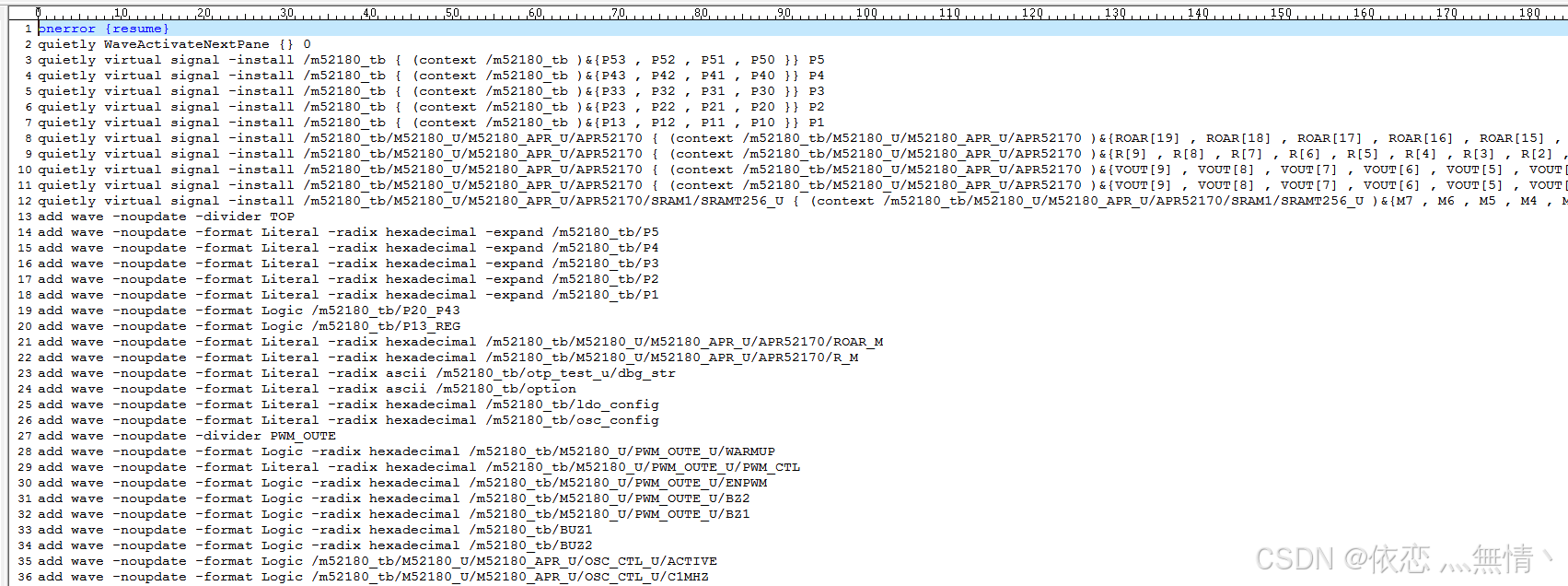

也可以单独写一个TOP1_WAV.do 文件,把需要观察的信号都加在文件内如下图,然后在tb_top 文件内加上一行 do TOP1_WAV.do ,此命令会将信号放在新的窗口打开。

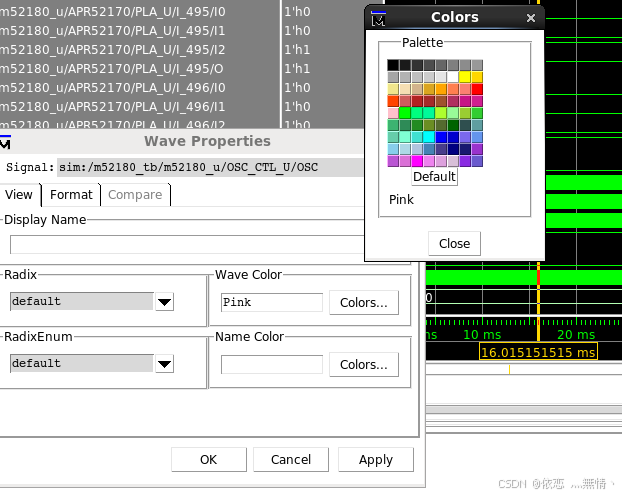

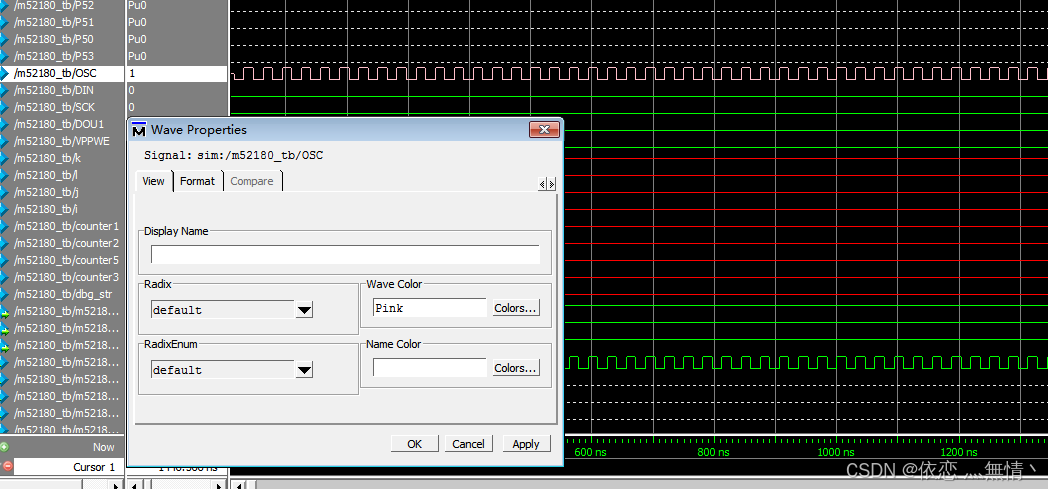

若想要把某条波形信号,醒目的观察,可以更改此信号的颜色,方法是:将鼠标移至信号窗口栏,选中那条信号,右键,选择properties,弹出波形属性窗口,更改波形颜色。

(更改某信号的波形显示颜色)

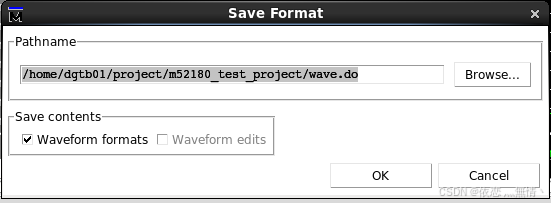

废了半天,把想要的波形的颜色都搞粉了,但若没保存,下次进入仿真,这些波形还是会恢复成原来的颜色。这时可以按Crtl + S 保存当前状态为wave.do,路径为默认路径。

下次想打开保存的波形,在你的工程文件目录下,有一个vsim.wif文件,打开它,会自动打开modelsim软件,但并没有再跑仿真,直接可以看波形。

接下来重复操作一遍,你懂的。我懂,在Transcript输入:do tb_top,按Enter回车键。上次的波形就回来了! ?????什么情况,我花花绿绿的波形呢,怎么又还原了,怎么回事?

(osc信号设置成粉色)

我知道你急,但是你先别急。执行do tb_top,执行的是最开始的仿真,他的波形设置是按默认的,想要找回上次保持的波形,只需要敲入do wave.do,你上次保存的波形do文件,回车一下就回来了。

正确打开波形窗口osc信号颜色改变

6.run命令

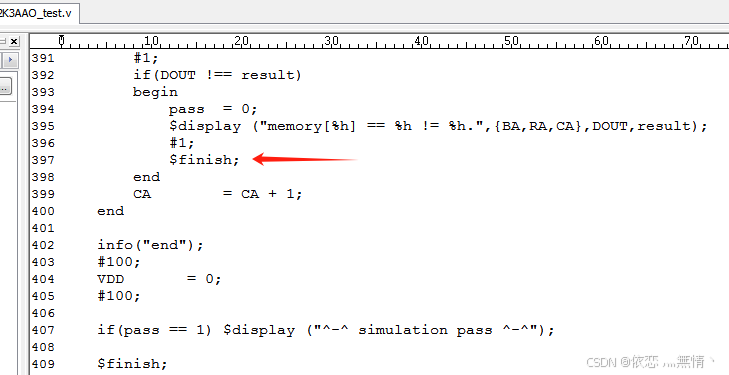

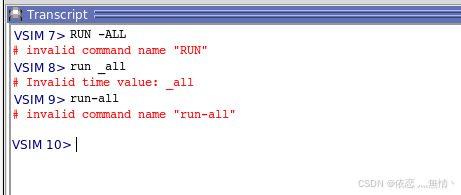

run 50ms表示仿真运行时间,格式: run +时间,时间单位ms 、us、ps,不可用秒,run用小写

run –all modelsim命令,功能直接运行仿真,没有时间限制,直到遇上,test_tb测试文件中的$stop或$finish命令才终止 ,如果没有停止命令仿真就会一直跑,可通过头部菜单栏中的stop选项,停止仿真。

run –continue 命令功能,让仿真继续运行

遇到验证功能,需要电路跑几秒或几分钟的情况,run –all命令好用的很,让仿真一直跑

注意:以下三种情况,不能用大写字母命令,都是小写,使用下划线是错误的,run命令后要空一格,

7.clear命令

.main clear清除命令行内容命令,注意main前面有一个 “.” 不常用到,要清命令行,在Transcrip窗口空白处,右键,点击clear更方便,

通过键盘上的方向键,可以在脚本控制台上下切换之前使用过的命令。不过因为使用过clear,故之前执行指令,所显示的报告,警告以及错误信息等都清除了,只保留命令记录。通过这个技巧可以快速的执行仿真命令,方向键,选择以往的命令+回车搞定。方便得很。

8.view

view

指令格式:view窗口名

指令功能:打开Modelsin的窗口

view souce,打开源代码窗口:

view wave,打开波形窗口;

view list,打开列表窗口;

view varibles,打开变里窗口;

view signals,打开信号窗口;

view all,打开所有窗口。

若想要单独观察某组数据,可使用此命令将需要的信号,放在自己命名的波形窗口中

9.quit 命令

quit -simquit -sim是退出仿真工程

quit –f -f参数是关闭软件命令

总结:

以上就是今天要讲的内容,本文仅仅简单介绍了modelsim自动化仿真的使用,而tcl脚本命令提供了大量能使我们快速便捷地完成仿真的方法。

2726

2726

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?