模拟ic入门——设计一个两级运放(一)两级运算放大器设计基础-CSDN博客

模拟ic入门——设计一个两级运放(二)两级运算放大器结构确定与参数计算-CSDN博客

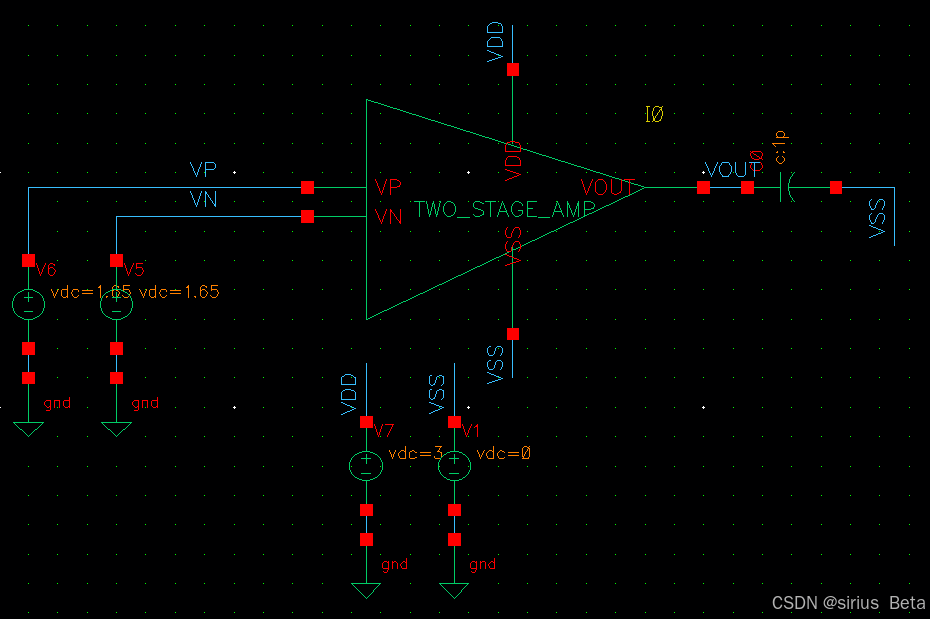

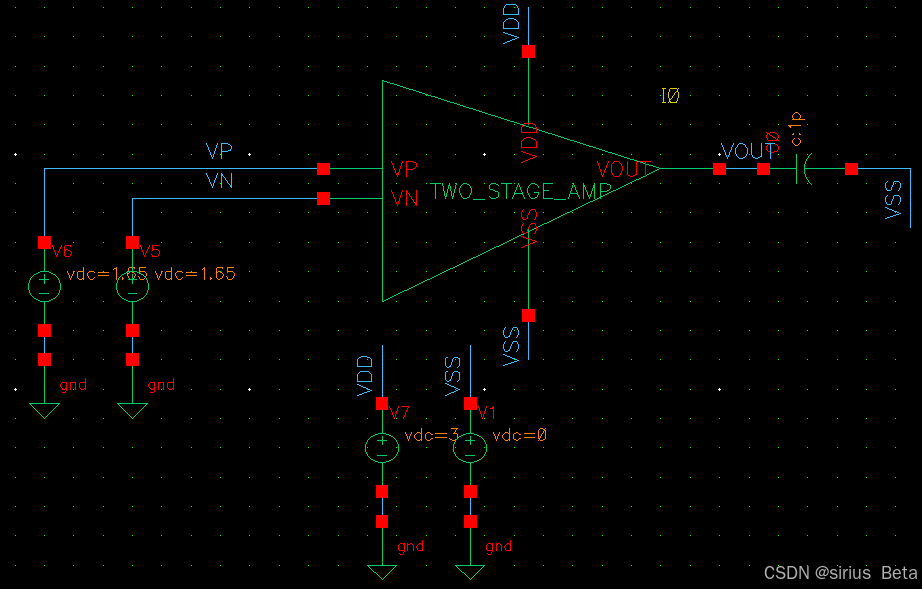

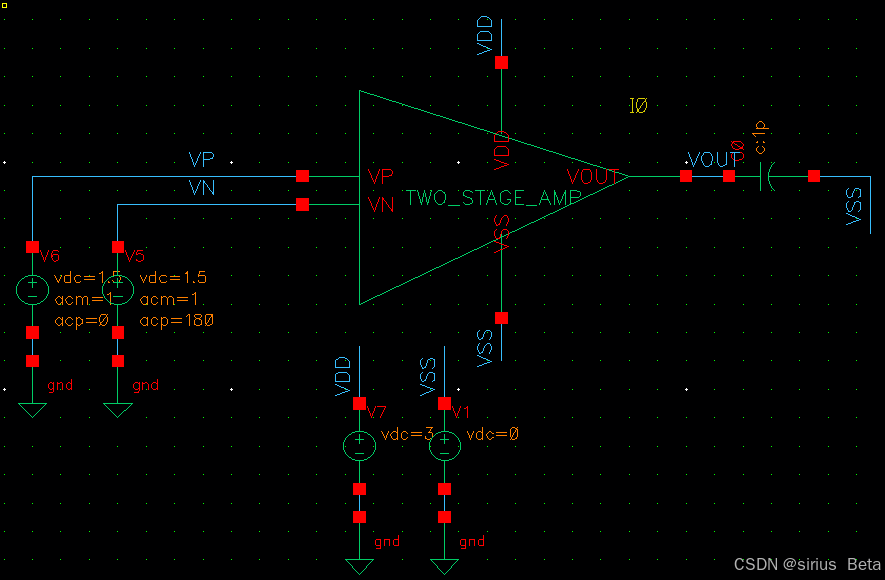

本节我们来通过virtuoso仿真上节计算的电路参数,分为三个部分DC仿真的,AC仿真以及trans分析

一、DC仿真

(1)静态工作点

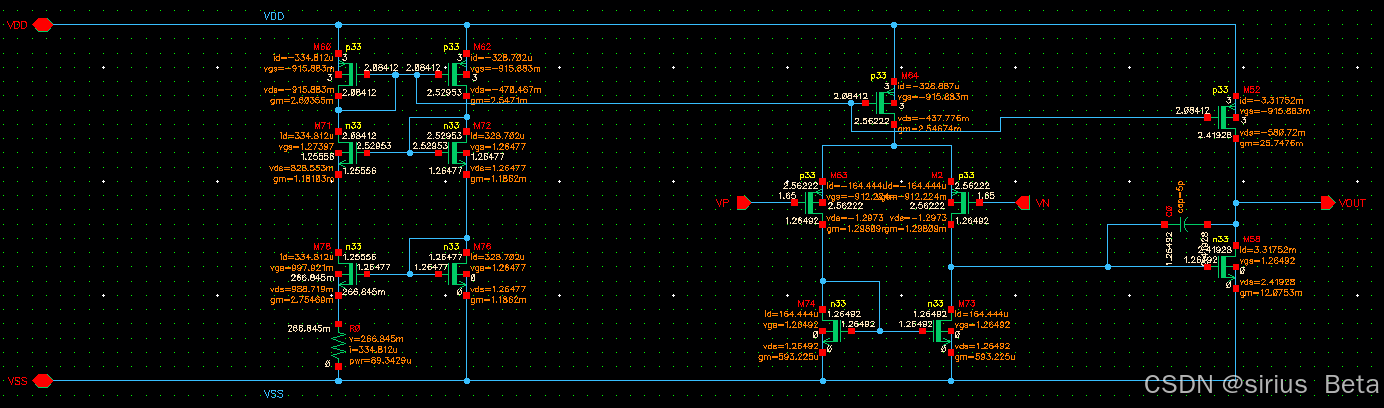

在电路各个部分全部设计完成后,首先进行

dc

仿真,查看电路静态工作点是否正确,MOS

管是否饱和,如图所示

从图中可以看出,电路中每个

MOS

管都工作在饱和区,其中流经M6的电流为328.887uA,

M1

与

M2

的跨导

gm

为

1.29mS

,高于设计值。这是由于设计基准电流源时采用的gm/ID与过驱动电压之间的近似计算,以及未考虑MOS

管的二级效应产生的

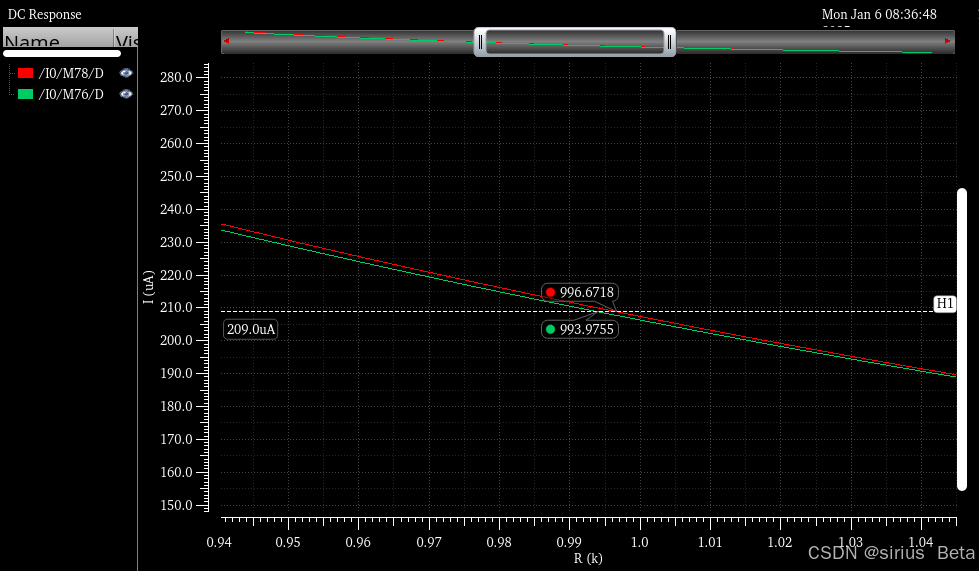

如果我们需要将M6的电流固定为209uA,怎么办呢?

我们可以通过修改电阻R1的大小,可以使基准电流源产生的电流更加准确。在本设计中,在选择合适的电阻R1大小我们仍然选择通过仿真器来进行操作

具体操作为:

首先设置电阻

R1

的大小为一个变量“R” ;然后再

ADE

仿真工具中选择

dc直流分析, “Sweep Variable“

选择”Design Variable

“ ;然后设计变量选择”R“

后,设置一个合适的扫描范围进行扫描分析,而输出选择流经M12与

M13

的漏源电流,全部设置完成后,进行仿真。如图所

示,就可以在曲线图中找到最合适的电阻大小,从而产生所需的电流值。

这里有一个技巧:输出可能是电流和电压值,电压选线,电流选点!详见这个博主写的

关于Cadence Virtuoso ADE L仿真时纵坐标为电流而不是电压的问题_virtuoso trans仿真看电流-CSDN博客

当电流大小为209μA时,两条支路的电流并不相同,为了减小误差,取两种情况下电阻的中间值,设电阻R1为994.5Ω

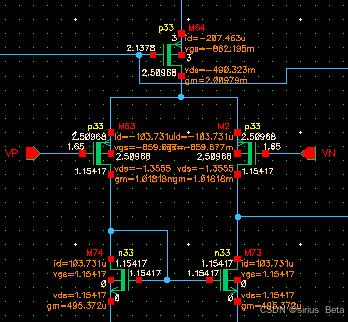

,对电路再次进行直流仿真

从仿真图

可以看出,M6的漏电流大小为

207.4μA

,已经非常接近理论计算值

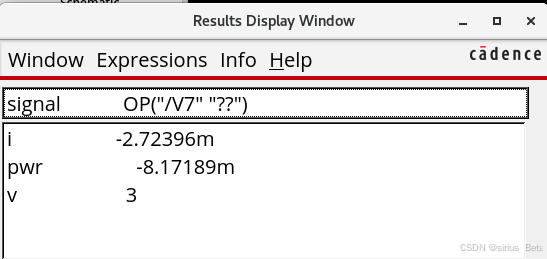

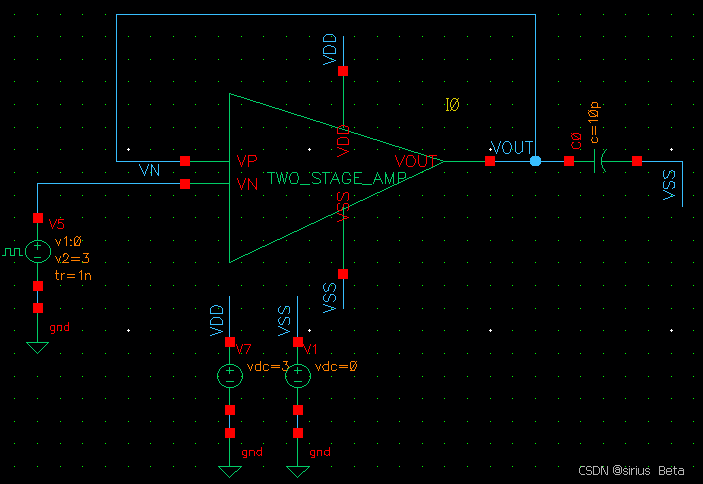

(2)静态功耗仿真

修改电阻

R1

后,再次对电路进行仿真查看电路的静态功耗,其中仿真电路图如图

所示

仿真成功运行后,点击ADE仿真环境菜单栏“Results”

中

“Print”

中的

“DC Operating Points” ,再点击运放电路的电压源信号

以得出电路工作的静态电流大小为2.72396mA,所以电路的静态功耗3V*2.72396mA=8.17189mW,符合设计指标的要求

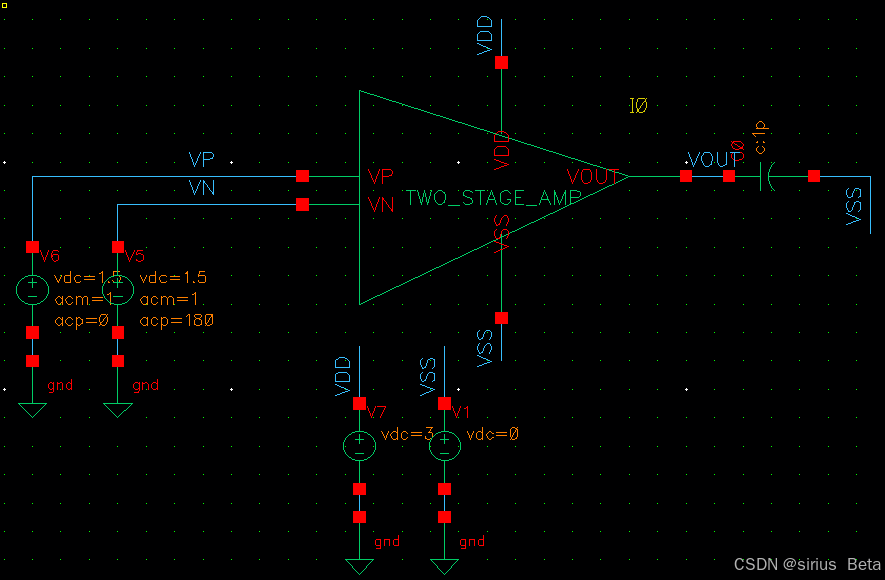

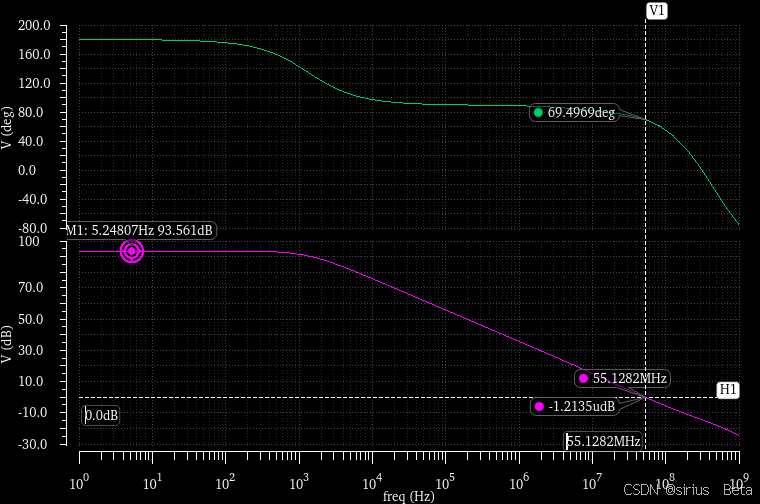

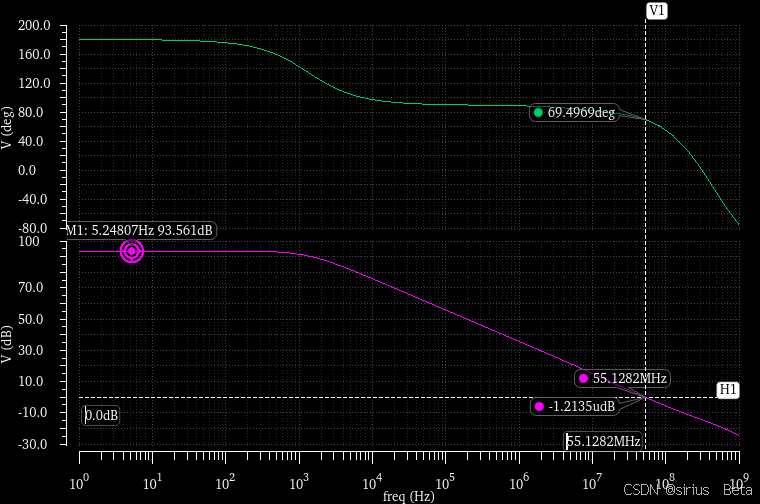

二、AC仿真

(1)增益与相位裕度仿真

交流小信号分析,可以得到电路的增益以及相位关系。运放的输入端接共模电压1.5V、交

流电压幅值为

1V

,相位相反的电压源

增益达到了93.56

dB

,单位增益带宽GBW

为

55MHz

,而相位裕度为69.4

° ,均达到了设计要求

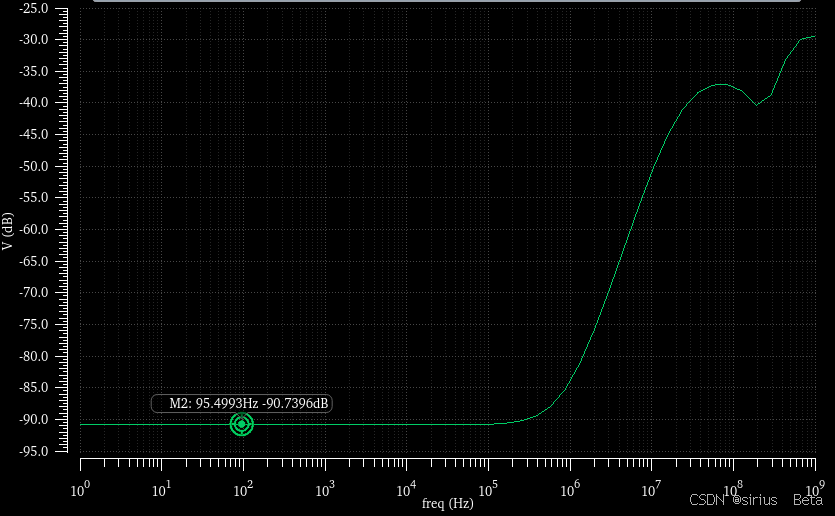

(2)共模抑制比CMRR仿真

对运放的共模抑制比进行仿真,可以将运放连接成单位增益负反馈形式。首先对反相输入端接一

个交流电压幅值为

1V

的电压源并连接至输出端,正相输入端则接一个共模电压为1.5V

、交流电压

幅值为1V

的电压源,仿真所用的电路图如图

所示

对电路进行

ac仿真,可以看出,运放的共模抑制比为90.7396dB

,达到了指标要求

如果还想要增大CMRR,怎么办?

观察差分输入级中的电流源,若想提高共模抑制比则需减小电流失配,其中过驱动电压VOD

与

gm/ID值已经确定,因此应尽量不考虑修改电流源晶体管的过驱动电压。除了增大过驱动电压可以增强电流镜的匹配性,还可以增大沟道长度L

,而本设计所采用的电流源MOS

管的L为

600nm

,为了减小失配,选择将所有的电流源MOS

管的

L

增大两倍,同样其W

也要增大两倍

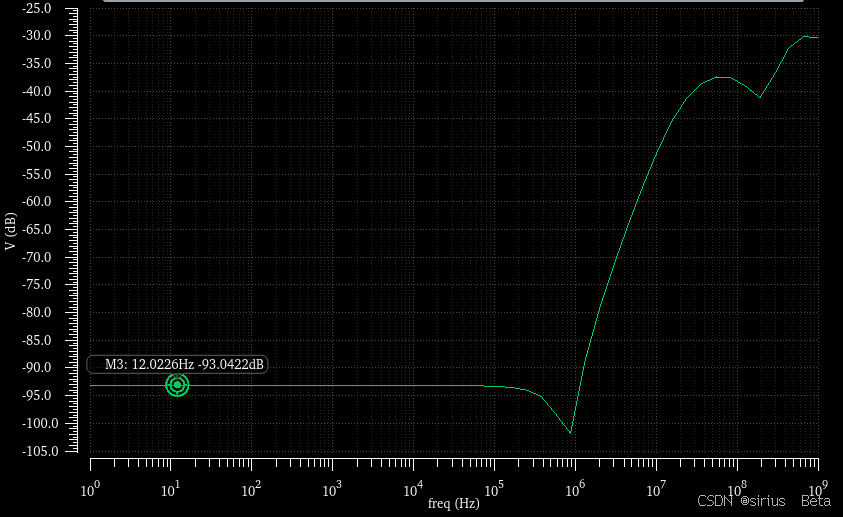

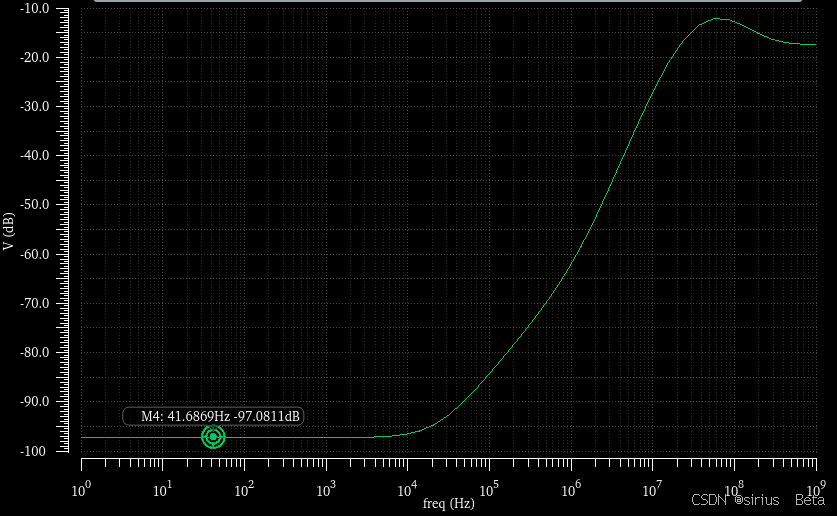

(3)电源抑制比

PSRR

仿真

对电路的电源信号处叠加一个交流电压为1V

的电压源,将运放的正相输入端直接接输出端,反相输入端接共模电压1.5V

低频时电源抑制比为97.0811dB,满足设计指标

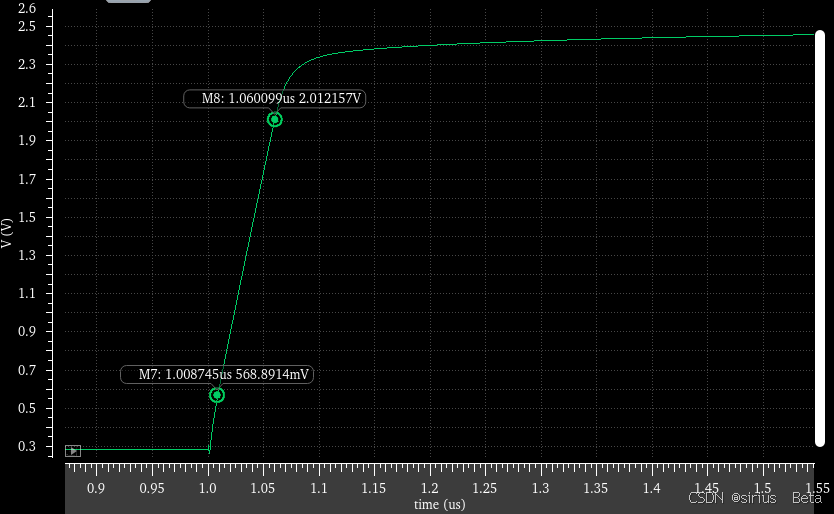

三、trans分析

测SR大小

输出信号在上升阶段的

SR

为

28.1042M

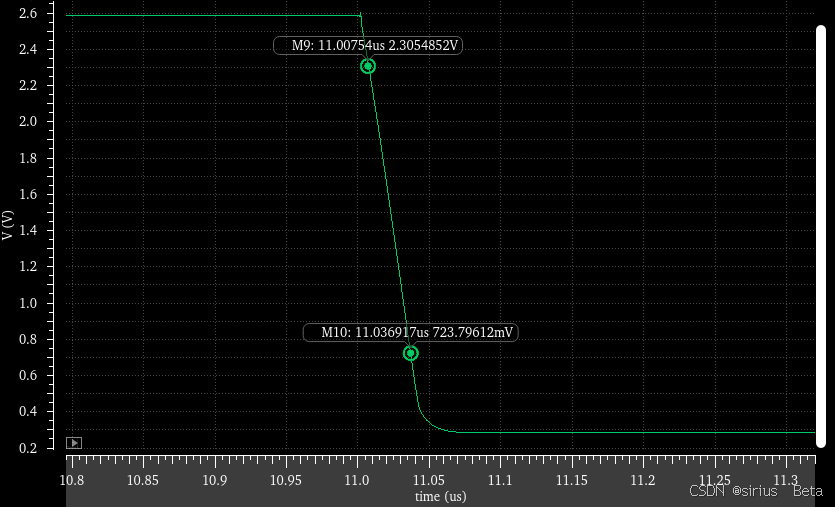

在下降阶段的

SR

为53.8410

M

因此运放的压摆率

SR为28.1042M,满足设计指标的要求

本节我们通过virtuoso仿真上节计算的电路参数,均满足要求。至此,一个简单的Miller补偿二级运放电路就设计完成了,后续会有版图和DRC,LVS等

2058

2058

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?