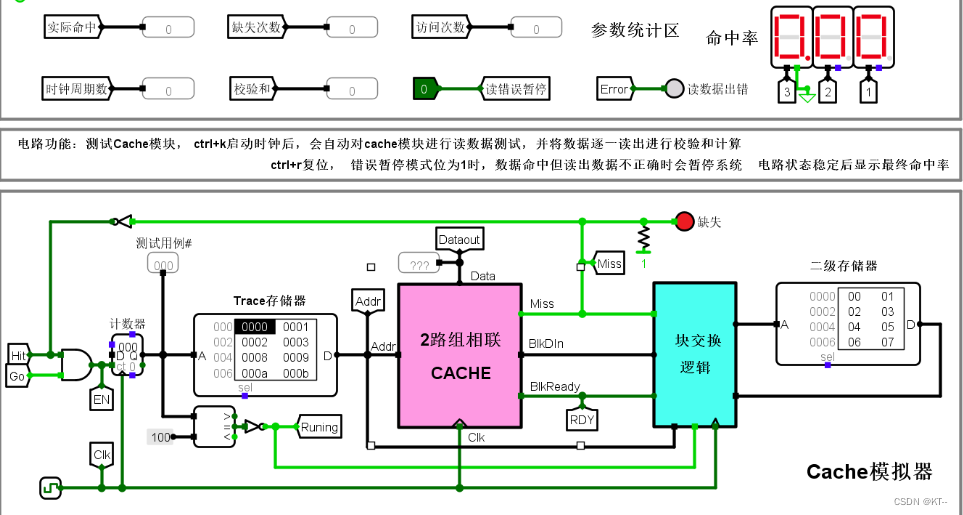

第7关:2路组相联cache设计

✨创作不易,还希望各位大佬支持一下

👍 点赞,你的认可是我创作的动力!

⭐️ 收藏,你的青睐是我努力的方向!

✏️ 评论,你的意见是我进步的财富!

链接:https://pan.baidu.com/s/1dIMlSrRySWRjNY6aLRlI0g

提取码:n7cd

实验目的

学生掌握 cache 实现的三个关键技术:数据查找,地址映射,替换算法,熟悉译码器,多路选择器,寄存器的使用,能根据不同的映射策略在 Logisim 平台中用数字逻辑电路实现 cache 机制。

实验内容

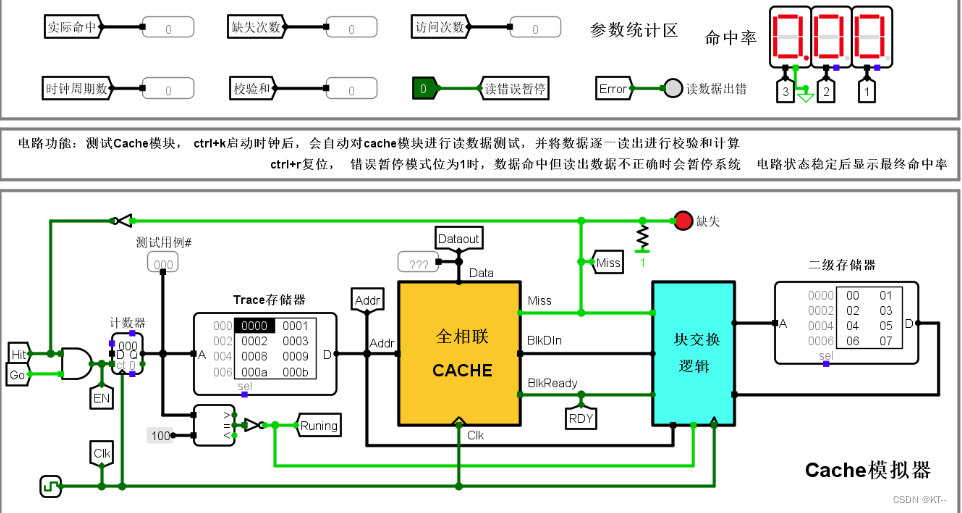

上图给出了一个在 Logisim 中设计完成的 cache 系统自动测试电路,为简化实验设计,这里所有 cache 模块均为只读 cache (类似指令 cache ),无写入机制。电路左侧计数器与存储器部分会在时钟驱动下逐一生成地址访问序列给 cache 模块。计数器模块的使能端受命中信号驱动,缺失时使能端无效,计数器不计数,等待系统将待请求数据所在块从二级存储器中调度到 cache 后才能继续计数。 cache 与二级存储器之间通过块交换逻辑实现数据块交换,由于二级存储器相比 cache 慢很多,所以一次块交换需要多个时钟周期才能完成, cache 模块判断数据块准备好的逻辑是 blkready 信号有效,该信号有效且时钟到来时, cache 将块数据从 BlkDin 端口一次性载入到对应 cache 行缓冲区中,此时 cache 数据命中,直接输出请求数据,解锁计数器使能端,继续访问下一个地址。 自动测试电路会逐一取出 trace 存储器中的主存地址去访问存储系统,并逐一将数据从 cache 模块取出送校验和计算电路计算校验和,当计数器值为256时会停止电路运行,此时所有存储访问的 cache 命中率将会在右上角 LED 数码管显示。本次实验的主要任务就是设计该电路的核心模块 cache 子电路。 结合引脚功能说明,实现只读的四路组相联 cache 模块,该 cache 模块共包括8个 cache 行,每个数据块包含包括4个字节共32位数据。

电路框架

storage.circ

✨创作不易,还希望各位大佬支持一下

👍 点赞,你的认可是我创作的动力!

⭐️ 收藏,你的青睐是我努力的方向!

✏️ 评论,你的意见是我进步的财富!

链接:https://pan.baidu.com/s/1dIMlSrRySWRjNY6aLRlI0g

提取码:n7cd

1776

1776

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?