Clock Tree Synthesis(Cts)

Place完成后此时所有的器件均已放进core内,可是所有的std cell放好就代表可以绕线了吗,当然不是,中间还有关键的一步——时钟树综合。这部分在整个后端实现都是非常重要的,因为时钟树质量和后续时序收敛难度有直接关系,好的时钟树可以很大程度上减少后续时序收敛的工作量。那什么叫cts?cts要做哪些工作呢?其实Cts就是在约束下,把clock信号从root通过buffer/invertor一级一级送到所有的sink点,并且尽量降低latency和skew的过程。

首先补充几个概念:

- Root pin:指时钟产生点,通常由create_clock定义

- Sink pin:包括reg的CK端,memory/IP的CK端

- Leaf net:指sink点和它前一级buf/inv之间的clock net

- Trunk net:指出去leaf net剩余的clock net

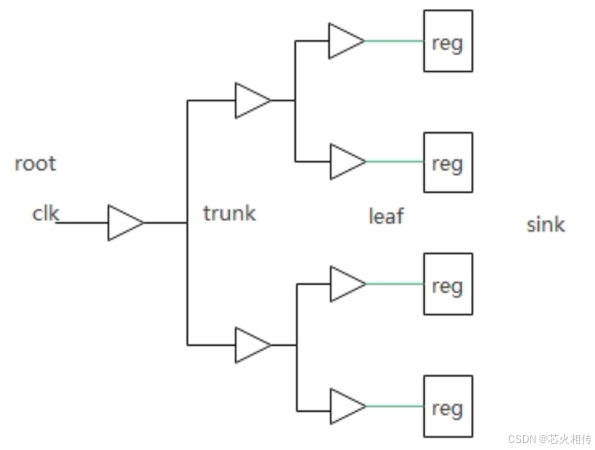

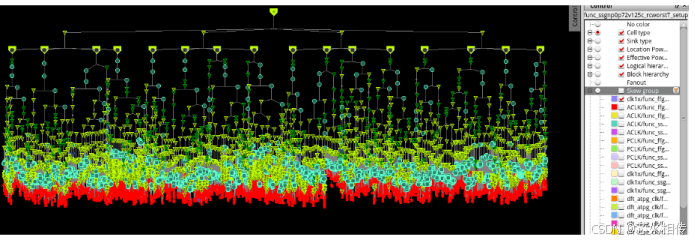

下面这张电路图可以帮我们理清楚上述几个概念:

由上图可以看到,时钟树其实就是由buf/inv一级一级组成的,每一个分结点就划分成一级,这里的buf/inv就是库里专门用来长时钟树的clkbuf/clkinv。

但是时钟树也不是长了就一定可以的,还要分析它的质量是否能达到标准,一般衡量时钟树质量的指标有:

- Latency

- Skew

而做高质量时钟树的目的就是为了时序服务的,这里需要关注的时序包括setup,hold,drv。

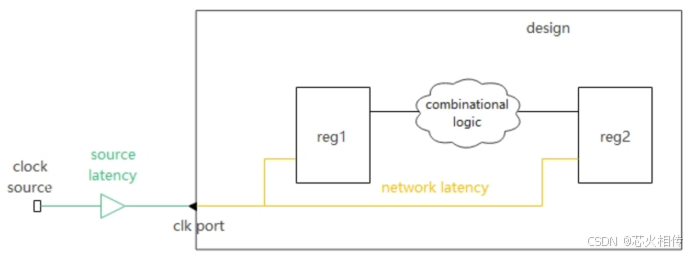

Latency

包括source latency和network latency两部分,source latency是指时钟源头到模块clock port的延时,network latency是指模块的clk port到sink点的延时。

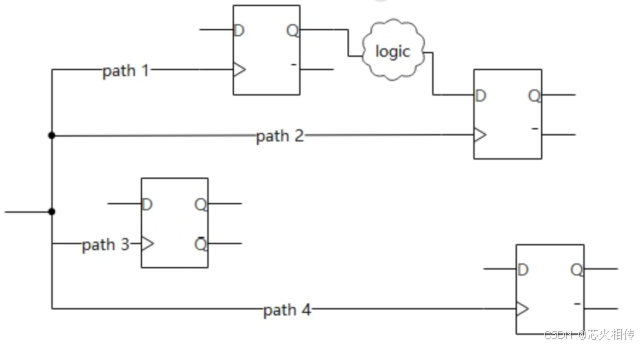

Skew

是指同一时钟到达该时钟域内不同reg的时间偏差,分为global skew和local skew。

Global skew即同一时钟域内,任意两个路径的最大skew(path 3 & path 4)。

Local skew即同一时钟域内,任意两个有逻辑关系的路径最大skew(path 1 & path 2)。

Cts策略内容:

- Clk buf/inv以及fix hold cell选型

- Ndr rule

- Sheilding

- Cts约束(包括useful_skew,insertion_delay,max_fanout length等)

关键cmd--ccopt_design

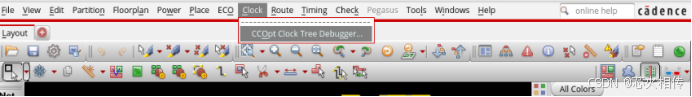

可通过innovus gui查看时钟树结果以及debug

最后,如果好奇不做cts会发生什么也可以测试下,文中也有答案。这部分内容太多,技术细节和注意事项后续文章我们再慢慢展开。

2529

2529

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?