知识回顾:

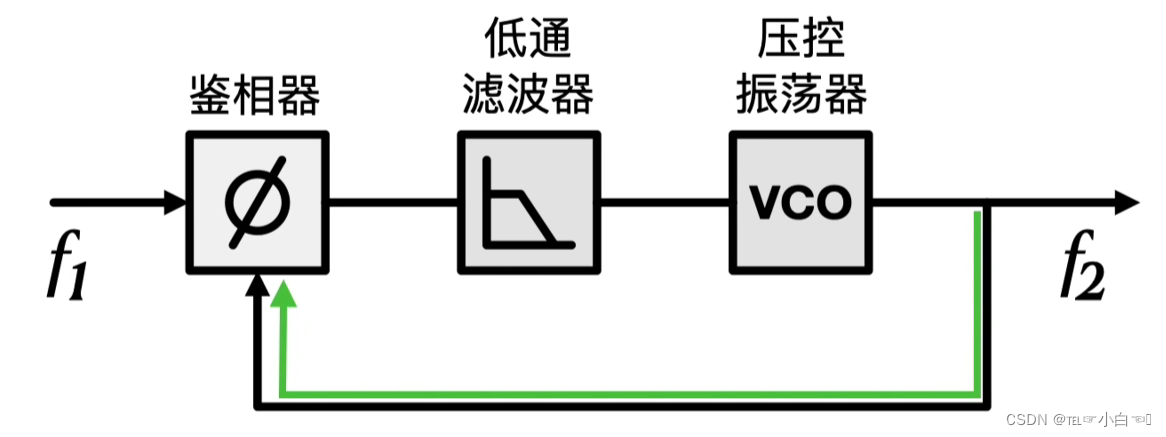

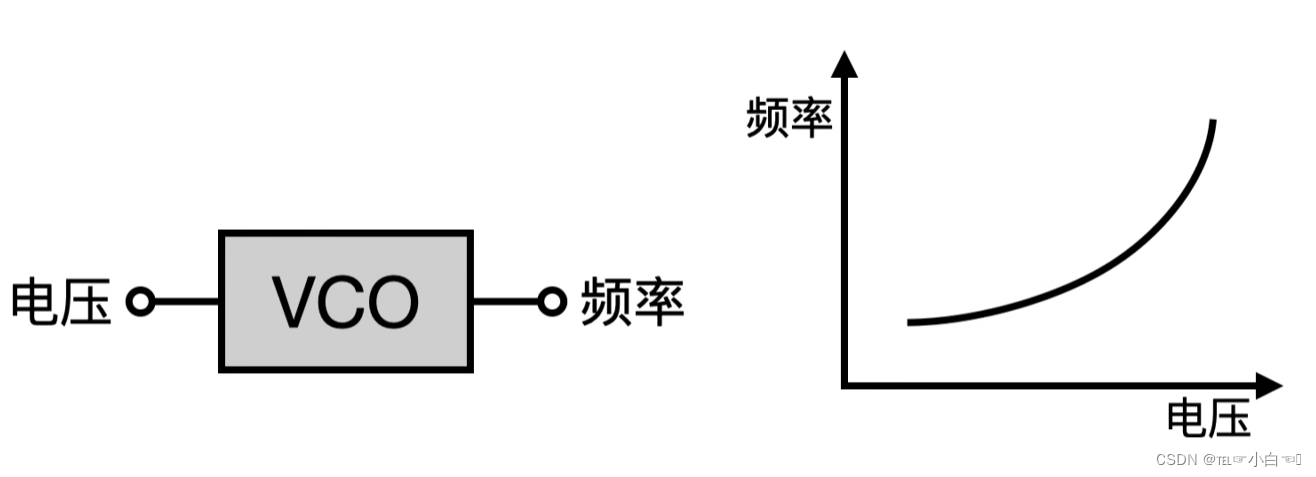

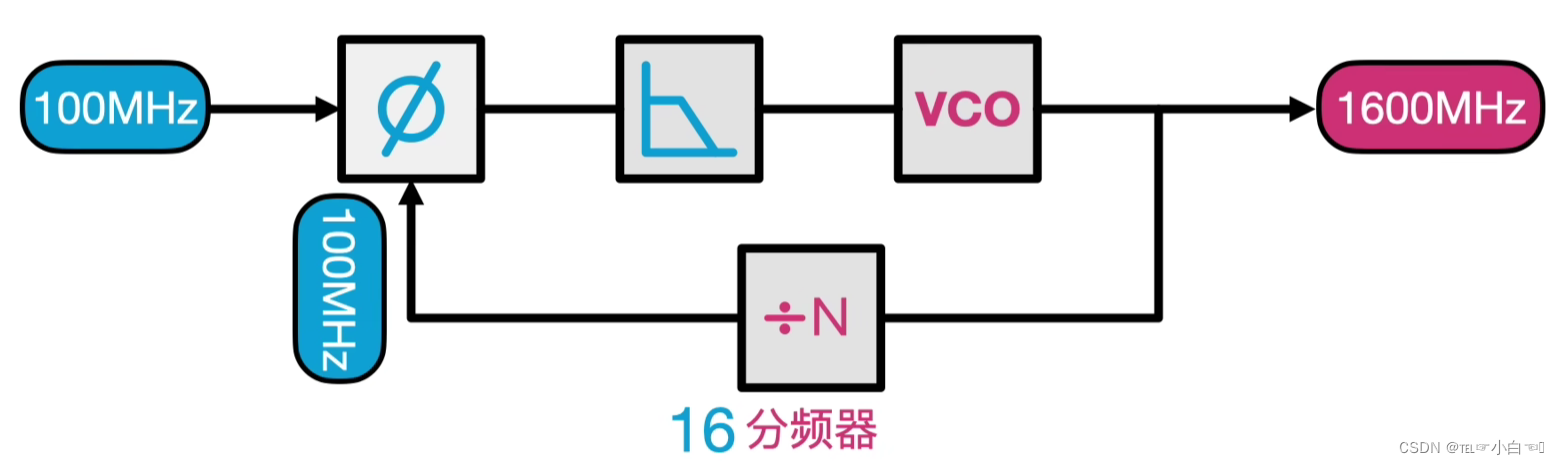

锁相环(Phase-Locked Loop,PLL),是一个能够比较输出与输入相位差的反馈系统,利用外部输入的参考信号控制环路内部振荡信号的频率和相位,使振荡信号同步至参考信号

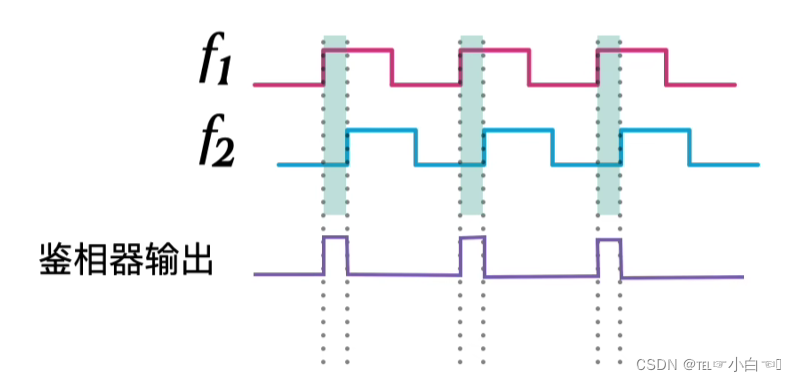

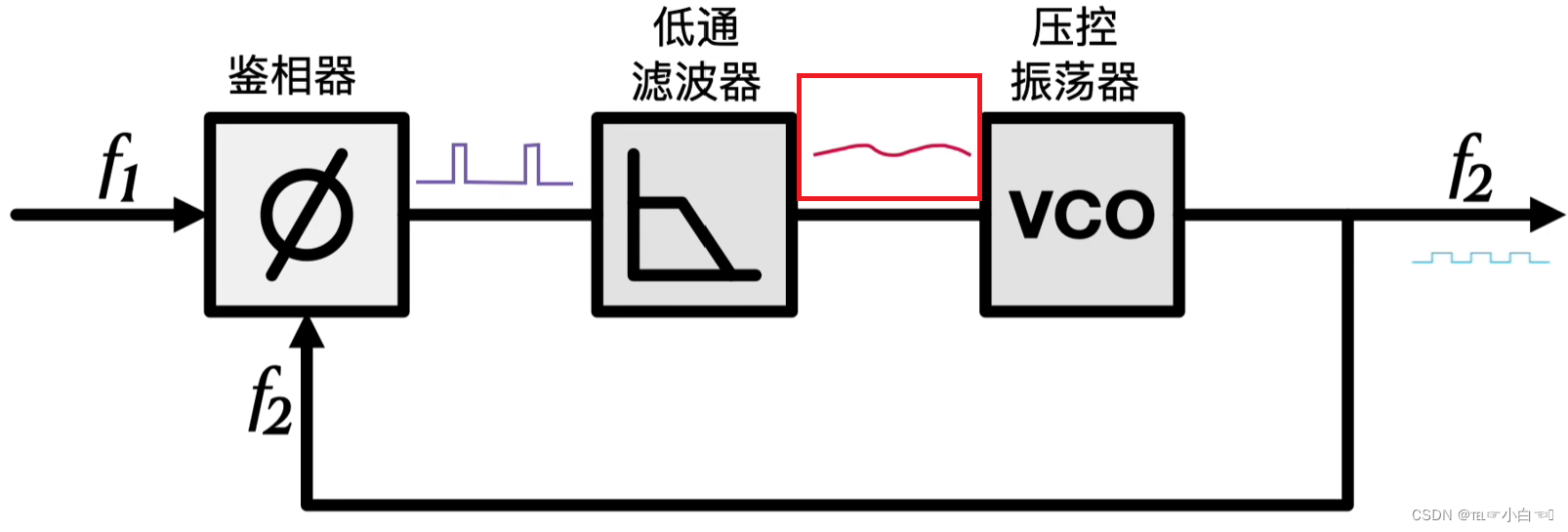

鉴相器有两个输入,分别是晶振信号的输入f1、VCO的输出f2,将两个信号进行比较,如果这两个信号存在相位差异或频率差异,则鉴相器就会在存在差异的这一段进行输出。鉴相器不停的调整输出的电压,使两个相位或频率快速保持一致

由于鉴相器输出的是矩形波,高低电平存在突变,低通滤波器可以让信号变得很平滑。输出的波形如下图所示

倍频,就是在回馈支路上加了一个分频器,经过鉴相器不停的调整输出的电压,使两个相位或频率快速保持一致

时钟树:

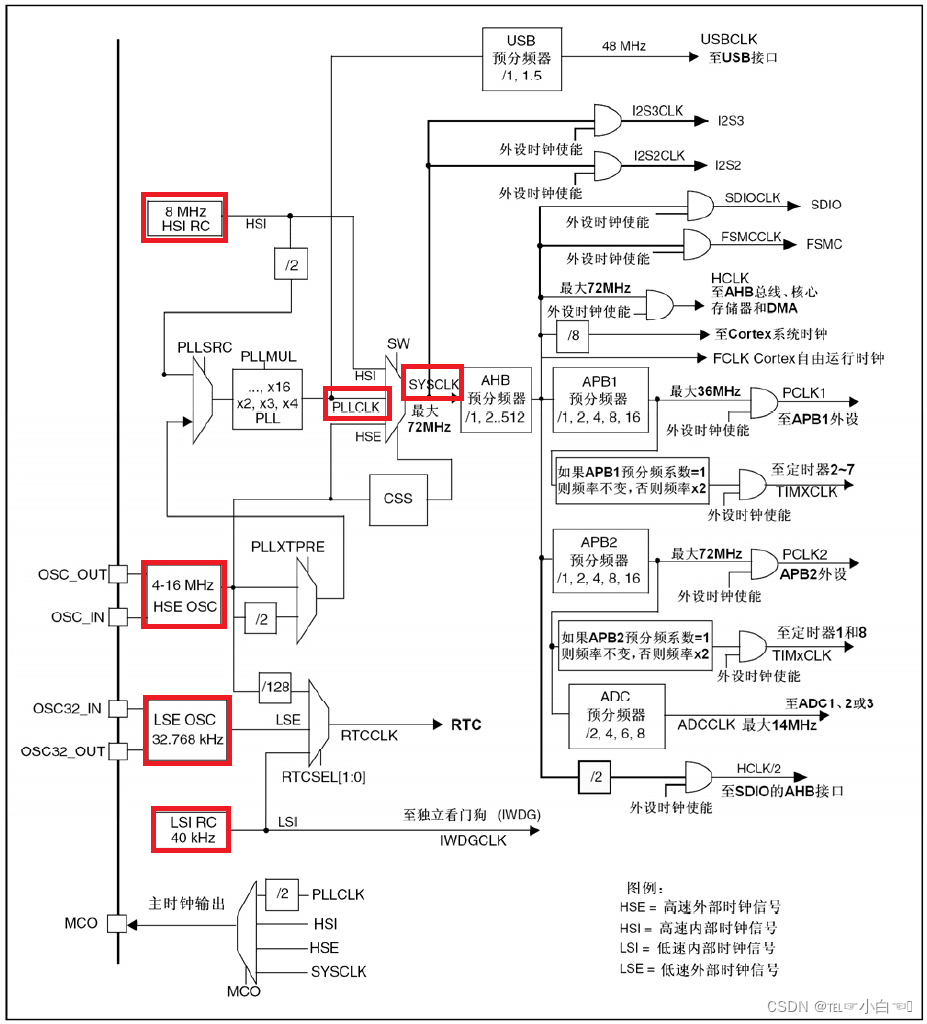

STM32F103单片机微处理器的神经中枢是时钟系统,时钟系统为整个硬件系统的各个模块提供时钟信号。由于各个外设对时钟信号有自己的要求,这就需要设置多个振荡器,分别提供时钟信号,或者从一个主振荡器开始经过多次倍频、分频、锁相环电路,生成各个模块的独立信号

片上外设在上电情况下默认是没有时钟信号的,此目的是降低功耗

在STM32中有5个时钟源,分别是HSI(High-Speed Internal Clock Sgnal)、HSE(High-Speed External Clock Sgnal)、LSI(Low-Speed Internal Clock Sgnal)、LSE(Low-Speed External Clock Sgnal)、PLL(Phase Locked Loop)

(1)HSI:高速内部时钟信号8MHz

通过8MHz的内部RC振荡器产生,并且直接可以用作系统时钟,或者经过2分频后作为PPL的输入

(2)HSE:高速外部时钟信号4~16MHz(一般接8MHz)

使用外部陶瓷/晶体振荡器产生。HSI比HSE有更快的启动速度,但频率精确度没有外部晶振高

(3)LSI:低速内部时钟信号30~60KHz

作为低功耗时钟源,可以在停机和待机模式下保持运行状态,为独立看门狗和自动唤醒单元提供时钟

(4)LSE:低速外部时钟信号32.768KHz

低速外部晶体/陶瓷振荡器,它为RTC或其他功能提供低功耗且精确的时钟源

(5)PLL:锁相环倍频输出

PLL用来倍频HSI或HSE,时钟输入源可选择HSI/2、HSE或HSE/2,倍频可选择2~16倍,但输出频率最大为72MHz

除此之外,STM32还具有系统时钟SYSCLK。SYSCLK为STM32中绝大部分部件工作提供时钟源。系统时钟可以选择PPL输出、HSI或HSE

CSS(Clock Security System):时钟安全系统。当外部时钟失效,自动把外部时钟切换到内部时钟,保障系统时钟的运行

启动文件在完成复位后跳转到main()之前调用system_stm32f10x.c中的SystemInit()用来初始化系统时钟(系统时钟源、PLL倍频因子、AHB/APBx的预分频及其Flash)

647

647

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?