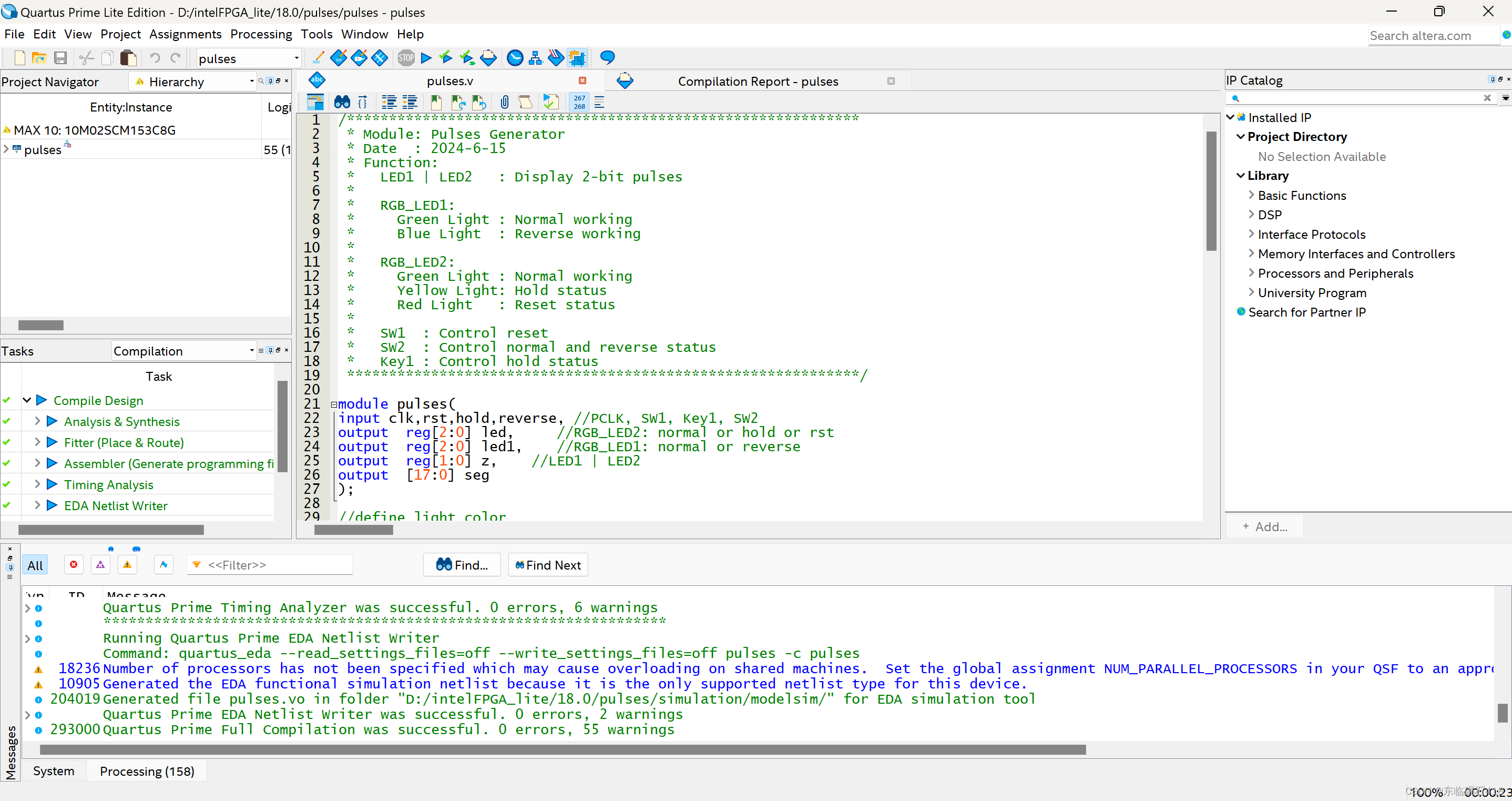

开发环境:Quartus Prime 18.0

设备:小脚丫开发板,搭载AlteraMAX10 10M02SCM153C8G

语言:verilog HDL

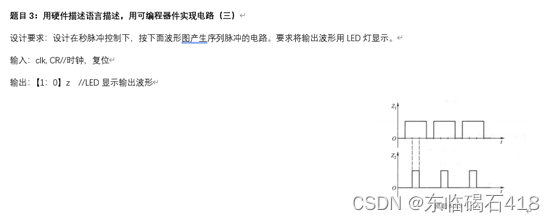

程序效果:

基本功能完成情况

(1)实现了2bit目标脉冲波形的输出

(2)实现了清零的功能

扩展功能完成情况

(1)实现了目标序列脉冲的反相输出,以及暂停保持的功能

(2)采用两颗RGB LED展示状态信息

主程序代码:

/*************************************************************

* Module: Pulses Generator

* Date : 2024-6-15

* Function:

* LED1 | LED2 : Display 2-bit pulses

*

* RGB_LED1:

* Green Light : Normal working

* Blue Light : Reverse working

*

* RGB_LED2:

* Green Light : Normal working

* Yellow Light: Hold status

* Red Light : Reset status

*

* SW1 : Control reset

* SW2 : Control normal and reverse status

* Key1 : Control hold status

*************************************************************/

module pulses(

input clk,rst,hold,reverse, //PCLK, SW1, Key1, SW2

output reg[2:0] led, //RGB_LED2: normal or hold or rst

output reg[2:0] led1, //RGB_LED1: normal or reverse

output reg[1:0] z, //LED1 | LED2

output [17:0] seg

);

//define light color

parameter GREEN =3'b101,

BLUE =3'b110,

RED =3'b011,

YELLOW=3'b001;

//divider: pluse of 1s

reg VDD;

initial VDD=1;

divider #(.N(6000000),.WIDTH(24))divider1(

.clk(clk),

.rst(VDD),

.clk_out(clk1)

);

//segment: show group No.: 30

reg [7:0]group_num;

segment7 high(.A(group_num[7:4]),.g_to_a(seg[17:9]));

segment7 low(.A(group_num[3:0]),.g_to_a(seg[8:0]));

//pulses generator

wire [1:0]zp; //POSITIVE

wire [1:0]zn; //NEGATIVE

reg [2:0]state;

parameter S0=3'b000,

S1=3'b010,

S2=3'b111,

S3=3'b110;

always@(posedge clk1,negedge rst, negedge hold)

begin

group_num<=8'b0011_0000; //BCD code: group No.30

//reset

if(!rst) begin state<=S0;led<=RED; end

//hold

else if(!hold) begin state<=state;led<=YELLOW; end

//normal working

else

begin

led<=GREEN;

case(state)

S0: state<=S1;

S1: state<=S2;

S2: state<=S3;

S3: state<=S0;

endcase

end

end

assign zp=~state[1:0];

assign zn=state[1:0];

//selector: zp or zn

always @(reverse)

begin

if(!reverse) begin z=zn;led1=BLUE; end

else begin z=zp;led1=GREEN; end

end

endmodule

子模块 1:分频器

module divider(

inout clk,

input rst,

output reg clk_out

);

parameter N=6000000,WIDTH=24;

reg [WIDTH-1:0] cnt;

always @(posedge(clk),posedge(rst))

begin

if(rst==1'b1)

cnt<=24'b0;

else if(cnt==N-1)

cnt<=24'b0;

else

cnt<=cnt+1;

end

always @(posedge(clk),posedge(rst))

begin

if(rst==1'b1)

clk_out<=1'b0;

else if(cnt==N-1)

clk_out<=~clk_out;

else

clk_out<=clk_out;

end

endmodule

子模块2:数码管

module segment7(

input wire [3:0] A,

output wire [8:0] g_to_a

);

reg [8:0] seg[15:0];

initial

begin

seg[4'b0000]=9'h3f;

seg[4'b0001]=9'h06;

seg[4'b0010]=9'h5b;

seg[4'b0011]=9'h4f;

seg[4'b0100]=9'h66;

seg[4'b0101]=9'h6d;

seg[4'b0110]=9'h7d;

seg[4'b0111]=9'h07;

seg[4'b1000]=9'h7f;

seg[4'b1001]=9'h6f;

seg[4'b1010]=9'h77;

seg[4'b1011]=9'h7c;

seg[4'b1100]=9'h39;

seg[4'b1101]=9'h5e;

seg[4'b1110]=9'h79;

seg[4'b1111]=9'h71;

end

assign g_to_a = seg[A];

endmodule

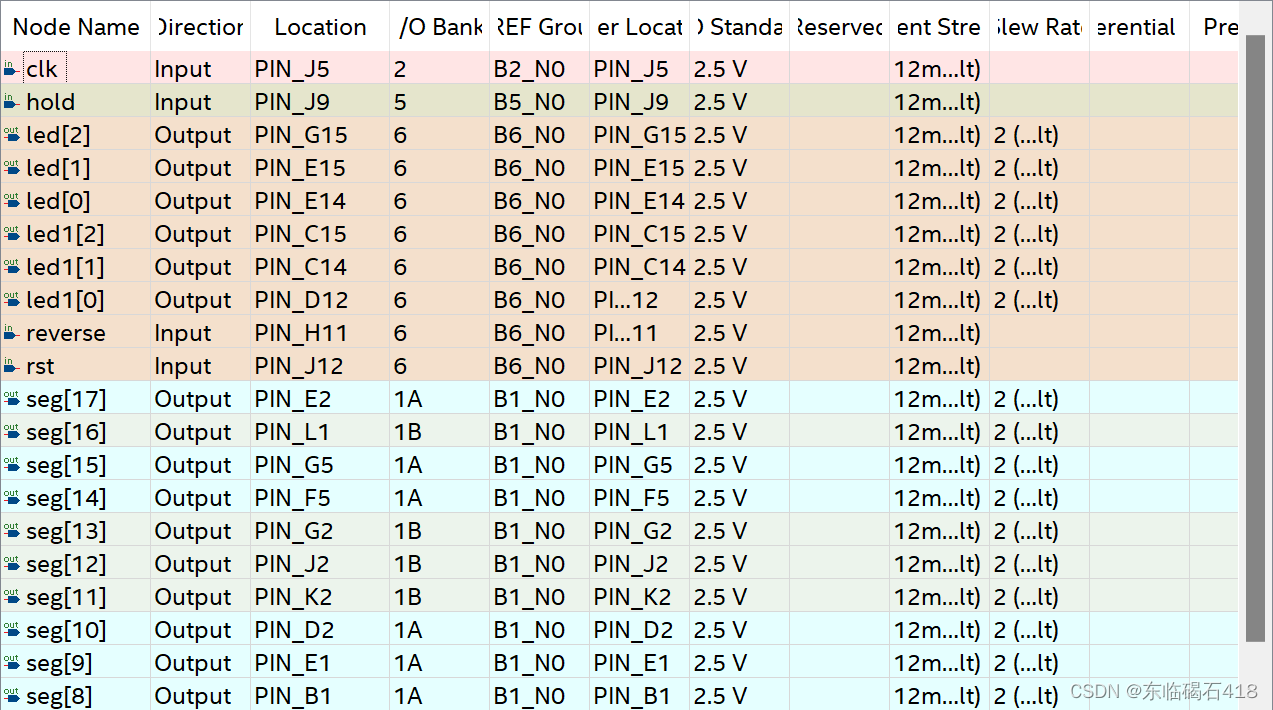

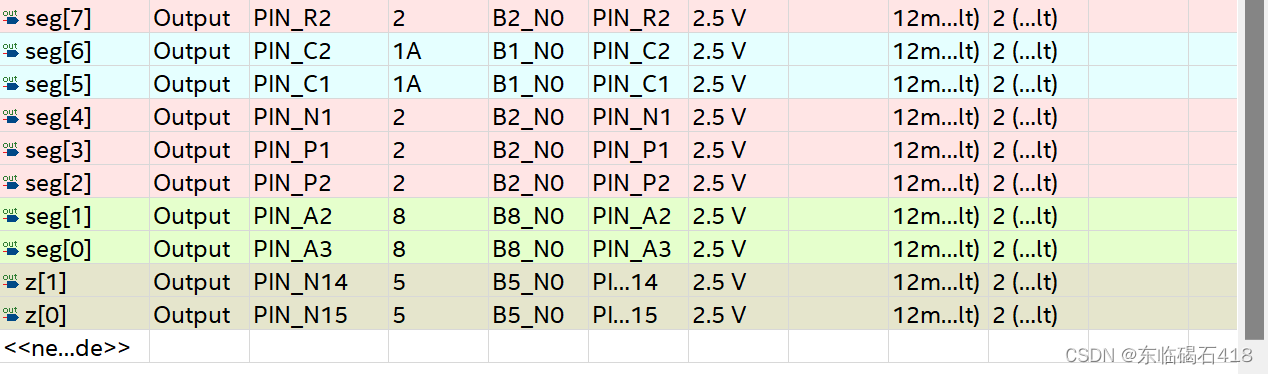

管脚分配:

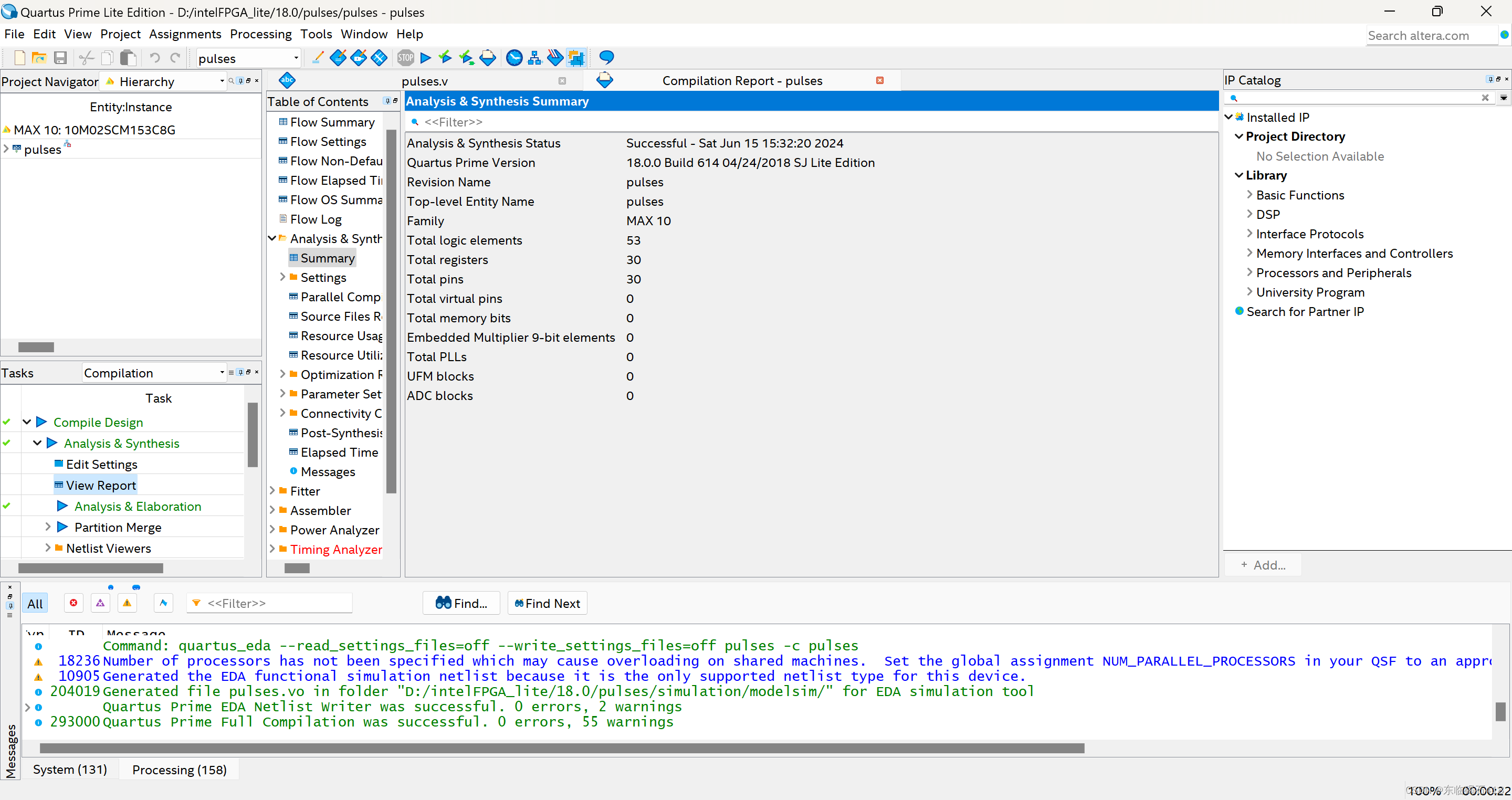

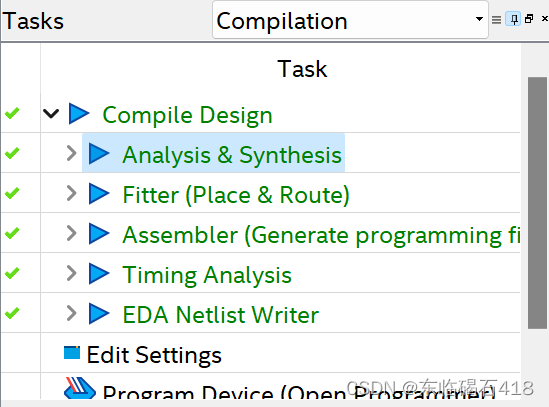

Analysis&Synthesis成功:

Compile Design成功:

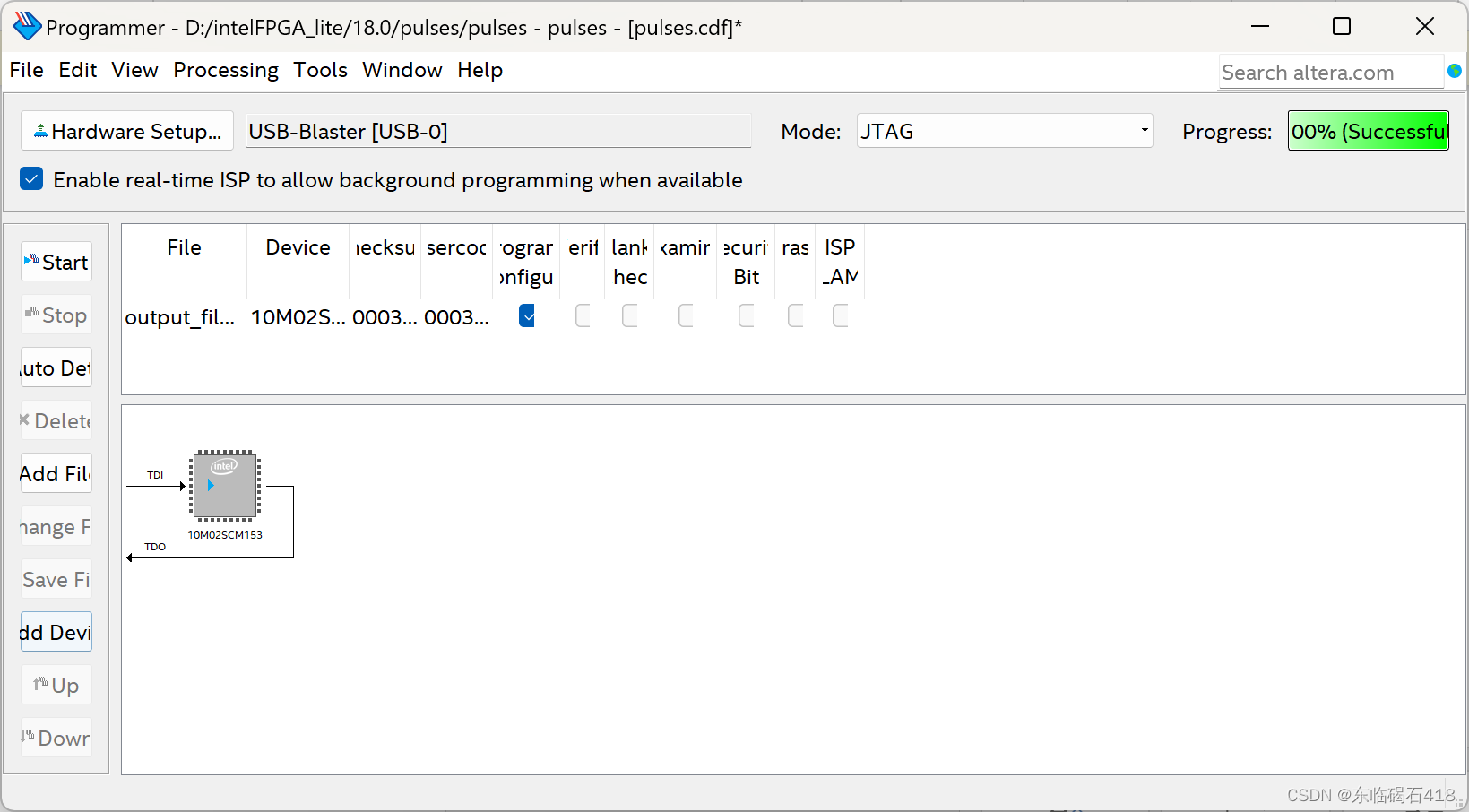

programmer成功:

视频展示:

FPGA序列脉冲波形发生器

2855

2855

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?