快速排序 实现原理

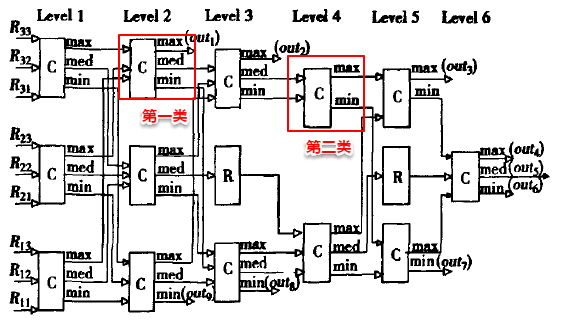

通过如下图所示的6级比较电路路输出中值,其输人数据为图1所示的滤波掩膜所在的图像数据。第一级比较电路由3个三输入比较器C组成,每个比较器的输出数据依序排列(参见图示)。将3组比较结果中最小的3个数放在一起、中间的3个数放在一起、最大的3个数放在一起,参加第二级比较。第二级比较电路的原理与第一级类似,输出out1和out9,分别是输入数据中的最大值和最小值,这2个数据将被舍去不参加下一级比较。参加第三级比较的有7个数据,其原理类似于前两级比较电路,输出out2和out8分别是该7个数据的最大值和最小值,并且被舍去,仅留下5个数据参加第四级比较。剩下的几级比较电路以类似于先前的原理进行比较。如此,经过6级比较后即可得到9个数据的标准中值滤波输出值out5,而outl,out2,⋯,out9分别是这9个数据从最大到最小的顺序排列值。此外。为了保证流水线操作过程中数据的同步性,在第三级和第五级比较电路中需要插入数据寄存器R缓存当前该级中不参与比较的数据。

快速中值输出

第一步:将每一行按最大值、中间值、最小值排列

第二步:提取出最大值的最小值,中间值的中间值,最小值的最大值

第三步:将第二步提取出来的三个数进行排序,中间值即我们要求的中间值。

4096

4096

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?