使用CIC滤波器用于降采样。同样的,CIC滤波器也适用于升采样。

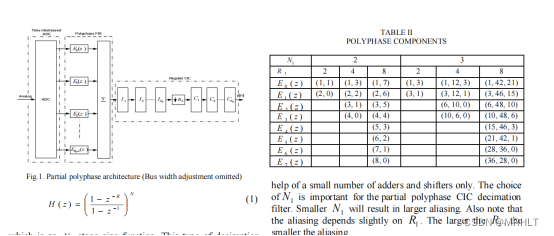

考虑到ADC采样率高达1Gsps以上,在FPAG实现CIC内插滤波器必须并行处理,并行处理结果如下图所示:

clc

close all

clear all

% fs=50e6;

% fc=1e6;

% LEN = 1E5;

% n=0:LEN-1;

% x = sin(2*pi*fc/fs*n);

fame = 10;

%% 生成bit数据

len = 1e3;

msg_data = randi([0 1],len,1); % 生成bit信号

Order_number = 6; %m序列的阶数等于7

msg_head = (idinput((2^(Order_number)-1),'prbs')' + 1)/2;%生成m序列

% msg = [msg_head msg_data.'];

% save msg.mat msg

load msg.mat

msg= msg(1:length(msg_head)+len);

tx_mod =1i*(1-2*msg); %% Bpsk调制

figure(1)

plot(tx_mod,'.r')

%%

tx_mod_r = repmat(tx_mod,1,fame); %% 重复帧数

%% 生产FPGA仿真数据

input = tx_mod_r.*2^14;

output = Gen_TxT(input);

%%

sync_head = tx_mod_r(1:length(msg_head));

figure(2)

plot(imag(sync_head ))

title('帧头时域')

conj_head_r = fix(real(conj((2^6)*sync_head(end:-1:1))));

conj_head_i = fix(imag(conj((2^6)*sync_head(end:-1:1))));

h_coe = conj_head_r + 1i*conj_head_i;

%% 16倍上采样

I = 16;

[y_serial,y_para] = cic_interp_func(input,I);

figure(3)

plot(real(y_serial(1:1e3)));hold on

plot(imag(y_serial(1:1e3)),'-r');hold off;

title('上采样后时域')

%%

% load CIC_outI0.txt

% load CIC_outQ0.txt

% rx_data = CIC_outI0.'+1i*CIC_outQ0.';

data_input = y_para(1,:);

[y_out,power] = xcorr_func(data_input,h_coe) ;

figure

plot( (power))

title('FPGA同步峰值')

%% 帧同步

head = sync_head.*2^6;

sync_thr = 2000;

for kk=1:I

rx_data = y_para(kk,:);

[output,sync_peak,start_index,max_peak(kk) ] = func_sync_fix(rx_data,head,sync_thr);

figure

plot(abs(sync_peak))

title('FPGA同步峰值')

kk

end

figure(55)

plot( (max_peak));grid on;

title('不同抽样同步峰值')

实测并行matlab仿真和串行仿真结果一致。并行CIC内插和并行CIC上采样滤波器FPGA实现如下:

如需matlab仿真和FPGA实现可私信。

560

560

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?