在宽带通信系统中, ADC/DAC的采样率 一般都在 1GSa/sec以上,而 FPGA的处理时钟一 般在 250MHz以下, 要完成实时信号处理技术,引入多相、并行处理技术。 我们以经典的 FIR滤波器为例:

FPGA不同并行度实现结构:

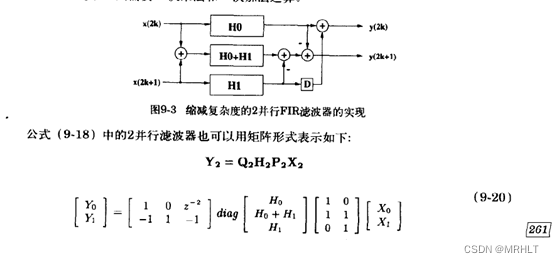

2并行FFA

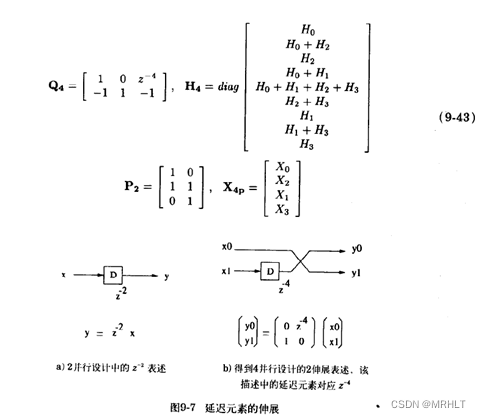

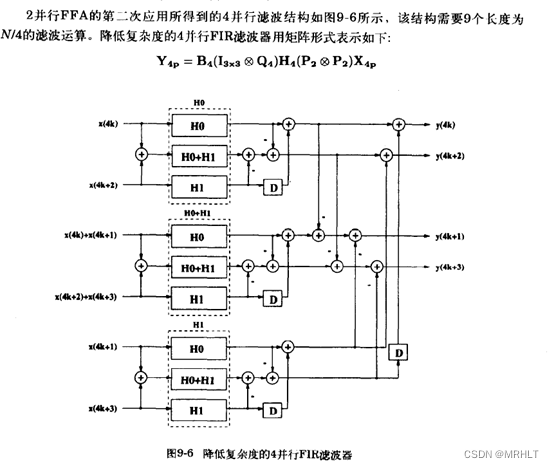

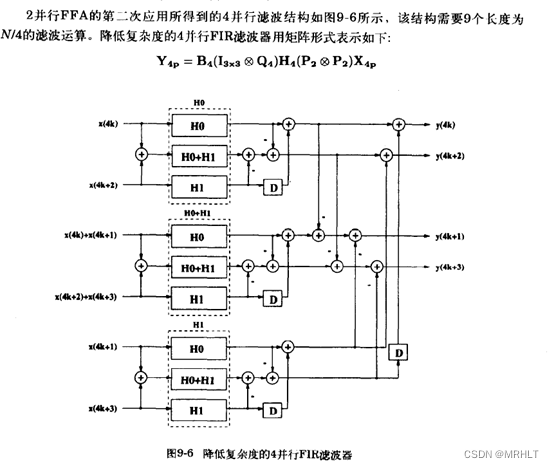

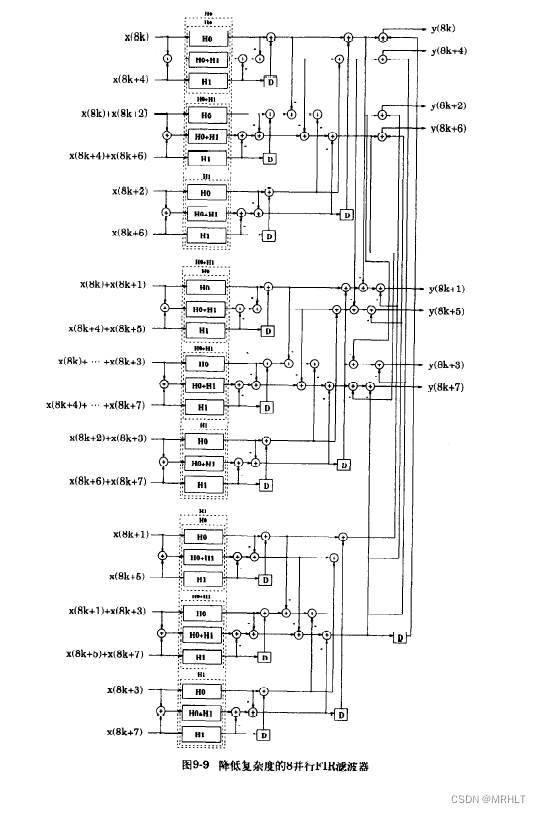

2、4并行FFA

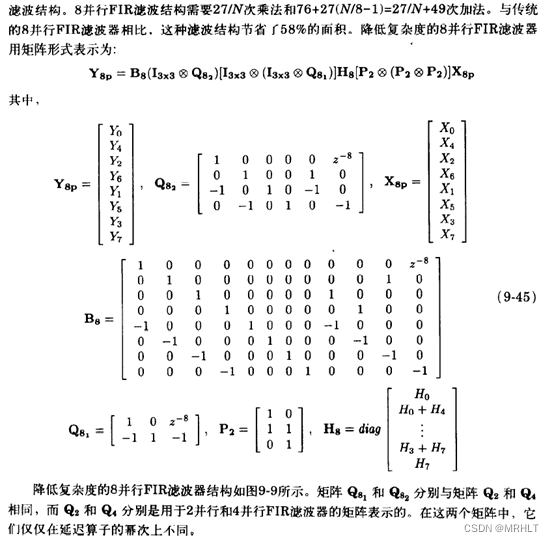

3、8并行FFA

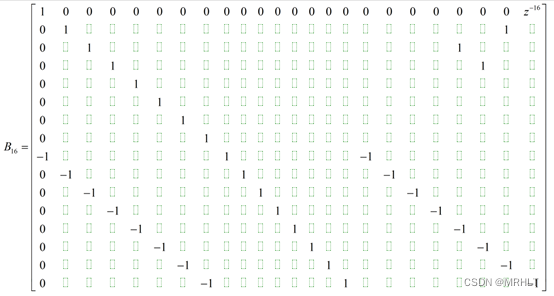

4、16并行FFA

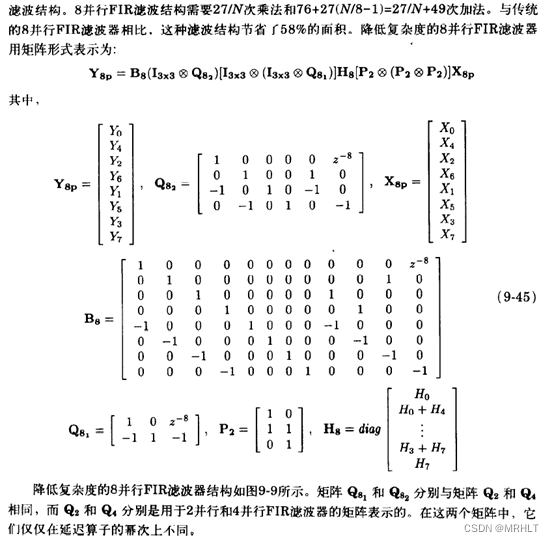

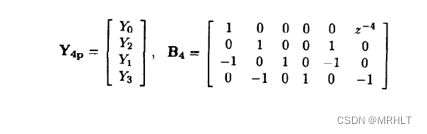

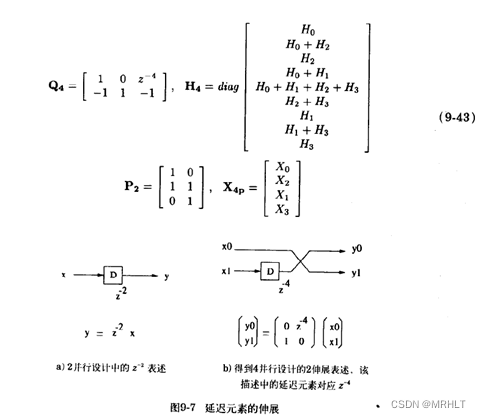

其中:

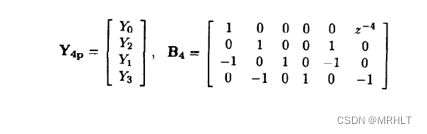

其中:

,

,

备注:空白处元素为0

如需matlab和FPGA代码可私信或+q2319108424。

在宽带通信系统中, ADC/DAC的采样率 一般都在 1GSa/sec以上,而 FPGA的处理时钟一 般在 250MHz以下, 要完成实时信号处理技术,引入多相、并行处理技术。 我们以经典的 FIR滤波器为例:

FPGA不同并行度实现结构:

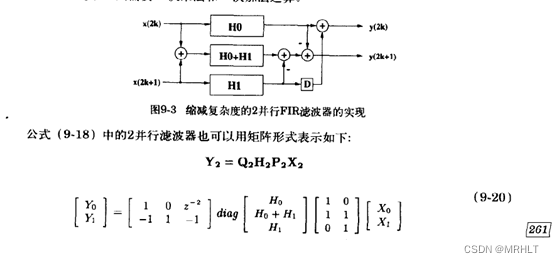

2并行FFA

2、4并行FFA

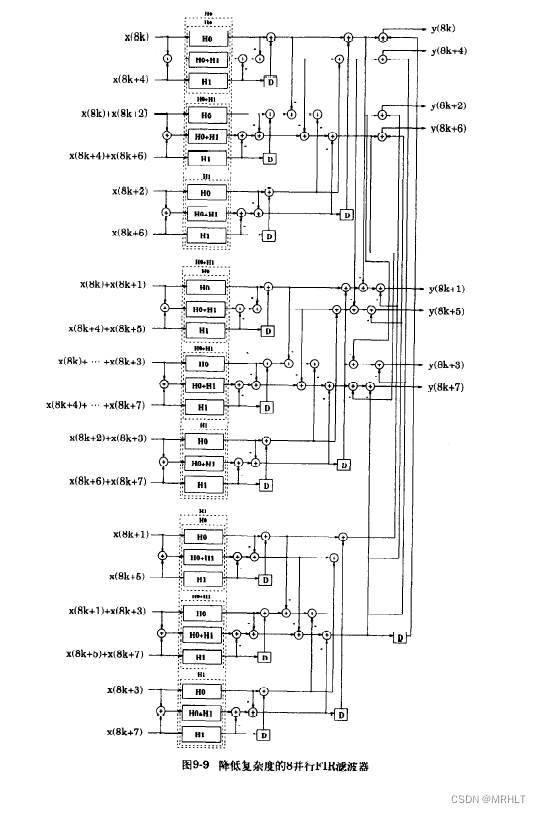

3、8并行FFA

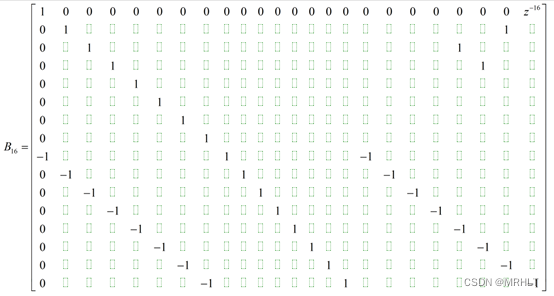

4、16并行FFA

其中:

其中:

,

,

备注:空白处元素为0

如需matlab和FPGA代码可私信或+q2319108424。

5451

5451

1466

1466

882

882

495

495

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?