逻辑移位

逻辑移位的操作符为右移(>>)高位不够的bit位补0。左移(<<),低位补0。

算术移位

算术以为呃的操作符为右移动(>>>)高位用呼号位补。左移(<<<),低位补0。

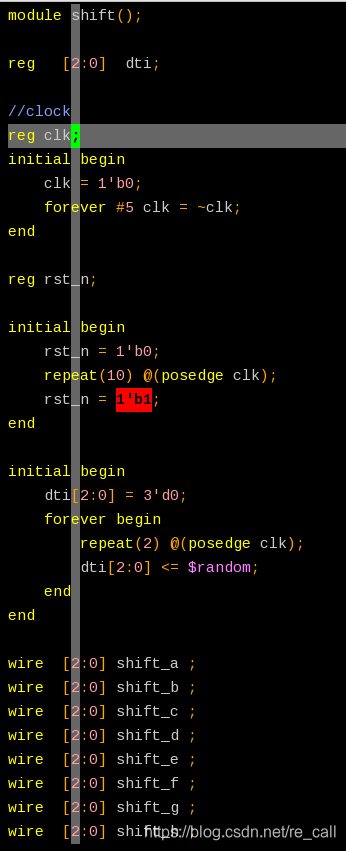

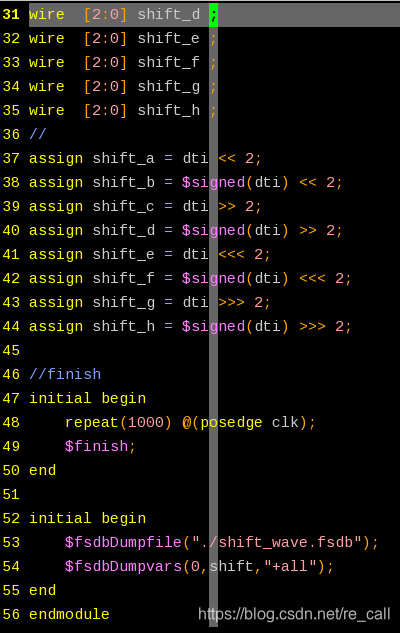

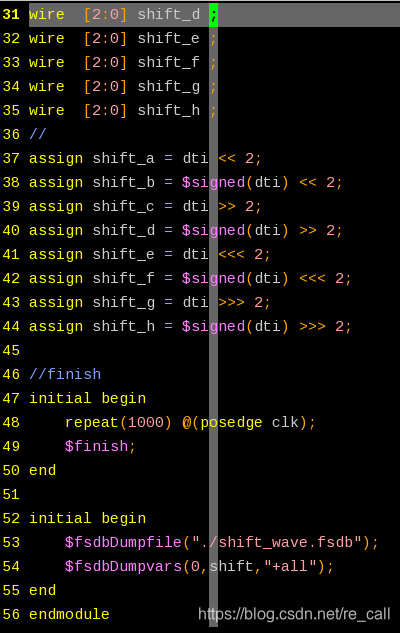

实例

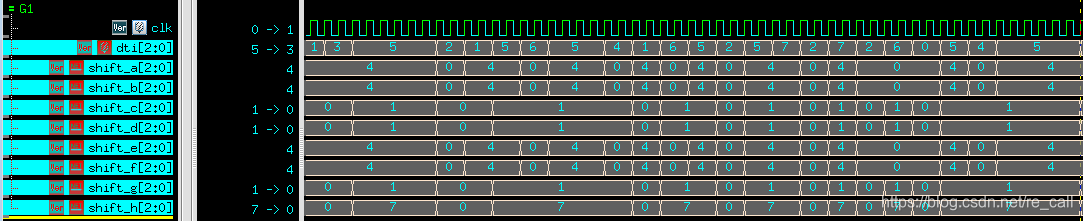

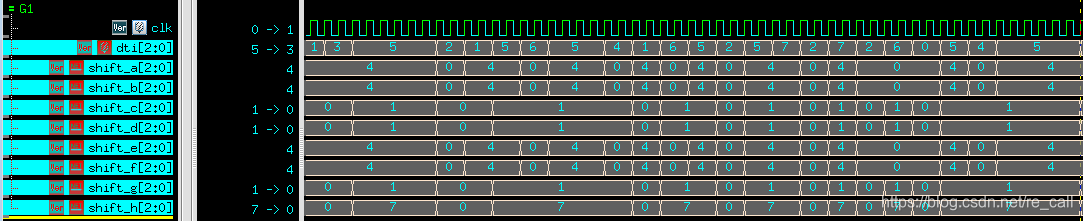

仿真结果

结论

对于无符号数,逻辑移位和算术移位结果是一样的。

对于有符号数,逻辑右移和算术右移是不一样的。算术右移时,高位需要用符号位补。

逻辑移位

逻辑移位的操作符为右移(>>)高位不够的bit位补0。左移(<<),低位补0。

算术移位

算术以为呃的操作符为右移动(>>>)高位用呼号位补。左移(<<<),低位补0。

实例

仿真结果

结论

对于无符号数,逻辑移位和算术移位结果是一样的。

对于有符号数,逻辑右移和算术右移是不一样的。算术右移时,高位需要用符号位补。

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?